虽然Verilog硬件描述语言有很完整的语法结构和系统,这些语法结构的应用给设计描述带来很多方便。但是Verilog是描述硬件电路的,它是建立在硬件电路的基础上。有些语法结构是不能与实际硬件电弧对应起来的,比如for循环,它是不能映射实际的硬件电路的,因此,Verilog硬件描述语言分为可综合和不可综合语言。

1. 所谓可综合,就是我们编写的Verilog代码能够被综合器转化为相应的电路结构。因此我们常用可综合语句来描述数字硬件电路。

2. 所谓不可综合,就是我们编写的Verilog代码无法综合生成实际的电路。因此,不可综合语句一般我们在描述数字硬件电路时是用不到的,不过,我们可以用它来仿真、验证我们描述的数字硬件电路。

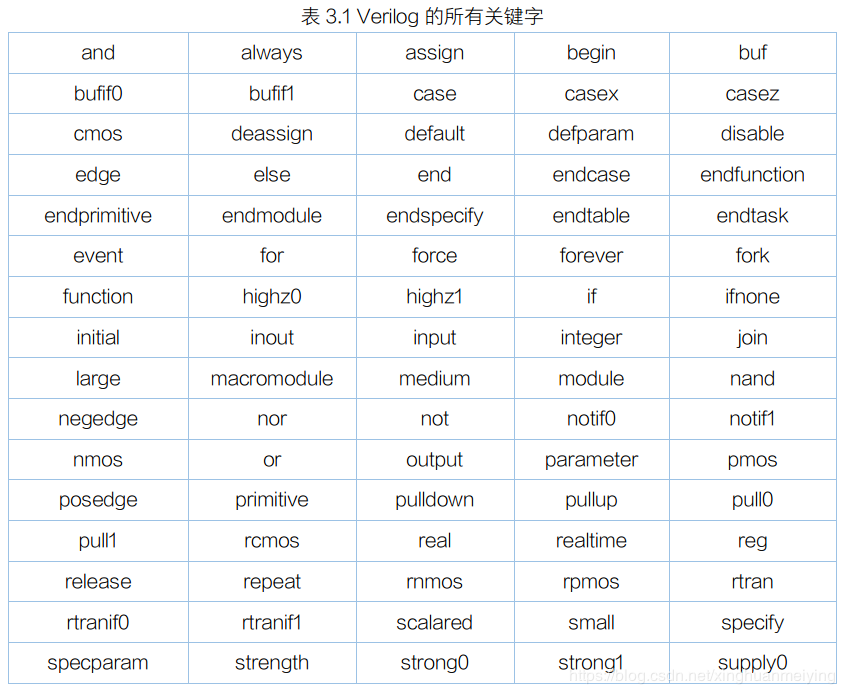

1. Verilog的关键字

下面给出Verilog的所有关键字,如下表所示。

看到这么多关键字,一定会被吓到,毕竟C语言也才不过32个关键字。其实在这里大家并不需要为此担心,前面我们说过,Verilog分为可综合和不可综合语句,由于我们是将Verilog用于描述数字硬件电路,所以我们只需要掌握可以被综合器综合的那部分关键字就可以了。

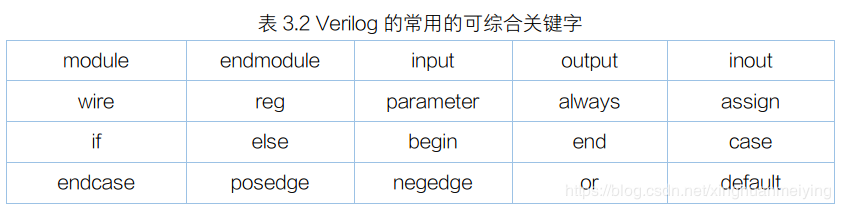

下面列出常用的可综合关键字:

2. Verilog的基本程序框架

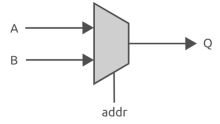

学习C语言时,首先接触到的第一个程序就是“Hello World”。既然Verilog是一种用于数字逻辑电路设计的语言,那么我们就以数字电路中最简单的与门为例,来作为入门学习的第一个程序。

module AndGate(a, b, c)

input a;

input b;

output c;

assign c = a & b;

endmodule 通过上面使用Verilog描述的与门程序,总结以下的基本程序架构:

- Verilog HDL 程序是由模块构成的,每个模块的内容都是嵌在 module 和 endmodule两个语句之间。

- 每个模块都要进行端口定义,并说明输入输出口,然后对模块的功能进行行为逻辑描述。

- Verilog HDL 程序的书写格式自由,一行可以写几个语句,一个语句也可以分写多行。

- 除了 endmodule 语句外,每个语句和数据定义的最后必须有分号。

版权声明:本文为CSDN博主「智小星」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/xinghuanmeiying/article/details/101022071