基于SRAM技术的Xilinx FPGA具有较高的逻辑密度,消耗较高功率。

基于闪存技术的Xilinx CPLD具有较低的逻辑密度,功耗也比较低。为了提高逻辑密度、集成更多功能,PLD厂商的每一代器件都会采用当前最新的工艺技术。不同的功能需求以及集成工艺,使得PLD的供电电压有所不同。

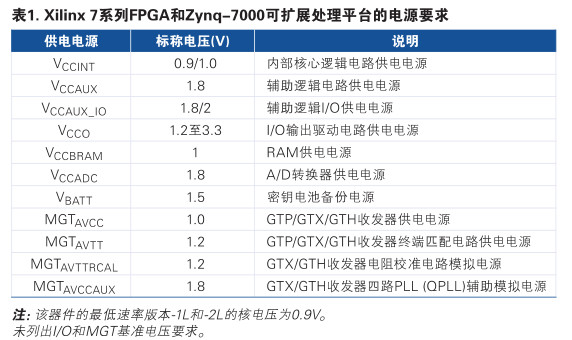

由于PLD在电路板上担当的角色是一个片上系统(SOC),为这些器件供电就相当于为整个系统供电。典型的高端Virtex系列FPGA可能需要10~15路独立的供电电压。另一方面,较低密度的Spantan、Kintex、Artix和CoolRunner系列器件会需要2~10路独立的供电电压。用户需要根据每路电压的功率要求、供电顺序以及系统电源管理的需求,确定正确的稳压电源组合。

现代PLD的核电源为内部多数电路供电,所消耗的功率也最高。每一次新工艺的出现,都会产生新的核电源要求。支持PLD辅助电路的核电电源用于配置逻辑电路、时钟管理以及其他辅助功能电路。此外,FPGA往往把一个接口标准桥接到另一接口标准,每个IO也会具有不同的电源要求求,范围从1.2V至3.3V。

另外,特别需要注意告诉SerDes收发器的供电电源,每个收发器可能消耗1至几个安培的电流,收发器速率为155Mbps至28Gbps,甚至更高。例如100G以太网系统中使用多个这样的收发器,电流损耗为10A,甚至更高。高速数据传输会在电源总线产生较大的噪声,对电源的性能影响较大。

本文转自:瓜大三哥,作者:米果不回来,转载此文目的在于传递更多信息,版权归原作者所有。