作者:,来源:FPGA开源工作室

1 基本概念与应用

1)LFSR:线性反馈移位寄存器(linear feedback shift register, LFSR)是指给定前一状态的输出,将该输出的线性函数再用作输入的移位寄存器。异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

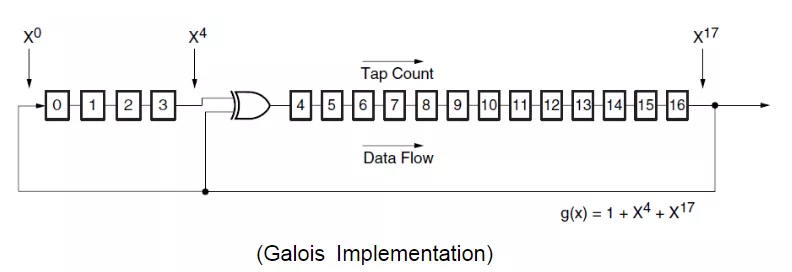

LFSR产生的两种形式为伽罗瓦(Galois)和斐波那契(Fibonacci)两种形式。也有成为外部(External)执行方式和内部(Internal)执行方式。

(1)伽罗瓦方式(Internal)

Galois方式特征数据的方向从左至右,反馈线路是从右至左。其中X -0 项(本原多项式里面的‘1’这一项)作为起始项。按照本原多项式的指示确定异或门(XOR)在移位寄存器电路上的位置。如上图所示X -4 。因此Galois方式也有人称作线内或模类型(M-型)LFSR。

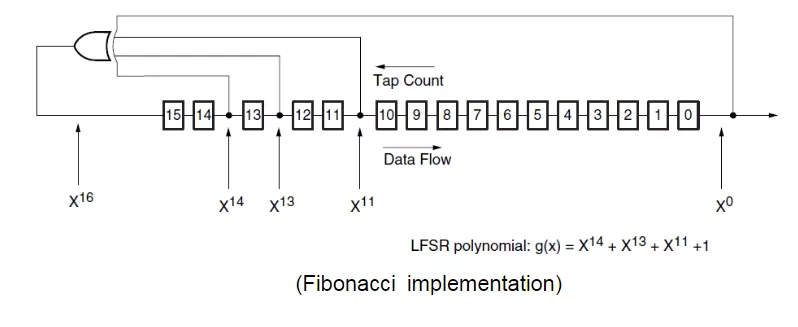

(2)斐波那契方式(External)

从图中我们可以看到Fibonacci方式的数学流向和反馈形式是恰好跟Galois方式相反的,按照本原多项式,其中X -0 这一项作为最后一项,这里需要一个XOR门,将本原多项式中所给的taps来设定它的异或方式。因此Fibonacci方式也被叫做线外或者简型(S-型)LFSR。

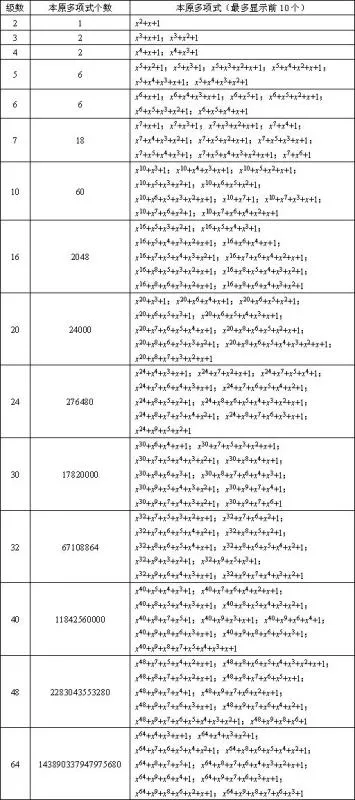

2)本原多项式

本原多项式是近世代数中的一个概念,是唯一分解整环上满足所有系数的最大公因数为1的多项式。本原多项式不等于零,与本原多项式相伴的多项式仍为本原多项式。

(1)在MATLAB中,本原多项式可以通过函数primpoly(x)来产生。

(2)在MATLAB中,通过函数gfprimfd(m,'min')可以找到一个最小的本原多项式。

3)应用

误码率测量--在数字通信中误码率是一项重要的质量指标,在实际测量数字通信系统的误码率时,一般来说,测量结果与信源发出信号的统计特性有关。通常认为二进制信号0和1是以等概率随机出现的。所以测量误码率时最理想的信源应是伪随机序列产生器。这样测量的结果,我们认为是符合实际运用时的情况。

时延测量--有时我们需要测量信号经过某一传输路径所收到的时间延迟,例如,需要测量某一延迟线的时间延迟。另外,我们还常常通过测量一无线电信号在某个媒质中的传播时间,从而折算传播距离,即利用无线电信号测距。这就是说,这种测距的原理实质上也是测量延迟。

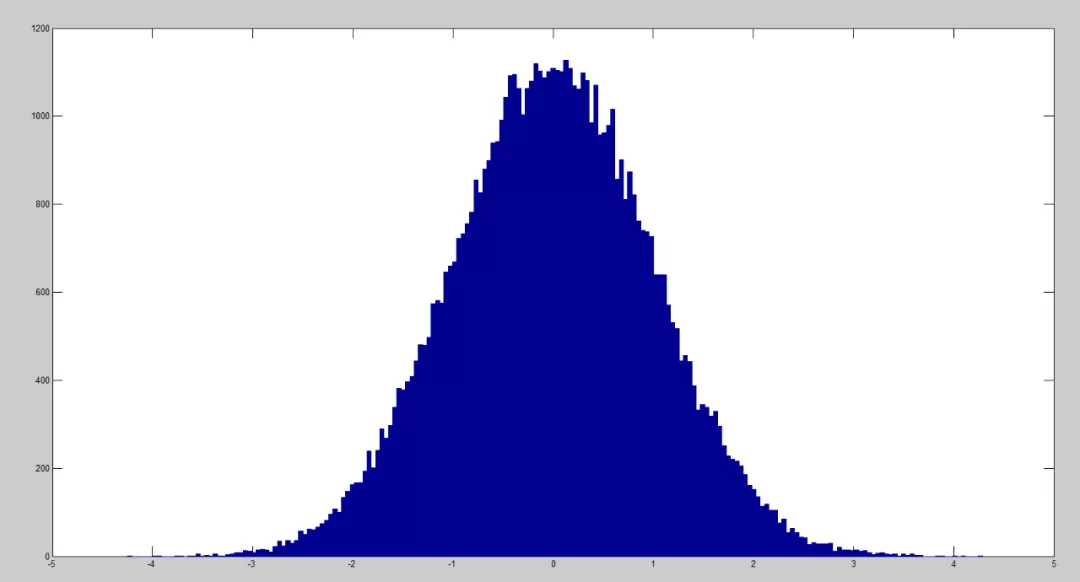

噪声产生器--测量通信系统的性能时,常常要使用噪声产生器,由它给出具有所要求的统计特性和频率特性的噪声,并且可以随意控制其强度,以便得到不同信噪比条件下的系统性能。例如,在许多情况下,要求它能产生限带白色高斯噪声。

通信加密、数据序列的加扰与解扰、扩展频谱通信、分离多径技术等等。

2伪随机序列的原理

对于某种反馈逻辑、初始化状态非全零时,若输出序列周期最长(P=2r-1),称为m序列,也称为伪随机序列。

伪随机序列通常由反馈移位寄存器产生,又可分为线性反馈移位寄存器和非线性反馈移位寄存器两类。由线性反馈移位寄存器产生出的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器,即为通常说的m序列,因其理论成熟,实现简单,应用较为广泛。下面介绍m序列的产生原理。

在二进制多级移位寄存器中,若线性反馈移位寄存器(LFSR)有n 阶(即有n级寄存器),则所能产生的最大长度的码序列为2n-1位。如果数字信号直接取自LFSR(非翻转信号)的输出,那么最长的连0数为n-1。除了字符串的连0和连1,伪随机序列在一个长度为n的字符串中将包含任何可能的0和1的组合。要使移位寄存器产生确定的值,必须置其初值并允许时钟电路产生移位时钟。

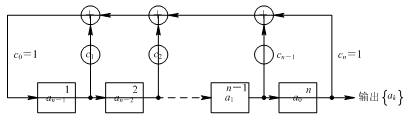

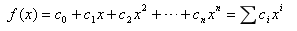

线性反馈移位寄存器产生m序列

在图中给出一个一般的线性反馈移位寄存器的组成。图中一级移存器的状态用表示,=0或1,i=整数。反馈线的连接状态用 表示,=1表示此线接通(参加反馈),=0表示此线断开。我们不难推想,反馈线的连接状态不同,就可能改变此移存器输出序列的周期p。

的取值决定了移存器的反馈连接和序列的结构,也就是决定了序列的周期。用特征多项式表示为:

当特征多项式符合某些条件时称为本原多项式。在设计m序列产生器时,移位寄存器反馈线的结构直接决定于本原多项式的结构。也就是只要找到本原多项式,就能由它构成m序列产生器。

3 matlab的LFSR验证

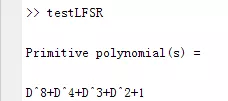

1)matlab函数产生本原多项式

clear all

close all

primpoly(8);

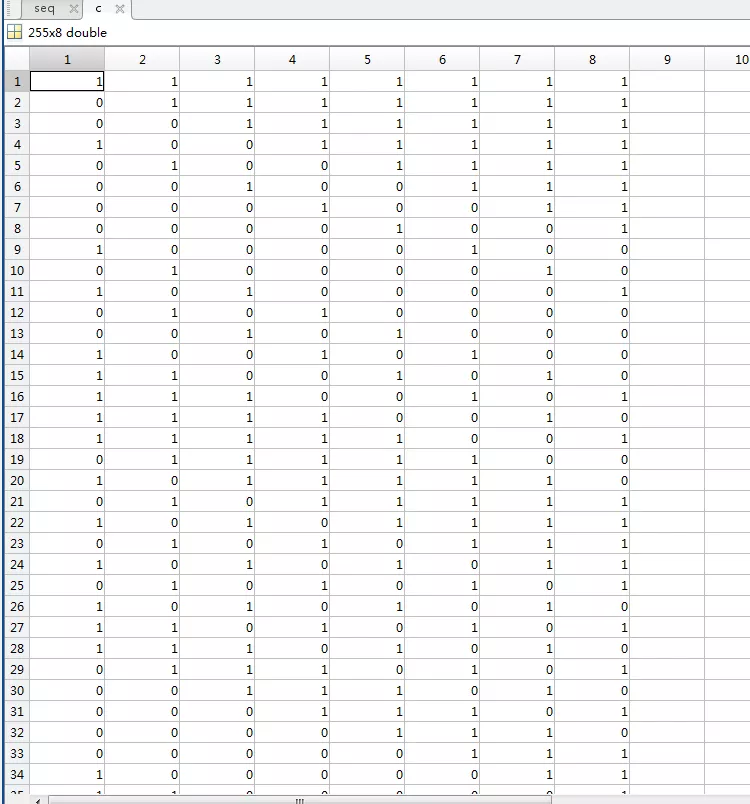

2)本原多项式产生随机序列

clear all

close all

% m=8

% x^8+x^4+x^3+x^2+1

% 435

s=[1 1 1 1 1 1 1 1];

t=[8 4 3 2];

[seq c]=LFSRv1(s,t);

4 FPGA的LSFR验证

1)fpga实现本原多项式

/*

m:x^8+x^4+x^3+x^2+1

*/

module msequence8#(

parameter seed= 8'b1111_1111

)(

clk,

rst_n,

en,

mse8, //m sequence

rand8

);

input clk, rst_n;

input en;

output mse8;

output reg [7:0] rand8;

assign mse8 = rand8[0];

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)

rand8 <= seed;

else if(en) begin

rand8[0] <= rand8[1];

rand8[1] <= rand8[2];

rand8[2] <= rand8[3];

rand8[3] <= rand8[4];

rand8[4] <= rand8[5];

rand8[5] <= rand8[6];

rand8[6] <= rand8[7];

rand8[7] <= rand8[0] ^ rand8[4] ^ rand8[5] ^ rand8[6];

end

else

rand8 <= rand8;

end

endmodule

如上图所示,当fpga仿真的输入种子和matlab的输入种子一致时产生的序列一致。

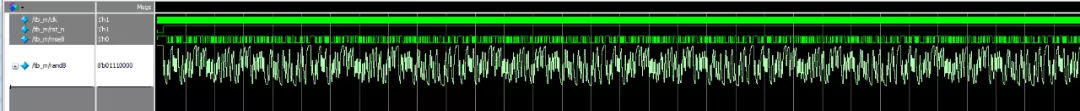

上图为随机序列的模拟信号展示。

3)在产生随机数序列的基础上我们可以进一步去产生符合高斯分布的高斯白噪声