作者:小墨,本文转载自:ZYNQ微信公众号

依稀记得,当我第一次接触ZYNQ的时候,是在一个从零开始的项目中,可以说是需求都没确定,只是需要FPGA与ARM结合的平台,在迷茫的选择中,我选择了xilinx zynq7z035ffg676这个型号的板子。

因为需要自己一个人做PL和PS端的工作,这两部分的很多细节我都不了解,于是我向老板的一个专门做这块的朋友请教了我的一些问题,下面来整理一下。

平台:win10+64位

软件:Xilinx_Vivado_SDK_2017.4

硬件:XC7Z035/030-FFG676I

ACP、GP、HP区别

64b AXI ACP slave ports ,32b GP AXI Master Ports ,High Performanmce AXI 32b/64b Slave Ports 的区别以及应用范围?

回答: 64b AXI ACP slave ports接口中ACP表示The accelerator coherency port (ACP),它提供PL侧的FPGA代码对PS侧的DDR内存的缓存一致性访问(PL侧为主或发起者),具体的描述在UG585的3.5.1节和5.4节。

32b GP AXI Master Ports接口中,GP 表示General Purpose,PS一侧为主或发起者,具体描述参见UG585的5.5节。PS侧程序通常通过该接口访问PL侧的外设或者少量数据。

High Performanmce AXI 32b/64b Slave Ports,PL侧为主或者发起者,用于PL侧将大量数据发送到PS侧的DDR或片上内存中。

High Performanmce AXI 32b/64b Master Ports,PS侧为主或者发起者,用于PS侧将DDR或片上内存中的大量数据发送到PL侧的BRAM或FIFO或其它处理模块。

AXI接口是PS和PL之间互相访问的主要方式,具体内容参见UG585的第5节。

像配置芯片这样的操作,走AXI GP接口就可以了。AD936x的采样数据可以走HP接口传输。

PS-PL时钟是怎么配合使用的?

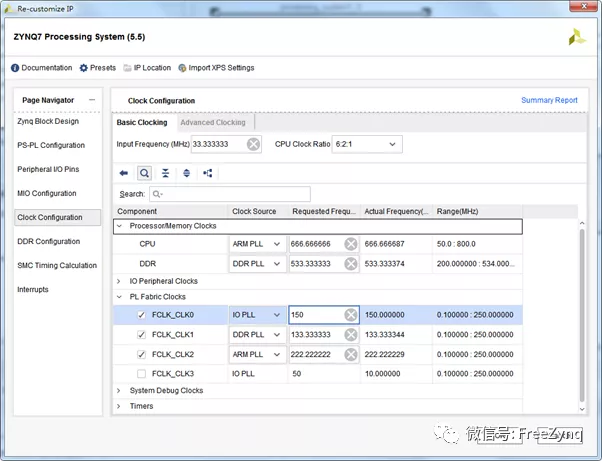

回答:zenq对外有一个PS_CLK的时钟输入,其内部有三个PLL,ARM_PLL、DDR_PLL、IO_PLL,分别用于ARM CPU、DDR和外设的时钟产生。PS一侧可以从这些产生的时钟里选择4个送给PL侧使用,参见下图:

由于所有的PS侧时钟都源于同一个输入时钟信号,因此不是所有的频率都能准确的得到。PL一侧也可以从专用时钟引脚接入不同的时钟使用。

例如AD9361的采样数据伴随着其随路时钟进入PL侧,PL侧采用双口RAM或FIFO存储数据(用随路时钟),存够1024个样本后,通过High Performanmce AXI 32b/64b Slave Ports将数据写入PS侧的DDR中(AXI接口用的PS侧的时钟)。

时钟的具体内容在UG585的第25节。

IRQ 关于中断请求是否存在I/O冲突的一些问题?如下图

回复:没有冲突,PL侧向PS侧最多16个通用中断信号,4个CPU私有中断信号,再多就只能通过查中断寄存器的方式扩展中断了(单个中断信号加中断指示寄存器的方式)。

PS一侧到PL的中断信号,每勾选一个就会增加一个信号端口。

中断的描述参见UG585的第7节。

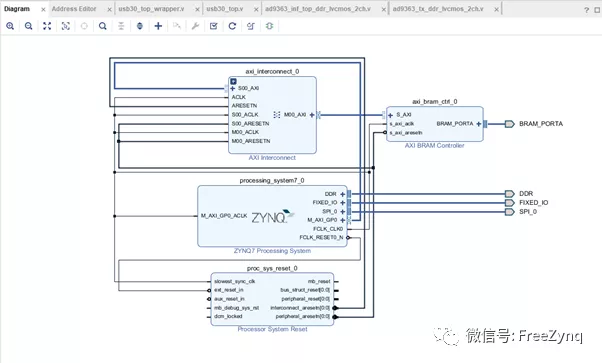

二、例如下框图,哪些引脚需要约束,判断条件?顶层文件top与其余module模块是包含关系还是并列关系?

答复: 上面黑体的模块表示当前的顶层模块,他下面有两个子模块design_1_i(是一个Block Design其打开后对应下个问题中的图中内容)和u_usb30_top。再下面的模块属于加入到工程中,但没有使用的模块。

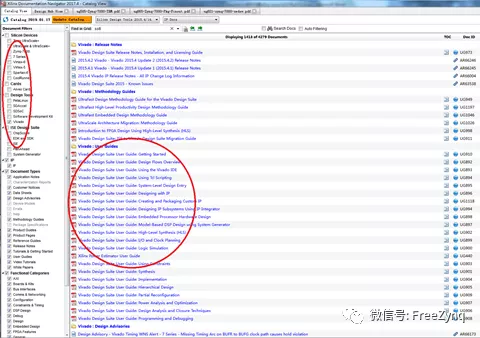

首先要先综合工程,参见下图:

综合完成后,点击左下的open Synthesized Design参见下图:

然后,点击右上角选择I/O Planning,参见下图:

然后在下面的IO port列表中分配PL侧的管脚位置和电平标准,参见下图:

将结果保存后(会存到一个XDC后缀的文件),管脚就分配好了。vivado的具体使用参见UG910.

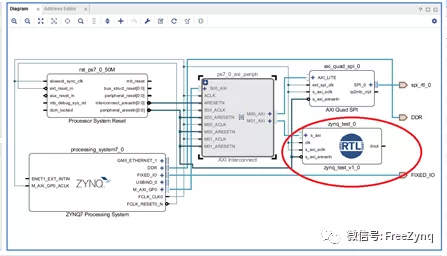

这种框图的设计一般结合PL和PS端,怎么配合PS和PL端的使用?

答复: 上面的Block Design中标ZYNQ的部分就是PS部分,其余部分都是PL部分,从ZYNQ模块引出的DDR、FIXED_IO和SPI_0都接在PS侧固定的管脚上。BRAM_PORTA接口应和PL侧自己写的FPGA代码连接。

有两种设计模式:

一种是全部用BD来实现,自己写的代码导入DB中,然后在BD中连接信号。

另一种是用BD来例化PS侧相关的IP和AXI中间件,然后wrap成verilog文件,顶层文件和PL侧功能用verilog实现,BD部分被作为模块调用。

vivado的具体使用参见UG910。

这是一个从未接触过ZYNQ的开发者的一些疑惑,希望对大家有一些帮助。