本文转载自:FPGA入门微信公众号

1、对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。

2、当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

3、当主机进行读数据时,接受数据即可。

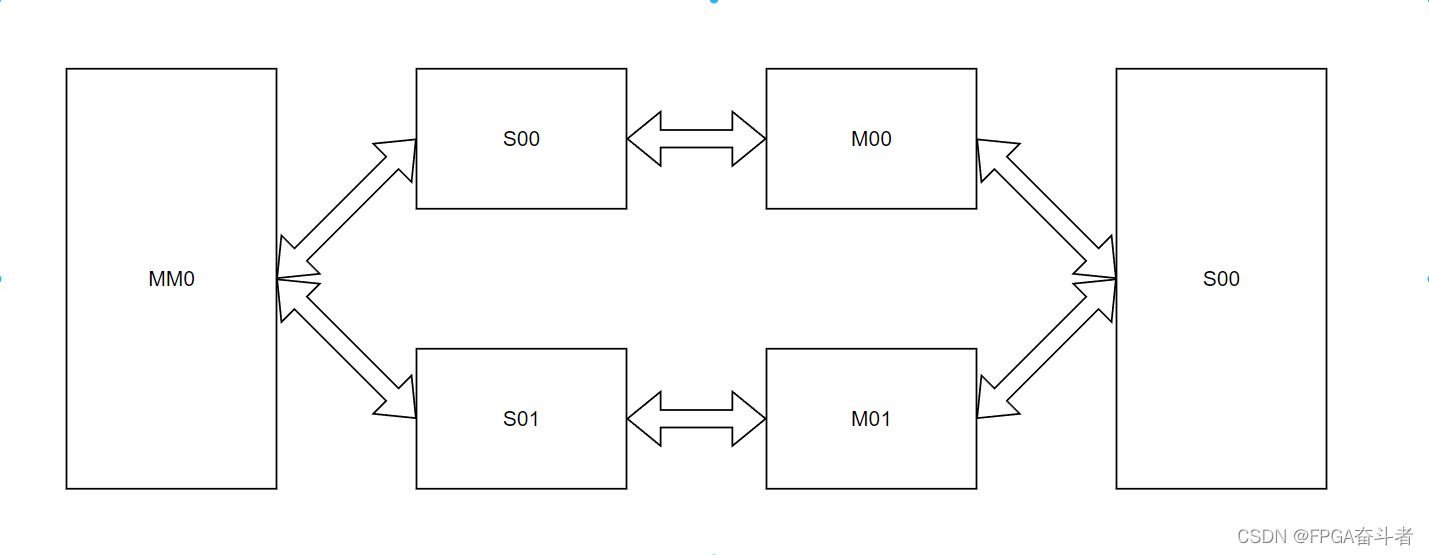

4、具体如图所示

5、共5路信号,每路信号都包括握手信号,ready和valid,当ready和valid都有效时,此时数据才有效,且信号不存在相互等待关系,以免发生死锁现象。

6、包括aw,w,b,ar,r,每路信号都应用FIFO做缓存,使数据对齐。

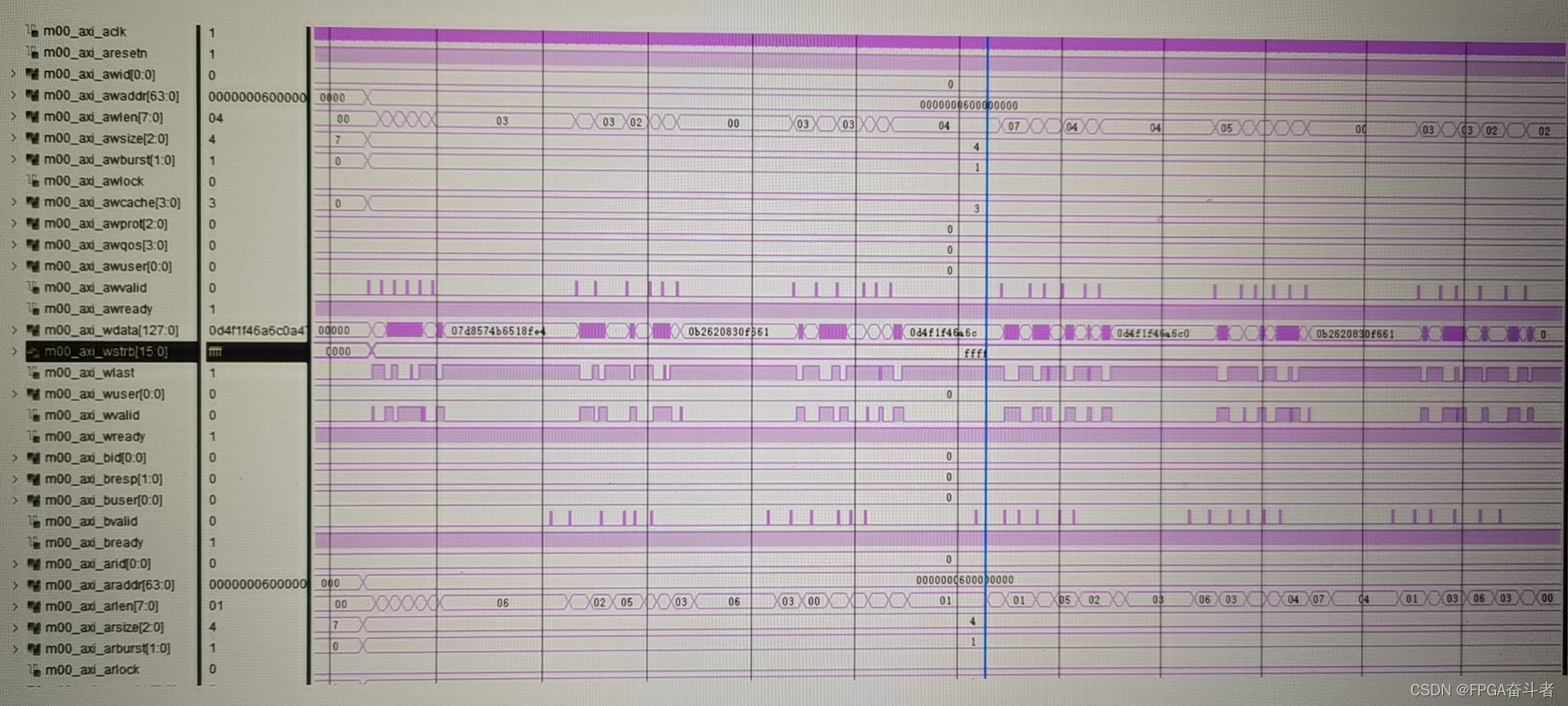

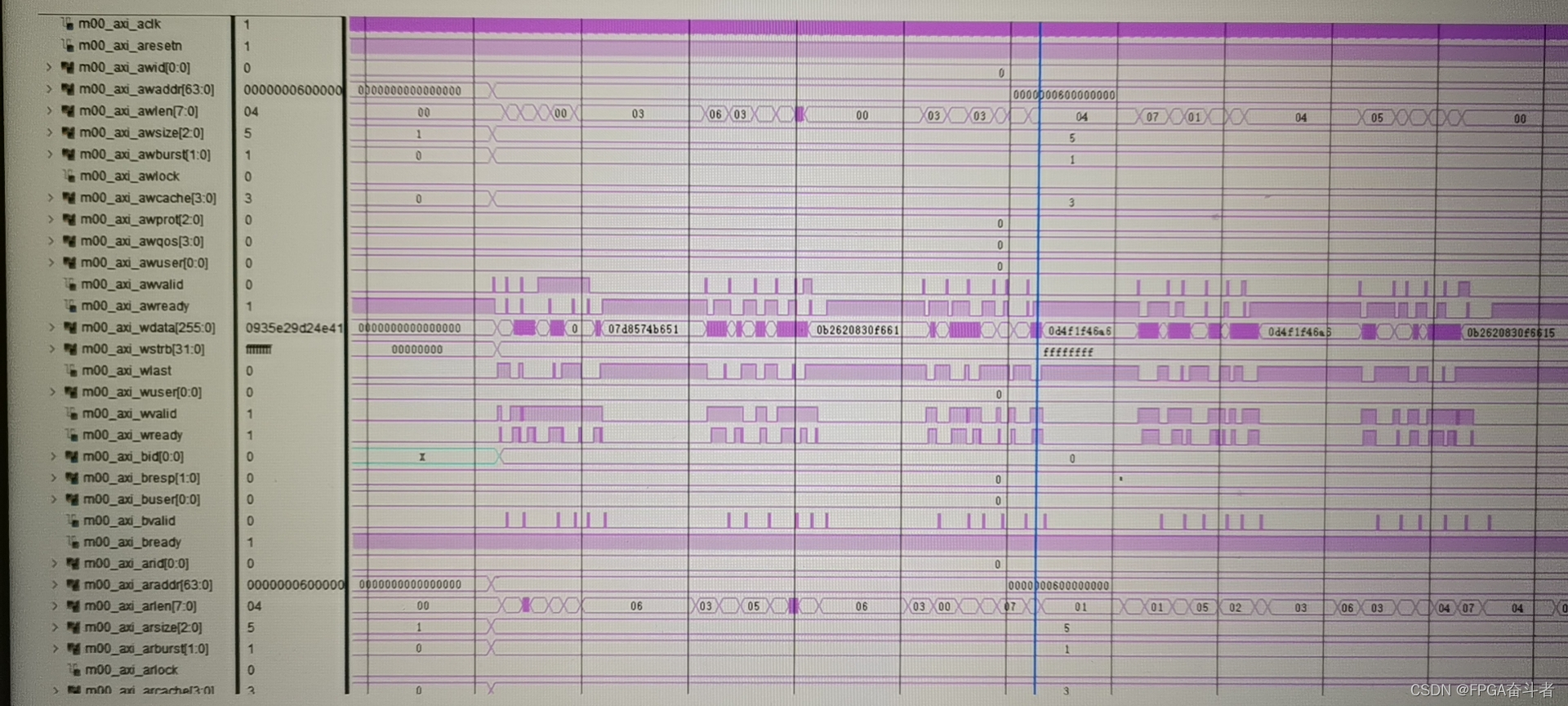

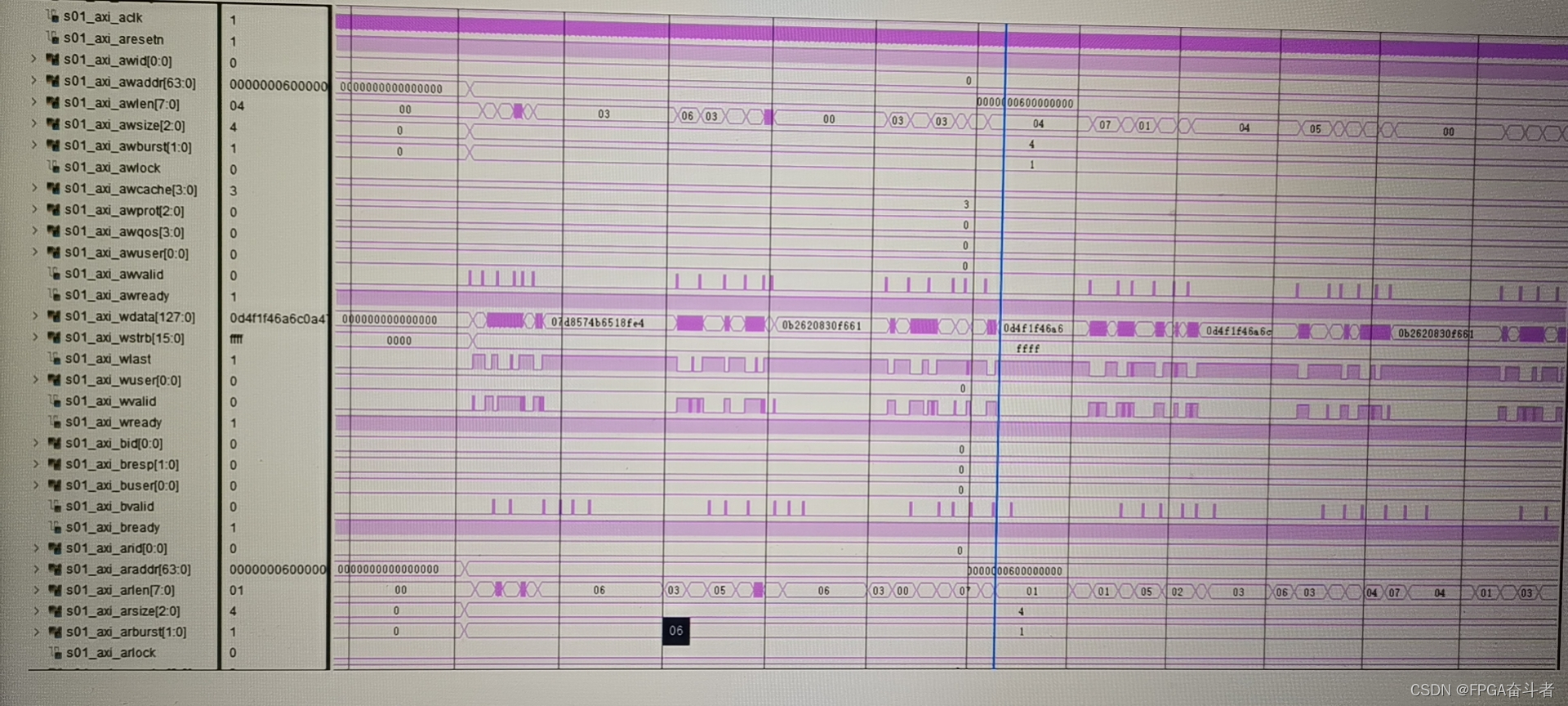

7、代码仿真如下

(1)

(2)

(3)

(4)

(5)

(6)

8、对其中的一组数据加延时,同样也可以使数据对齐,容忍度为FIFO的大小。