本文转载自: 雷达通信工程师微信公众号

主要方式简单对比

USB3.0接口

目前在FPGA上实现USB3.0高速通信主要有两种方案,一种是采用FTDI的FT601系列芯片,官方自带驱动和基础的FPGA接口实例;

另一种为采用赛普拉斯的EZ-USB® FX3 SuperSpeed USB 控制器,同样官方也提供驱动和FPGA示例代码,主要特性如下:

以上两种方案都是支持5Gbps传输速率,和FPGA采用32bit并行数据通信接口;

千兆网以太网

千兆网目前应用最广泛的接口之一,是个人台式电脑和服务器的标配,也可用于FPGA和PC之间的高速通信,免驱动,通过简单的调用操作系统API即可使用,借助以太网自身的技术生态还可很容易实现一些其他功能,如多节点数据交换等;

FPGA实现1、2.5Gbps网络接口可通过外接PHY或者使用高速Serdes收发器实现,介质方面可选择光口,或者RJ45;如果使用外部PHY的方案,可以根据传输介质的需求选择合适的PHY型号,部分PHY支持光口传输;若所使用的FPGA型号(以xilinx为例)带有高速serdes收发器,也可直接采用GTX实现SFP光模块接口,该方式省去了PHY芯片的电路,FPGA逻辑实现上也更简单,当需要用光口传输时,直接插上SFP光模块即可,若需要用RJ45接口,则插上专用的SFP电口模块转出RJ45,电口模块和光口模块分别如下图所示;

万兆网以太网

万兆以太网技术在运营商核心网、互联网大厂的数据中心中应用很多,目前有多种速率等级,基础10Gbps,更高的25G、40G、100G、200G等,基础的10Gbps可以采用专用的万兆网线进行传输,更高速率的标准一般通过光纤和高速铜缆DAC进行传输,DAC线缆因损耗其传输距离较短,通常为3米以内,越是高速越难以远距离高速传输;远距离高速传输通常采用光介质(光纤+光模块)方案;xilinx的vivado中提供了多个万兆以太网的IP核,速率从10G到100G都有(高端IP需要付费),除了IP中实现的PHY和MAC之外,应用还需要实现IP协议栈,如TCP、UDP,其中UDP协议较为简单,能满足绝大多数应用场景;TCP则较为复杂,也有第三方提供收费的IP。

要想实现高性能的传输,特别是25G以上的一些速率等级,除了FPGA端,PC端的驱动也非常重要,目前普遍采用DMA+用户端轮询驱动的方式,将数据包的收发绕过操作系统内核区间(避免内核与用户区之间的拷贝),直接由用户区程序进行处理,使用轮询而不是CPU中断(CPU中断响应时间不确定性较大),同时用零拷贝技术传递数据,减少在内存中的拷贝次数,提高处理效率,下图为一种40G的光模块。

PCIE接口

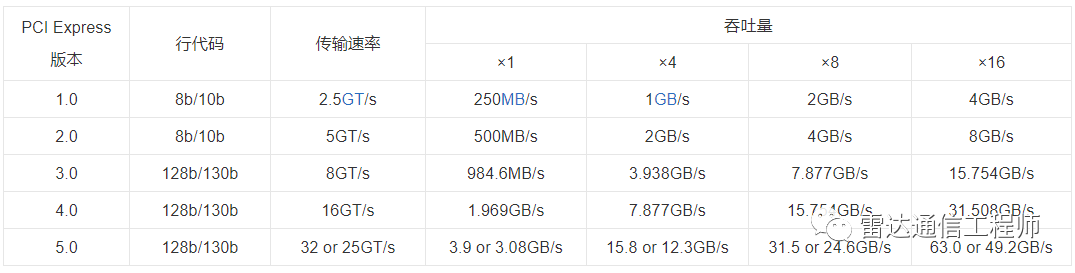

PCIE接口很常见,如个人电脑的主板上都有PCIE的插槽,这也是服务器或PC与外部设备进行超高速数据传输的主要接口,像GPU卡、万兆网卡、NVME固态硬盘等都是连接在PCIE通道上。

FPGA上,intel和xilinx两家在容量稍大的FPGA系列z中都设计了PCIE的硬核,如xilinx的7系列以上中等容量以上型号都具有PCIE核,只是性能有所区别,如7系列中的K系列只支持PCIe Gen2速率等级,只有V系列才支持PCIe Gen3。xilinx提供的XDMA PCIE核将PCIE和DMA封装在一起,提供AXI4-Stream或者AXI4-MM高速数据接口和AXI4-LITE低速接口,实测在windows系统上采用PCIe Gen3x8连续传输数据流可达到6.4GB/S以上。