本文转载自:Linest-5的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

实验介绍

本节介绍最简单的实验工程,用串口打印helloworld。

实验工程基于Vivado2018.2实现

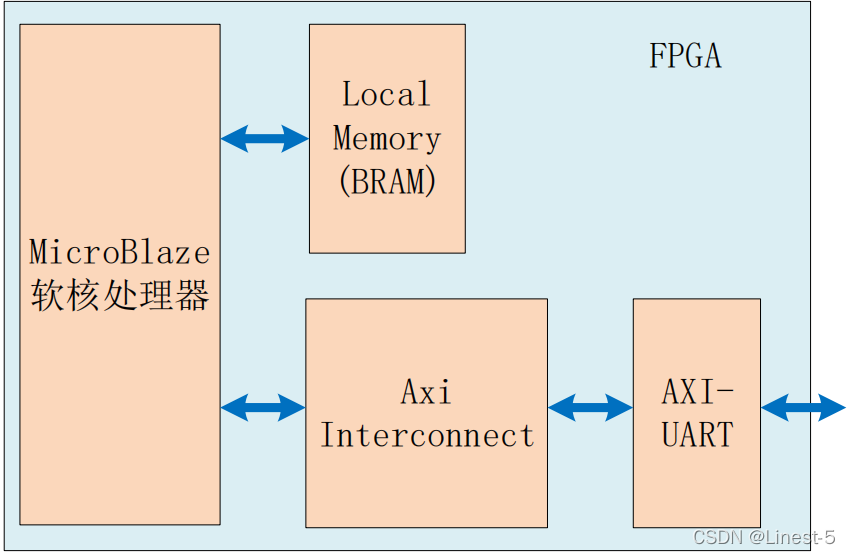

下图是实验工程的框图,非常简单,MicroBlaze作为处理软核,搭载着片上存储器BRAM,MB通过AXI互联接到AXI-UART,通过控制就可以在串口打印信息了。

硬件设计(Vivado部分)

创建工程

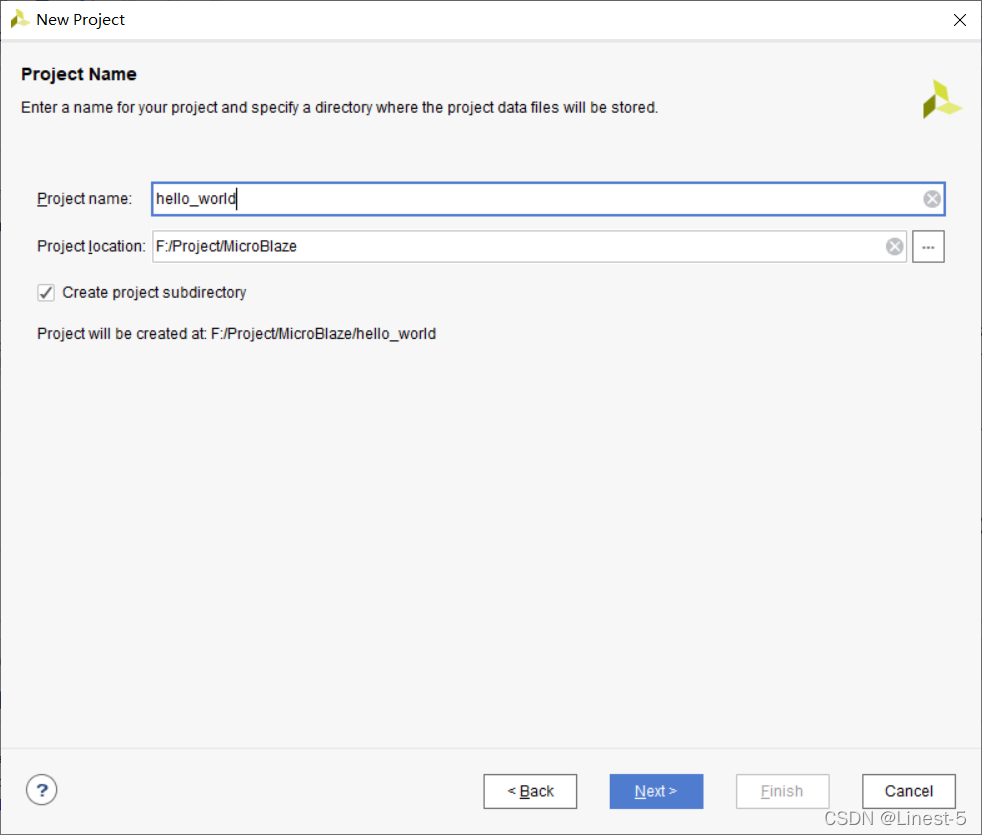

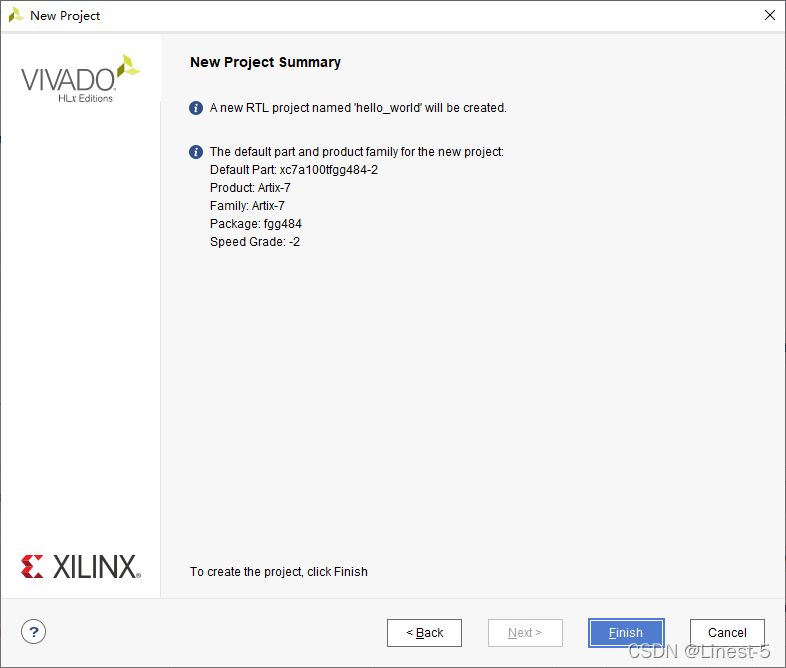

点击Vivado的Creat Project,创建一个新的工程,命名为hello_world,注意命名不能含有中文空格等字符,只允许字母和下划线组成,存储位置自己定义,同样需要注意的是路径不能过长,否则综合可能不通过。

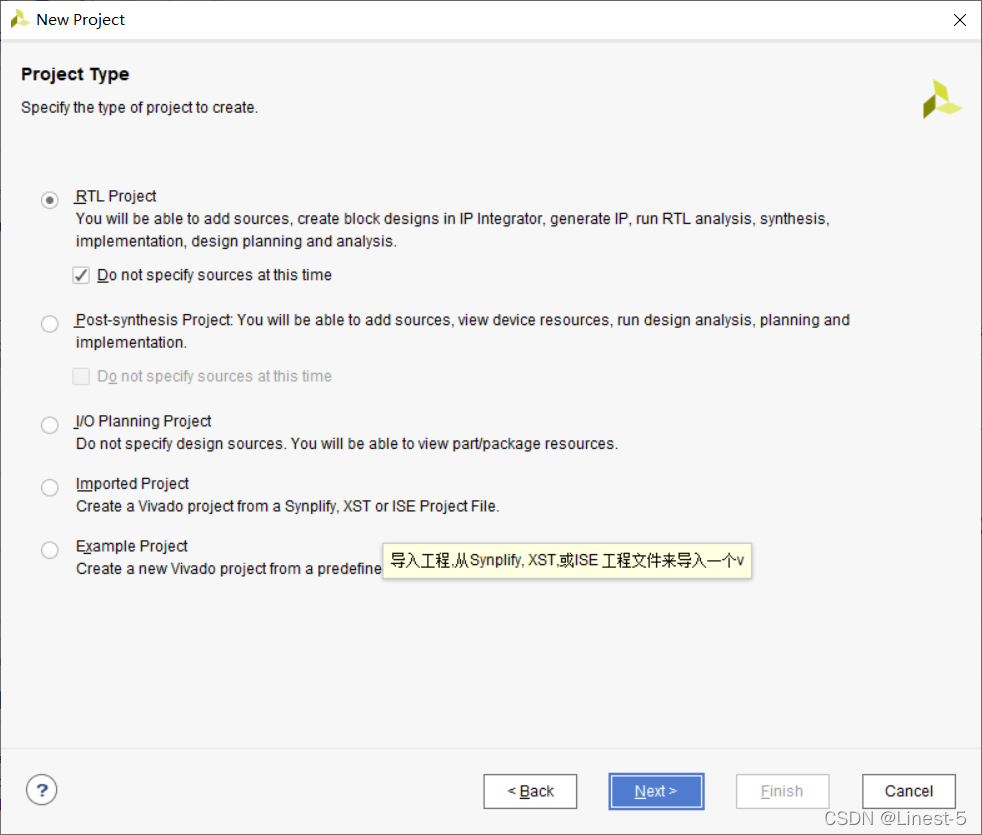

选择先不指定设计文件

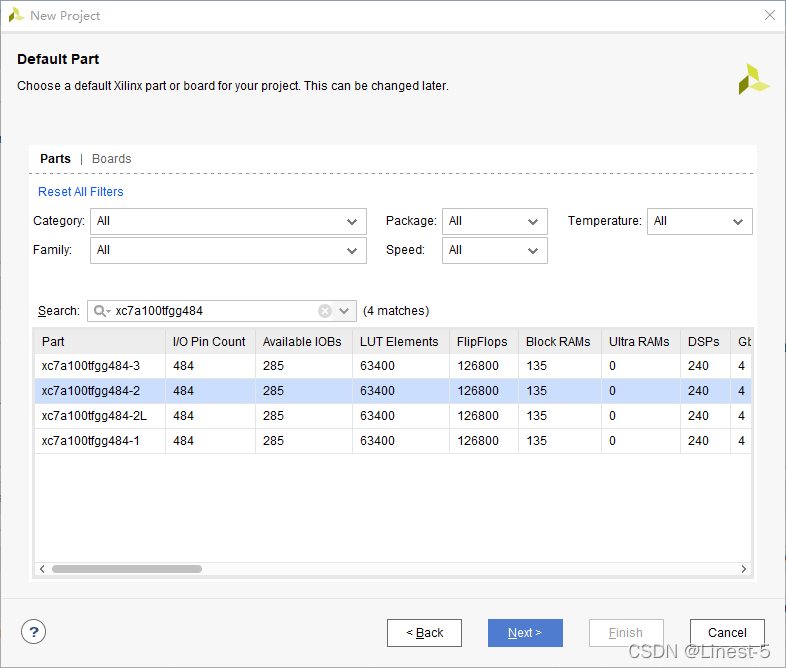

选定自己使用器件的型号,可以在器件的使用手册中查询到,我使用的是黑金的AX7103,器件型号为xc7a100tfgg484-2。

在这里就可以看到汇总信息,点击Finish即可。

搭建Block Design

点击左侧菜单栏中的creat block design

MicroBlaze部分

点击+号搜索MicroBlaze,双击添加到BD中

双击MB模块查看其中的配置信息

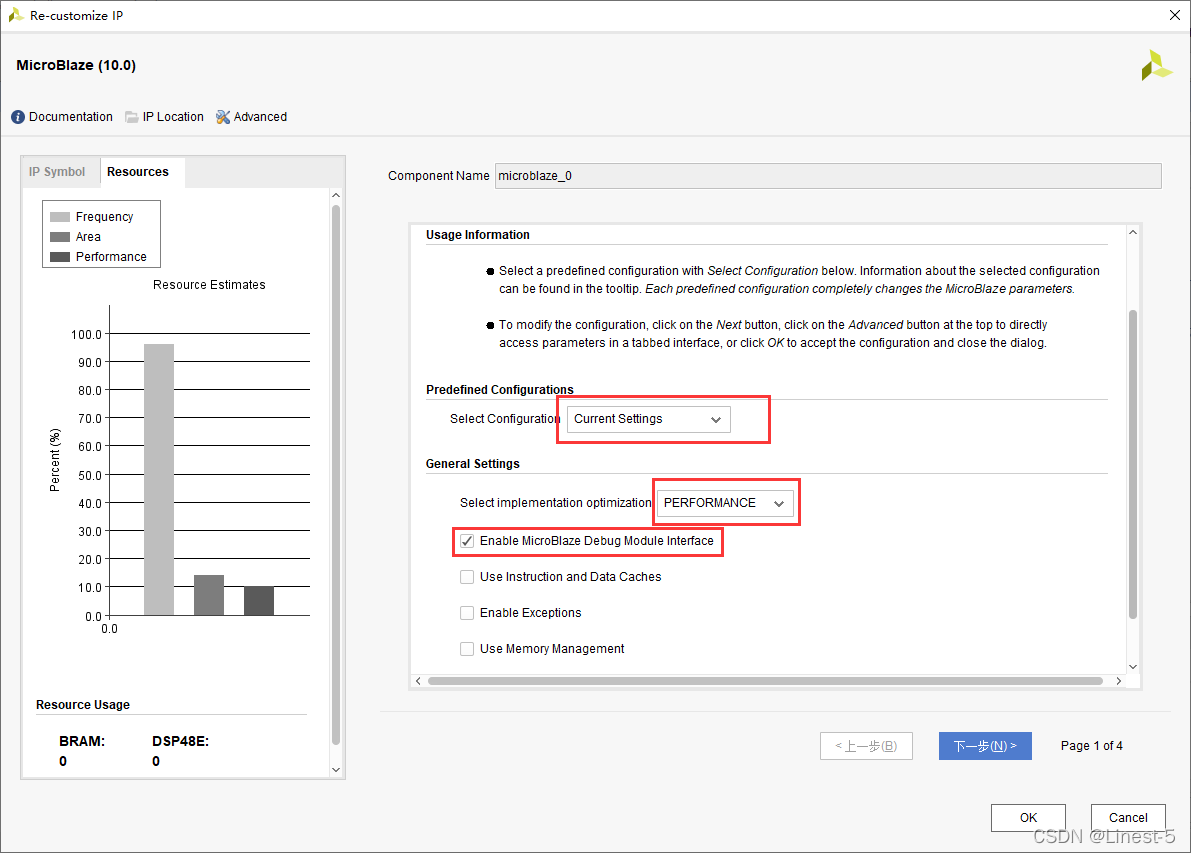

第一页

Predefined Configurations:配置模板,点击 Select Configuration 右侧的目录框能够看到多个模板选项(Minimum Area、Maximum Performance 等),但本次实验不需要用到模板,因此保持默认选项“Current settings”就可以。

Select implementation optimization;用于使能面积优化功能,打开其右侧的目录,可以看到有PERFORMANCE、AREA 和 FREQUENCY 三个选项表示三种优化方式,其中 AREA(区域)表示三级优化,速度最慢占用资源最少;FREQUENCY(频率)表示八级优化,速度最快占用资源最多;PERFORMANCE(性能)是五级优化,速度和资源占用量在 AREA 和 FREQUENCY 两者之间,本实验选择PERFORMANCE。

Enable MicroBlaze Debug Module Interface:使能调试功能,一般情况下都开启该功能,只有在资源十分紧张的情况下才会禁止此功能。

Use Instruction and Data Caches:使用指令和数据缓存。当使用外部存储时,激活这个选项可以明显地改善性能,由于本次实验使用的是本地存储,该选项对实验没影响,因此不选择。

Enable Exceptions:异常功能的使能。

Enable Discrete Ports:使能软核上的独立端口。

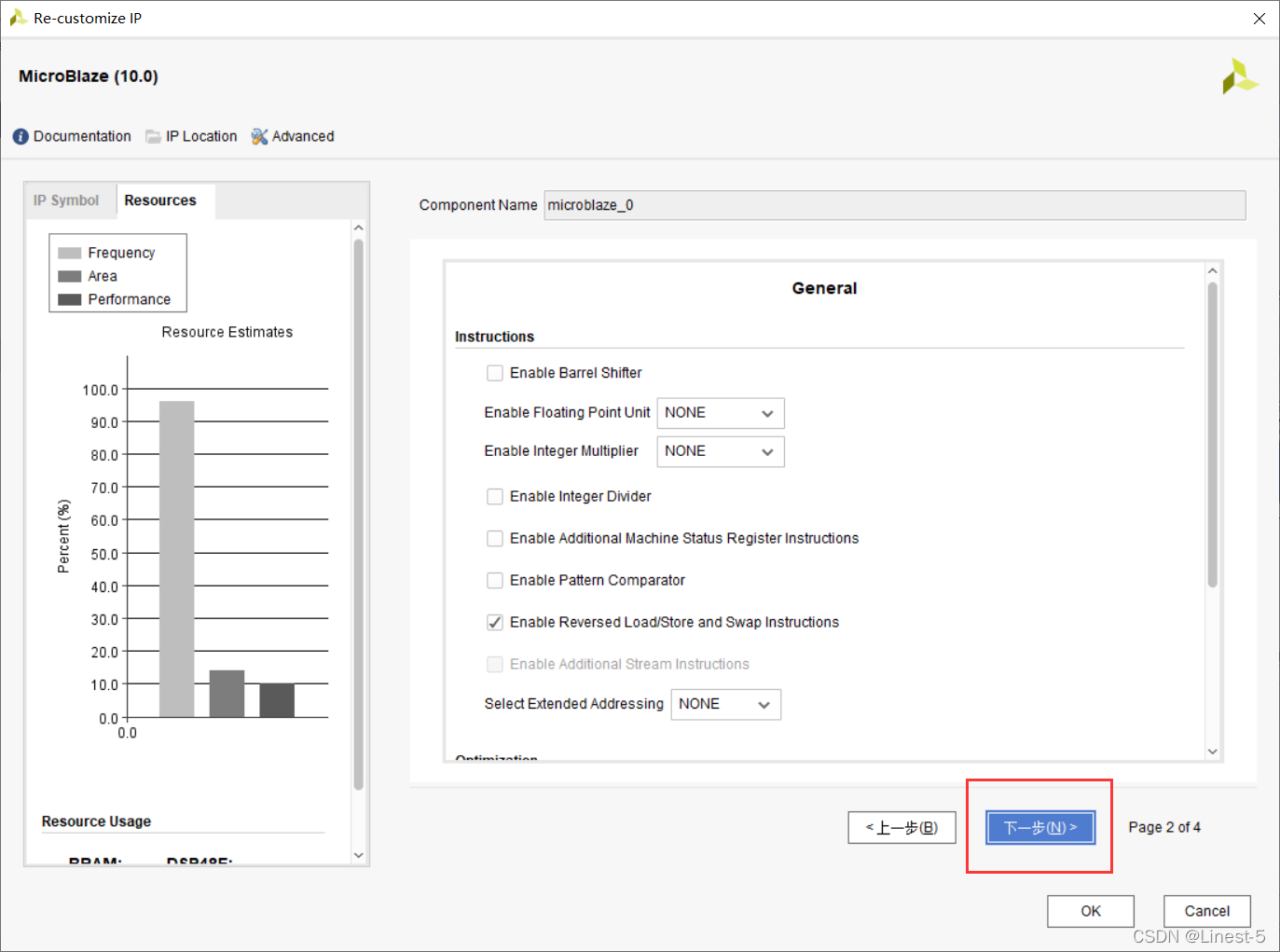

第二页

配置完成后点击“Next”进入第二页 General 页面,General 页面能够选择单元的选择和优化。直接保持默认就可以了,点击“Next”进入 Debug 页面。

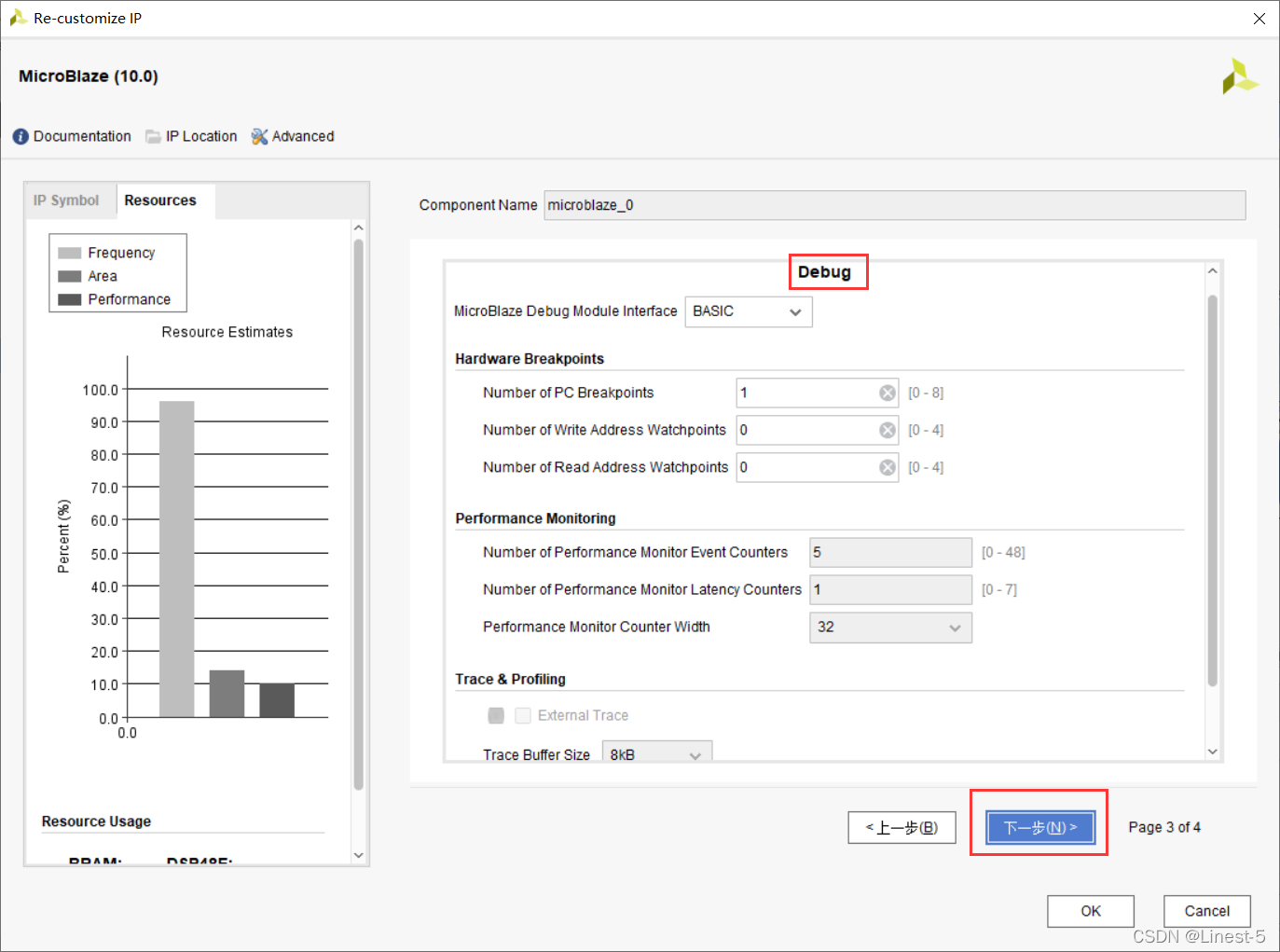

第三页

这一页也是保持默认即可,这一页的配置内容是只有在第一种选择了debug才会出现的。

第四页

在Local Memory Bus Interfaces的选项中,两个都勾选,分别表示使能指令接口以及数据接口,AXI and ACE Interfaces中选择AXI接口,并且只需要勾选数据接口,指令接口大多数的情况下是不需要的,只有在特殊情况下才需要勾选上。Stream Interfaces 和 Other Interfaces 分别用于开启 Stream 流接口和一些其它接口,本实验中直接保持默认,配置完成后点击OK完成 MicroBlaze 的配置。

外围模块部分

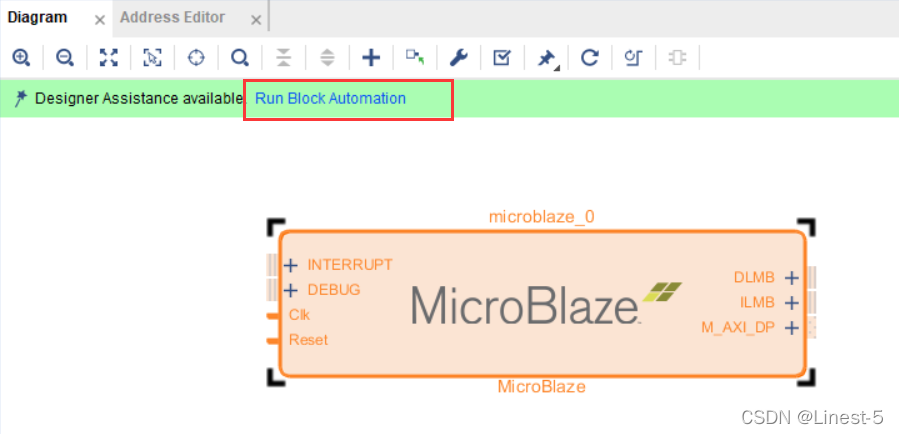

点击Run Block Automation

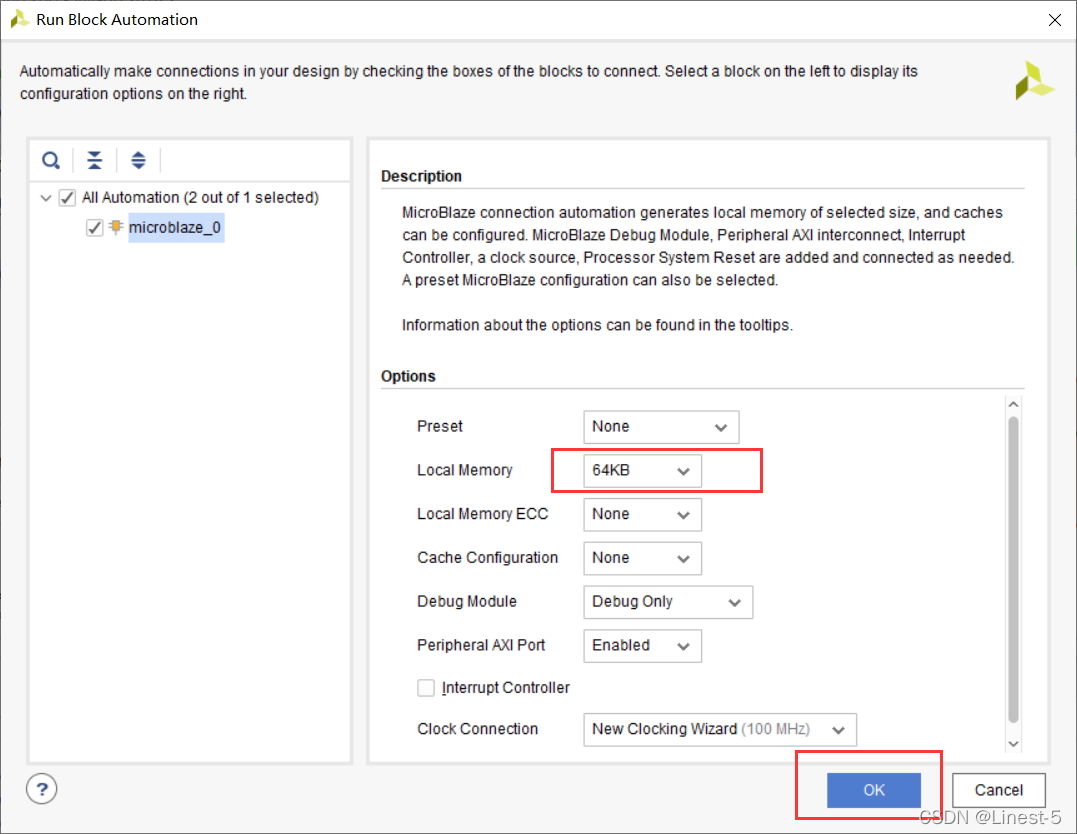

在这个界面中,需要将Local Memory选择为64kb,尽量选大点,因为MicroBlaze自身是没有存储单元的,需要在片上添加存储,如果选太小的话,程序可能无法运行。点击ok。

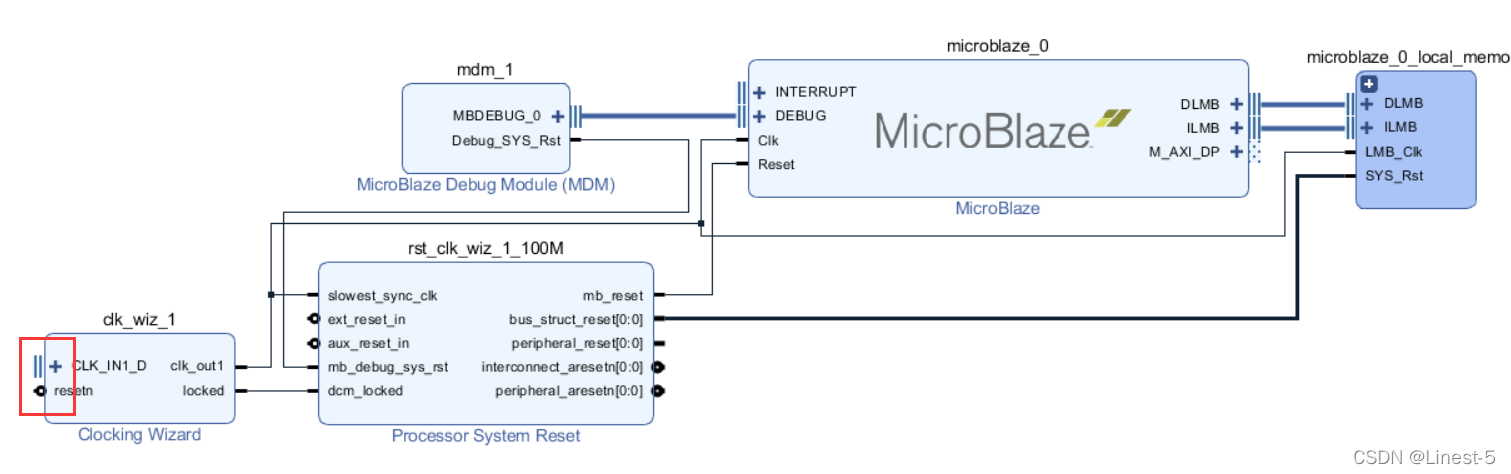

然后会生成多模块界面,该界面可以看到自动生成了四个模块。clk_wiz_1 模块提供系统时钟,rst_clk_wiz_1_100M 是系统复位模块,用以给系统各个模块提供复位信号,mdm_1 是 MicroBlaze调试模块,microblaze_0_local_memory 模块是片上存储模块。

时钟模块

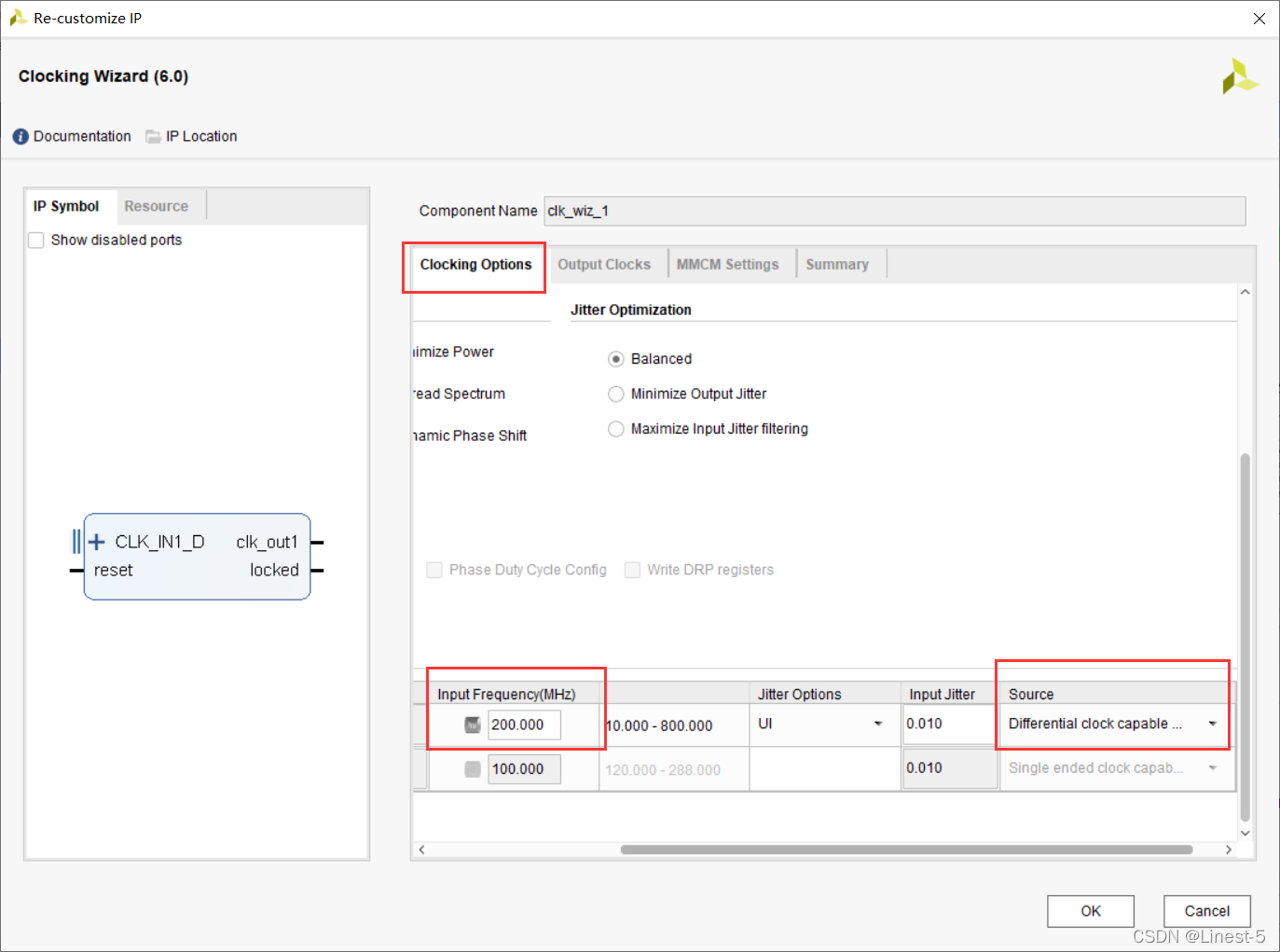

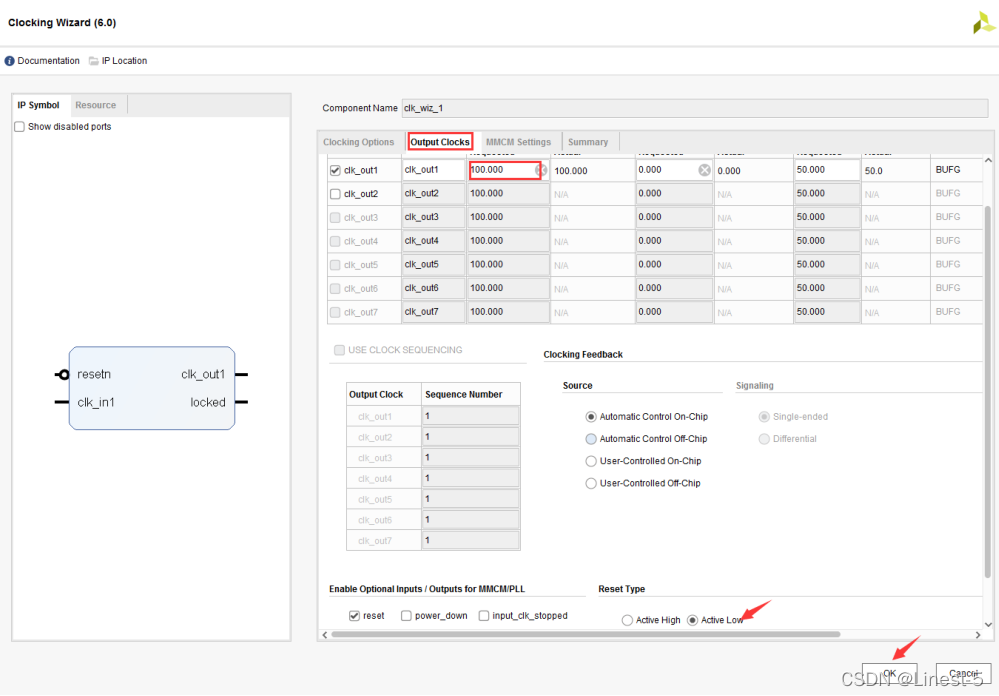

再对时钟模块clk_wiz_1进行配置

双击打开配置界面,再输入时钟将输入时钟配置成200Mhz,Source栏选择Differential clock capable pin,也就是差分时钟。注意!我只是按照我是用的板子进行配置参数,需要根据自己实际使用的板子所需要的输入时钟进行配置,可以查询板子的手册,否则实验可能不通过。

时钟输出选项中,选择输出时钟为100Mhz,复位类型选择低有效,注意!因为我的板子是复位键按下时低电平,未按下是高电平,所以设定为低有效,根据自己的板子实际情况定。

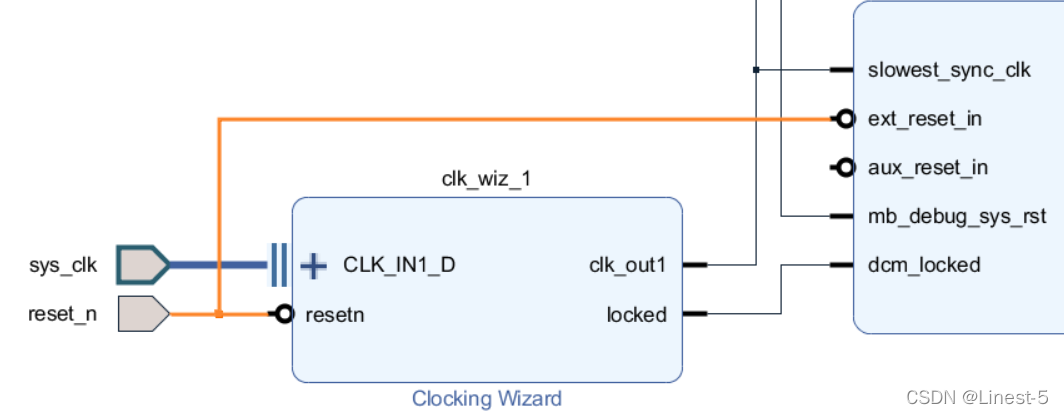

clk_wiz_1 模块配置完成后,可以看到 clk_wiz_1 模块的输入时钟变成了单端输入,复位为低电平有效。

鼠标右击时钟模块的时钟和复位管脚,选择make external,将其管脚引出。

还可以对管脚的名称进行修改。

将复位引脚于复位模块的ext_reset_in相连

Uart部分

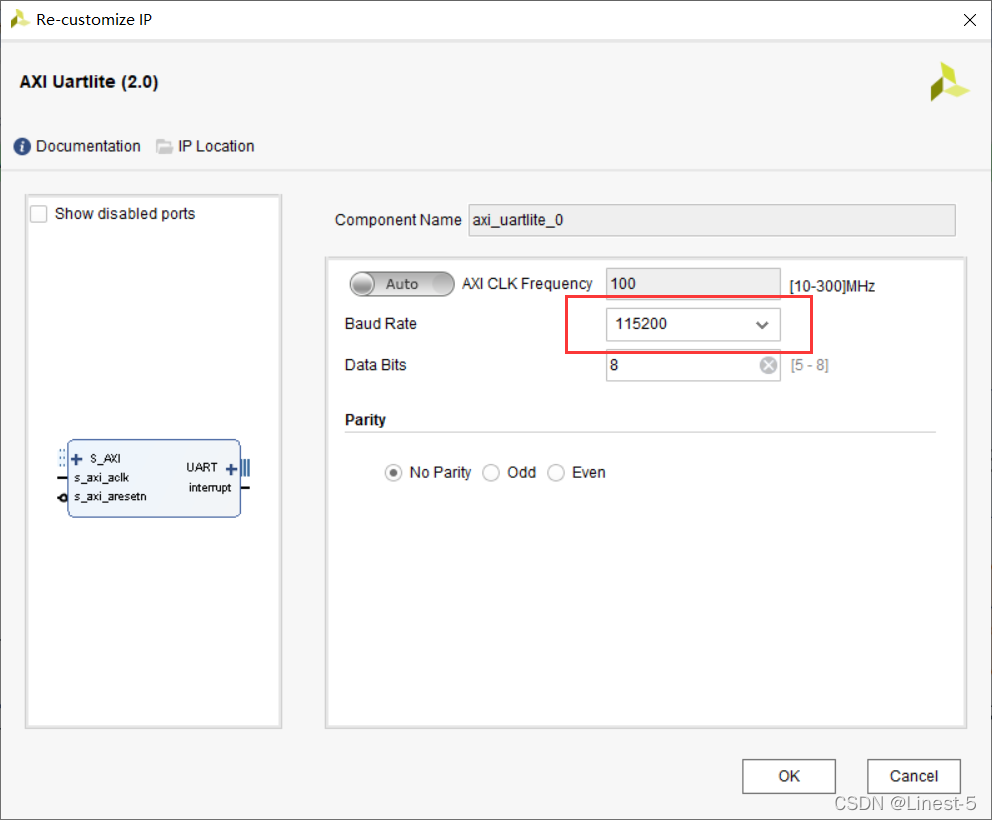

既然将实现串口打印信息的实验,因此需要有uart模块进行串口通信,添加uart模块,点击+号搜索uart双击添加。

双击uart模块进行配置,将波特率选择115200,需要与之后串口的波特率大小保持一致,其余保持默认即可。

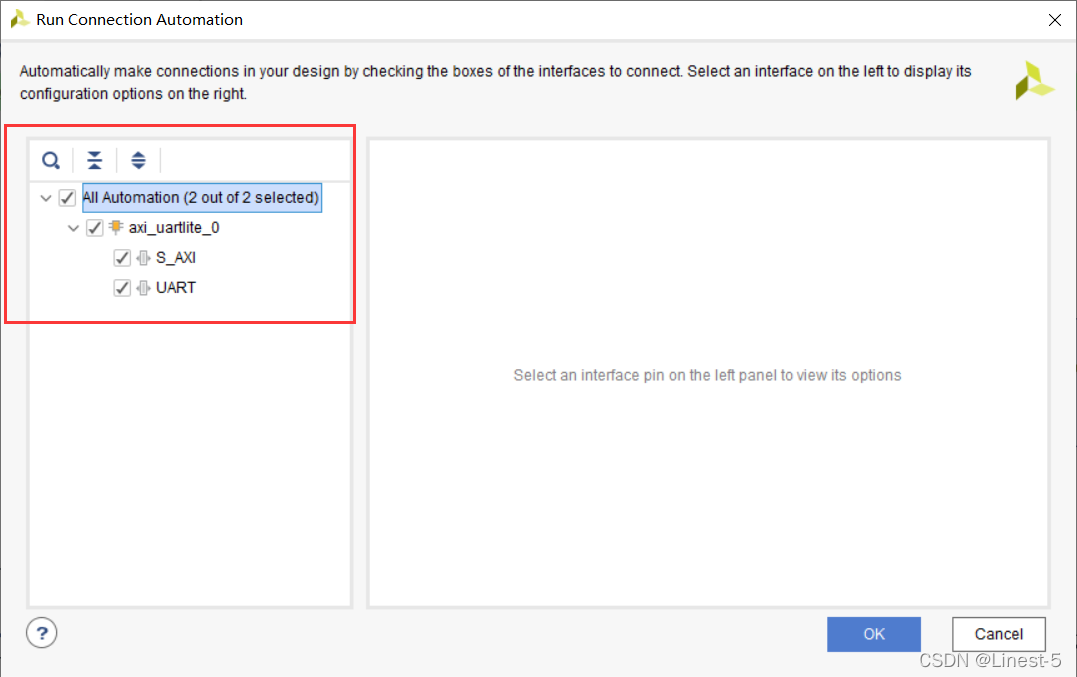

再点击自动连线即可完成Block Design的设计。

管脚绑定、时钟约束

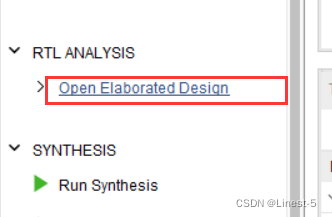

点击左侧菜单栏中的Open Elaborated Design。

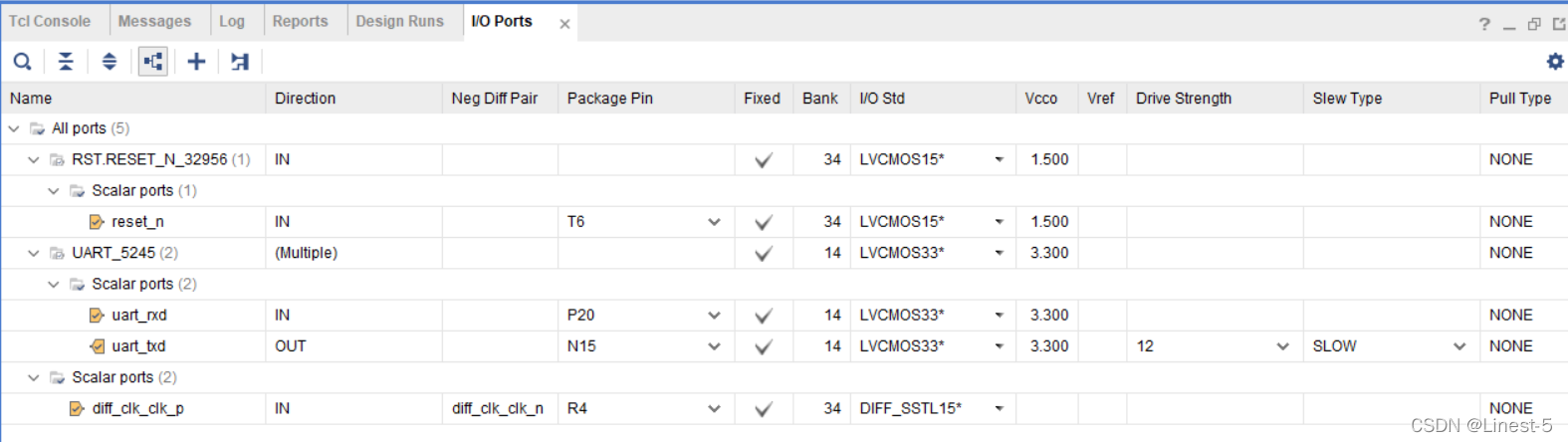

点击上方的windows选项中的I/O ports,进行管脚分配。

根据自己的板子的原理图或者手册进行分配即可。CTRL+S保存XDC文件。

点开Sources中的约束文件,并添加一句时序约束,目的是创建一个时钟频率为200Mhz即周期为5ns,因为我使用的板子不是官方的板子,而是黑金的第三方板子,因此需要额外添加一句时钟约束,不添加可能实验会出错。

完整的约束文件如下所示:

set_property PACKAGE_PIN T6 [get_ports reset_n]

set_property IOSTANDARD LVCMOS15 [get_ports reset_n]

set_property PACKAGE_PIN N15 [get_ports uart_txd]

set_property PACKAGE_PIN P20 [get_ports uart_rxd]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rxd]

set_property IOSTANDARD LVCMOS33 [get_ports uart_txd]

set_property PACKAGE_PIN R4 [get_ports diff_clk_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports diff_clk_clk_p]

create_clock -period 5 [get_ports diff_clk_clk_p]

生成Bit流文件

直接点击左侧菜单栏中的Generate Bitstream生成比特流文件。

点击上方菜单栏中的File->Export->Export Hardware,将硬件设计部分的信息导入到硬件,再带年纪Launch SDK,进入到软件部分的设计。

软件设计(SDK部分)

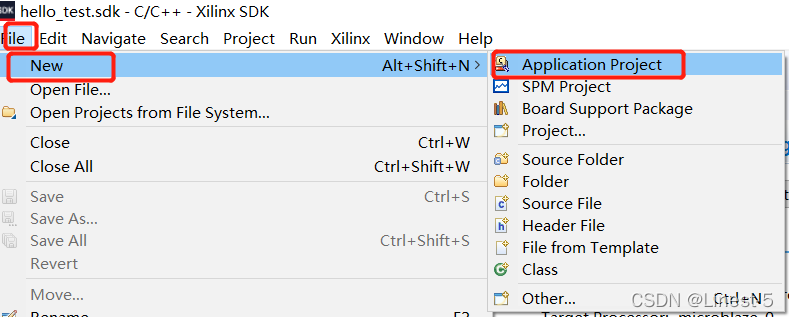

进入到SDK中,点击上方的File->New->Application Project,创建一个新工程

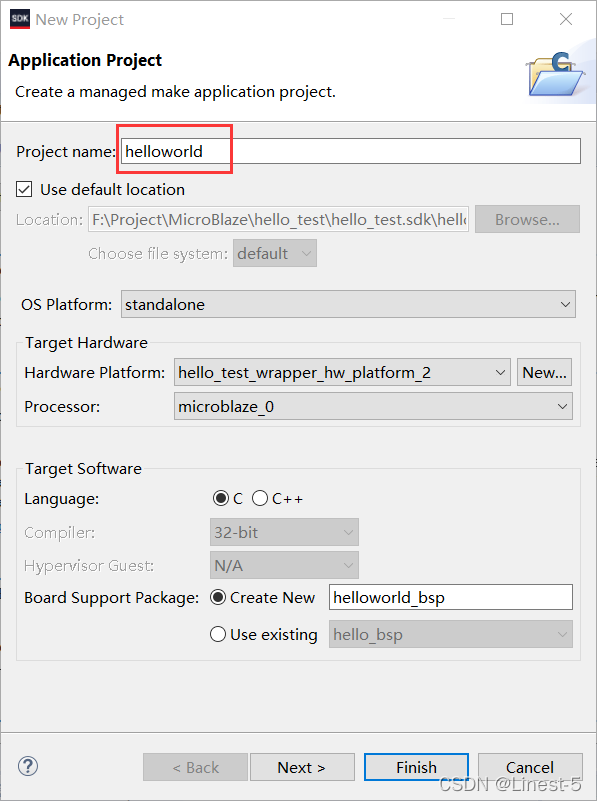

命名为helloworld,点击Next。

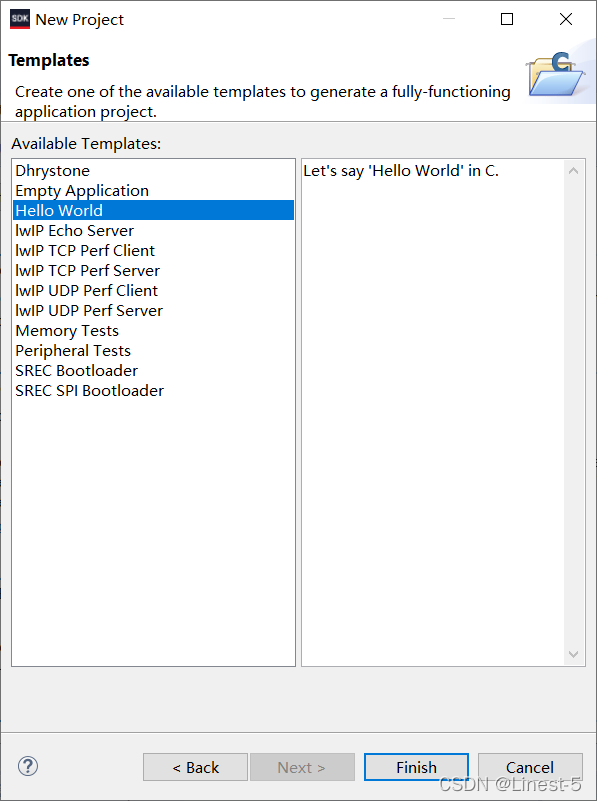

选择Hello World模板,点击Finish即可。

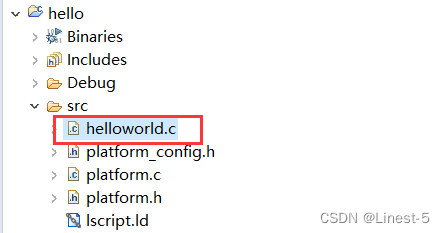

点击文件中的src中helloworld.c文件。

可以看到导入的模板,就是很简单的利用C语言写的helloworld,其中头文件中"platform.h"和''xil_printf.h''是Xilinx官方的头文件信息,直接拿来用即可。

#include

#include "platform.h"

#include "xil_printf.h"

int main()

{

init_platform();

print("Hello World\n\r");

cleanup_platform();

return 0;

}

板级验证

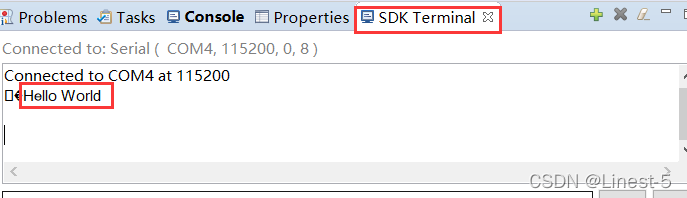

点击SDK Terminal中的+号添加端口。

Port选择端口号,波特率设定为115200,与前面的uart模块的波特率值设定一致。

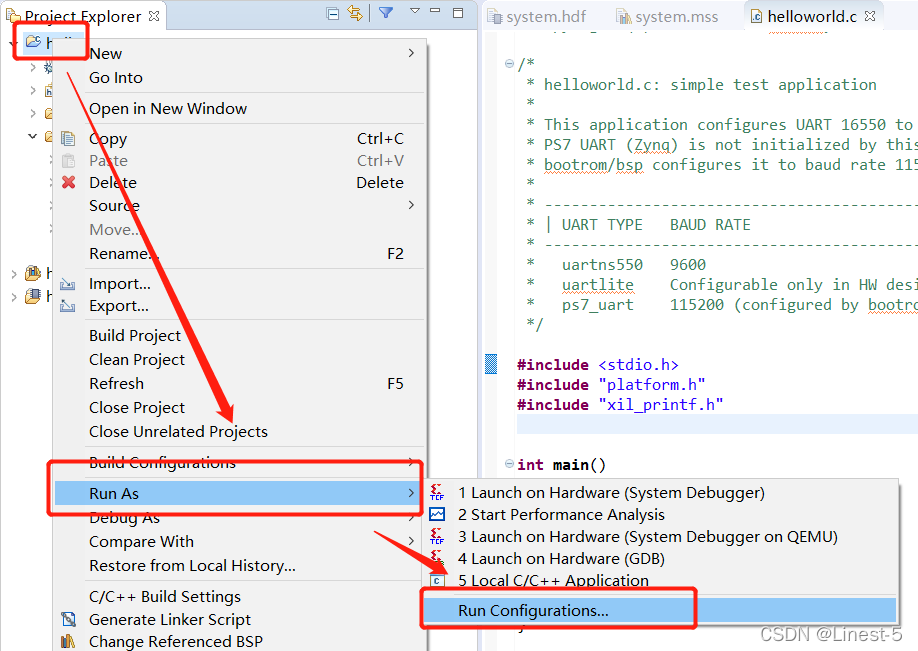

右击文件选择Run As->Run Configurations。

在Run Configurations的界面中,双击GDB,选择跳出的GDB,在右侧勾选Reset entire system以及Program FPGA,复位整个系统并启动FPGA,点击Apply,最后点击Run。

最后在端口可以看到Hello World的字样,实验成功!

总结

通过运行打印hello world 的实验,不仅可以对MicroBlaze的开发流程有个初步的认识,也可以验证板子是否可用,熟悉板子的一些参数配置,为之后的实验打好基础。