本文转载自: FPGA的现今未微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

前不久参加Xilinx举办的U55C高性能计算卡专项研讨会的时候,有一个关于HBM分享,加上我前面在微信公众号也写了2篇关于HBM的文章,这里再做一个总结,主要是和DDR的对比,对项目前期的选型做一分析。

1、单板布局

对于Virtex系列的FPGA来说,一般有4+个DDR控制器,每个控制器访问多个DDR颗粒,因此呈现的结果就是FPGA的周边布满了DDR颗粒,这对单板的布局、走线都是一个挑战。带HBM的FPGA就没有这个问题,因为HBM已经封装在芯片里,不需要外部接口,即不需要额外的布局布线。

2、接口调试

做过DDR的人都知道,DDR接口的调试,无论是硬件还是FPGA内部的逻辑,都是一个不小且麻烦的工作,这部分工作消耗的人力和时间在整个项目中都是很大的。相反,HBM已经封装在芯片内,采用标准的AXIM总线接口,不再需要DDR类似的调试工作,极大地缩短了项目周期。

3、容量

HBM的容量目前在4Gbyte、8Gbyte、16Gbyte这3个规格,在本人基于数据中心的加速项目中,已经足够用了。在基于DDR的设计中,一般是通过多个DDR颗粒并联的方式扩大存储空间,存储空间越大,对单板布局的要求就越高,以单颗粒大小为1Gbit为例,要达到4Gbyte的容量需要32个颗粒。当然HBM容量有一定限制,比不上DIMM条的容量,可能不适合对外部缓存需求巨大的场景。

4、性能

关于性能前面有文章(Virtex® UltraScale+™ HBM 使用心得(2)——性能)已经讨论过这个问题,这里不再赘述,由于图标格式的问题,这里只是贴出测试数据。

5、灵活性

HBM的灵活性来源于它的架构,Virtex® UltraScale+™ HBM 使用心得(1),从这里可以看出,32个AXIMM接口通过interconnect模块可以灵活地配置每个存储空间的大小和用户接口个数,这点相对DDR来说是无与伦比的优势。比如HBM每个用户接口最高可以获得相同的带宽,而DDR必须是每个用户共享总的带宽。

6、缺点

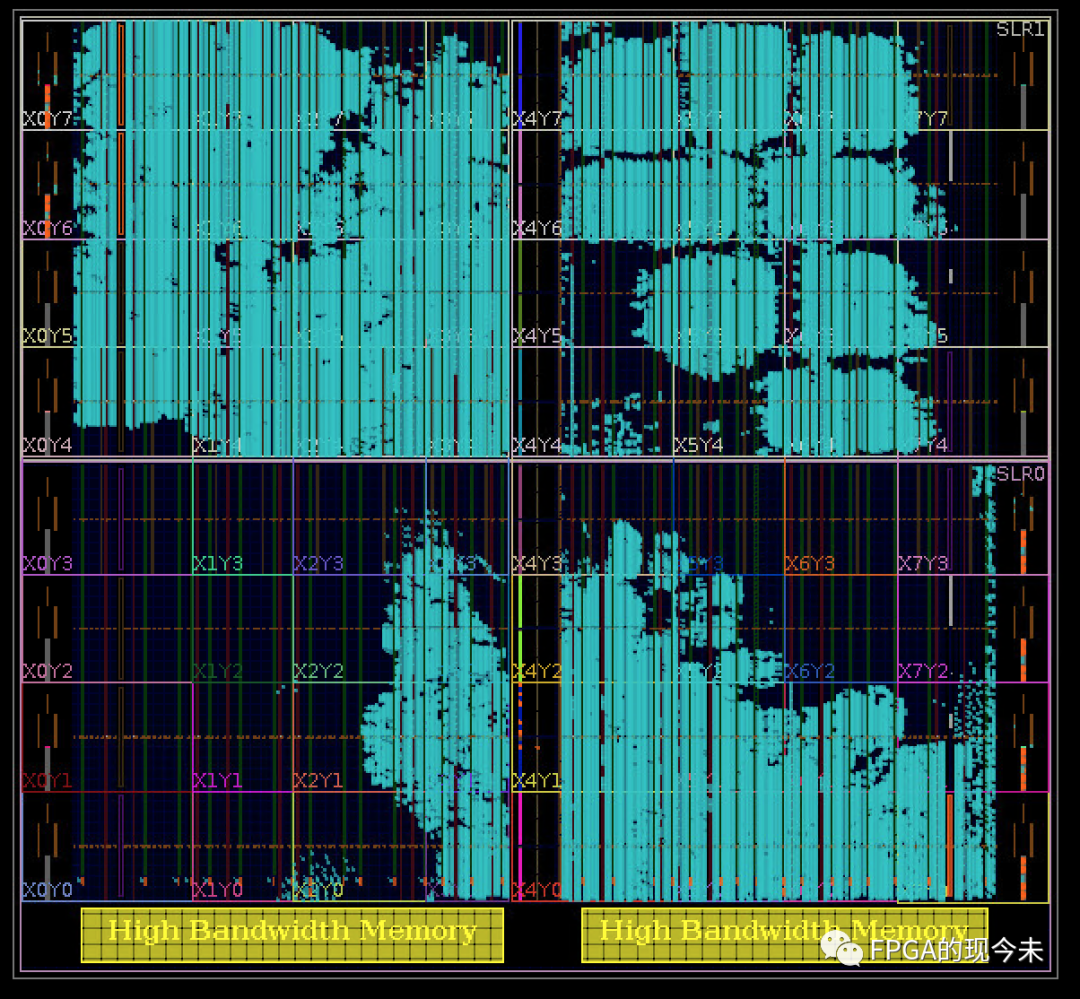

HBM也有一个缺点,那就是它存在的位置导致设计的难度加大。VU器件大部分都是多die的芯片,在设计的时候需要考虑数据流在die之间的穿越,而HBM仅在芯片的底部,如下图所示,进一步加剧了这种die之间穿越。对于多用户访问HBM的设计,要提前规划好数据流和某个die的资源消耗,这显然加大了设计难度。DDR控制在芯片中的分布,相对来说就要友好得多了。

总之,Xilinx推出HBM的芯片时,主打的点就是高带宽和大容量,作者通过2个项目的使用,相比DDR,确实有非常多的好处,建议有条件的项目,上HBM芯片是一个不错的选择。