本文转载自:Linest-5的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

本实验基于Vivado2018.2实现。

DDS原理:

DDS信号发生器采用直接数字合成,英语名Direct Digital Synthesis,简称为DDS。把信号的发生器的频率稳定度,准确度提到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的调节。也就是说它对的误差很小 与基准频率之间的误差很小。可以工作在调制状态。可以产生任意波形。

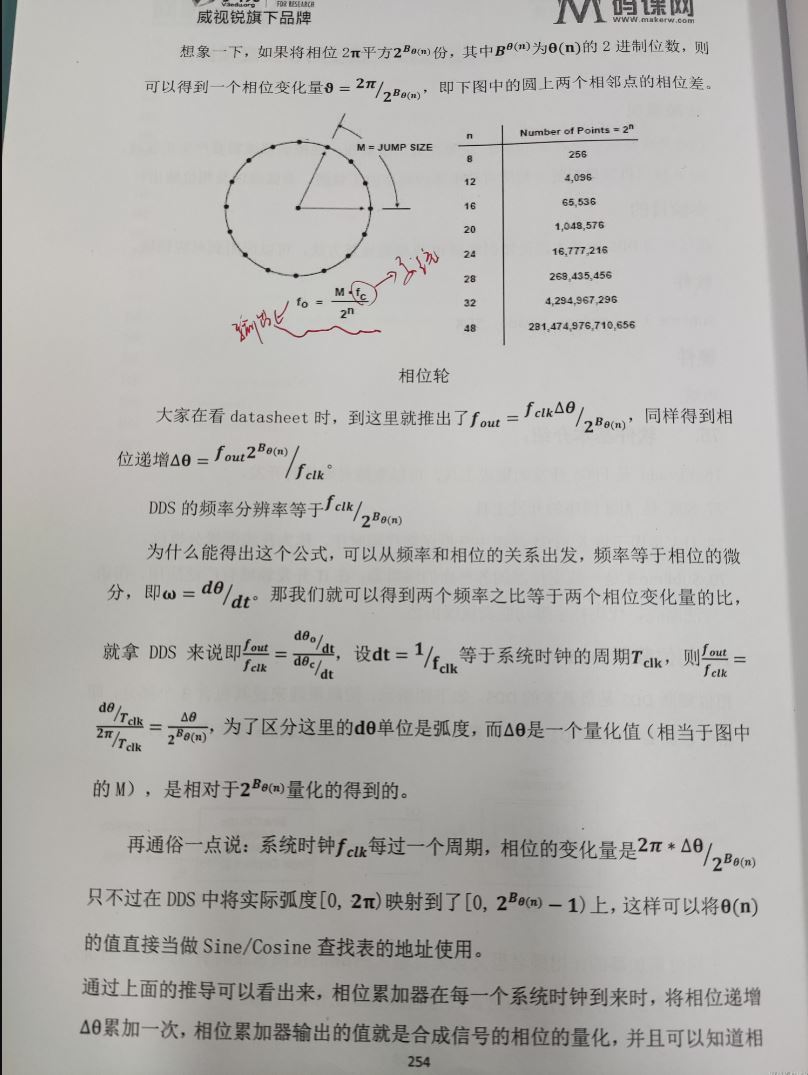

DDS技术是根据奈奎斯特取样定律,从连续信号的相位出发,将正弦信号取样,编码,量化,形成一个正弦函数表,存在EPROM中,合成时,通过改变相位累加器的频率字来改变相位增量,也就是我们所称的步长。相位增量的不同导致一个周期内取样点的不同,在时钟频率即采样频率不变的情况下,通过相位的改变来改变频率。

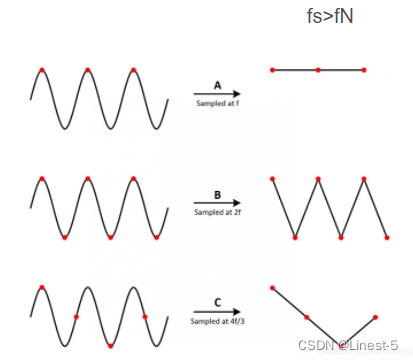

奈奎斯特采样定理:

奈奎斯特采样定理解释了采样率和所测信号频率之间的关系。阐述了采样率fs必须大于被测信号最高频率分量的2倍。该频率常常被称为奈奎斯特频率fn。

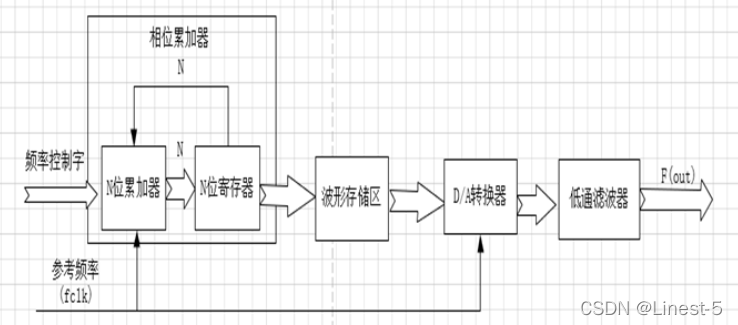

DDS的结构图:

相关参数的说明:

假设位宽为8,则可以表示2的8次方个数,就可以把一个周期的2pi分成256份,频率分成256份也就是分辨率,每一次的jump size即为每一次能够跨过几个点,即可算出输出频率的大小。

Vivado设计部分:

实验目的:用两个DDS分别产生4MHZ和5MHZ的正弦波,再用混频器IP,对两列正弦波进行混频处理,仿真看结果。

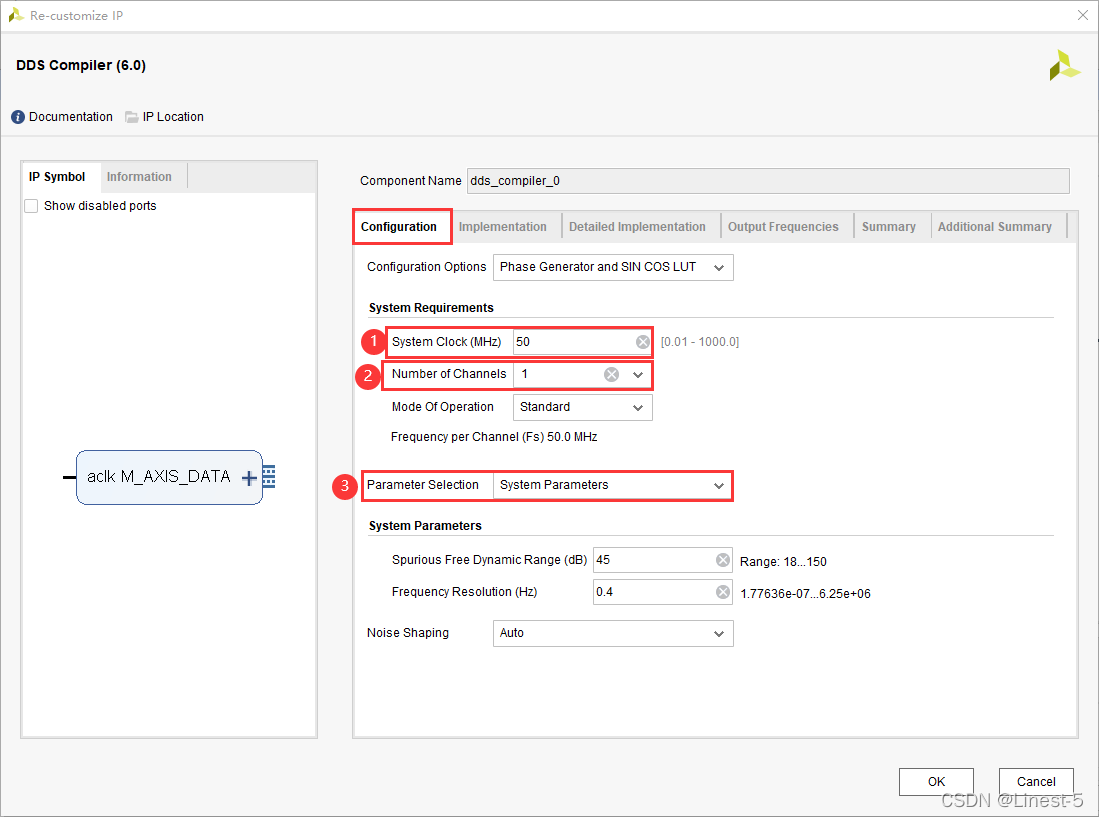

创建工程,创建新的BD,添加DDS IP核,点开DDS IP核设定其参数

①系统时钟:根据板子的时钟设定,zedboard设定为50MHZ;

②通道个数:一个;

③参数挑选:选择系统参数;

动态范围为45,计算方法:输出8位宽能表示最大为255,则其动态范围为:20*log255=48db,因此其动态范围为0-48,设定为45是可以的;

分辨率为0.4;计算方法:相位位宽为27(phase width),根据分辨率的计算方法:时钟除以2的27次方,即约等于为0.4。

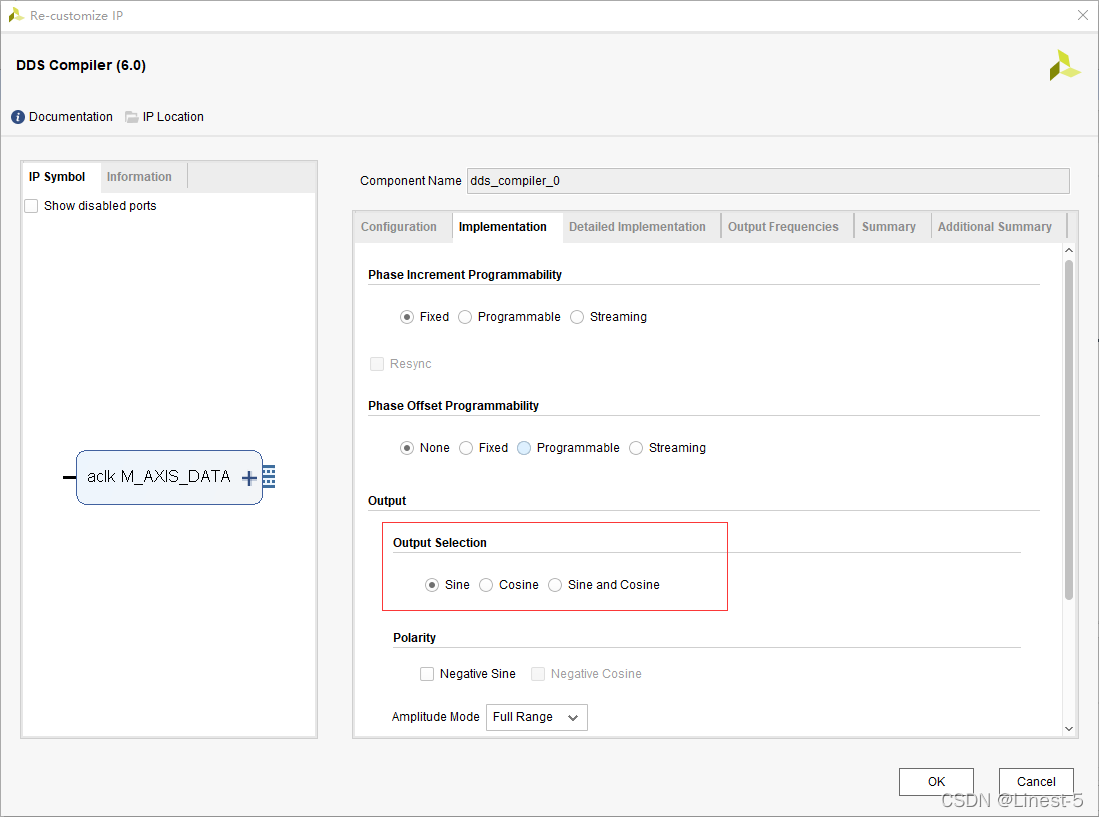

设定为正弦波。

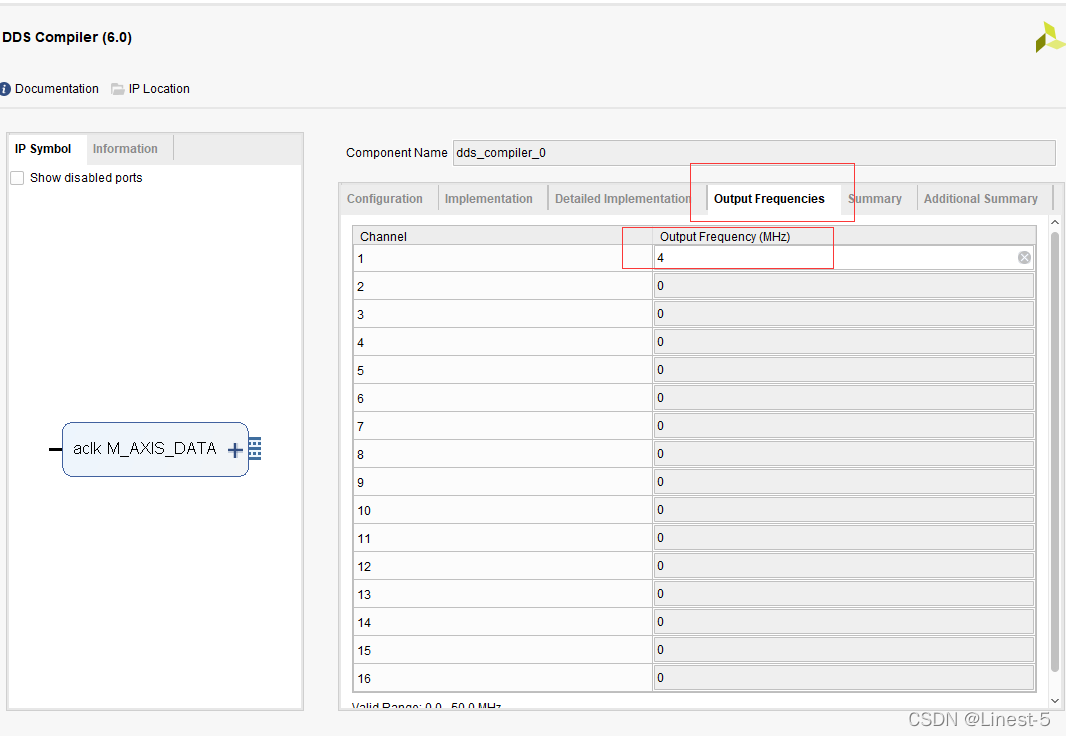

输出波频率为4MHZ。其余的参数设定保持默认即可。

同样的方法,添加一个频率为5Mhz的DDS即可,只需复制粘贴,改下频率即可。

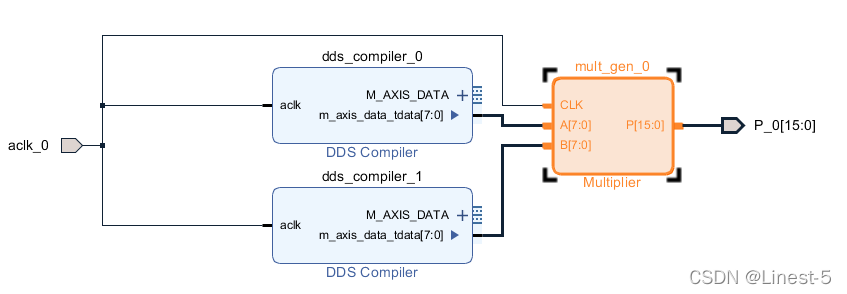

添加混频器 IP(multiplier)

设定参数:

输入选择项:

都设定为手动调整(manual),并设定为有符号的:signed,两路输入位宽都为8,使用user LUTs、speed optimized

输出和控制项:

输出位宽为0-15,共16位,其余保持默认即可。

再将对应的线连接好。如图

保存生成顶层文件。

并打开顶层文件右击模块名生成testbench文件,稍加改动保存即可。

module tb_dds_mix_wrapper();

reg clk;

initial begin

clk = 0;

forever #(10) clk = ~clk;

end

// (*NOTE*) replace reset, clock, others

//wire [7:0] M_AXIS_DATA_0_tdata;

//wire M_AXIS_DATA_0_tvalid;

wire aclk_0;

wire [15:0] P_0;

assign aclk_0 = clk;

dds_mix_wrapper inst_dds_mix_wrapper

(

//.M_AXIS_DATA_0_tdata (M_AXIS_DATA_0_tdata),

//.M_AXIS_DATA_0_tvalid (M_AXIS_DATA_0_tvalid),

.P_0(P_0),

.aclk_0 (aclk_0)

);

endmodule

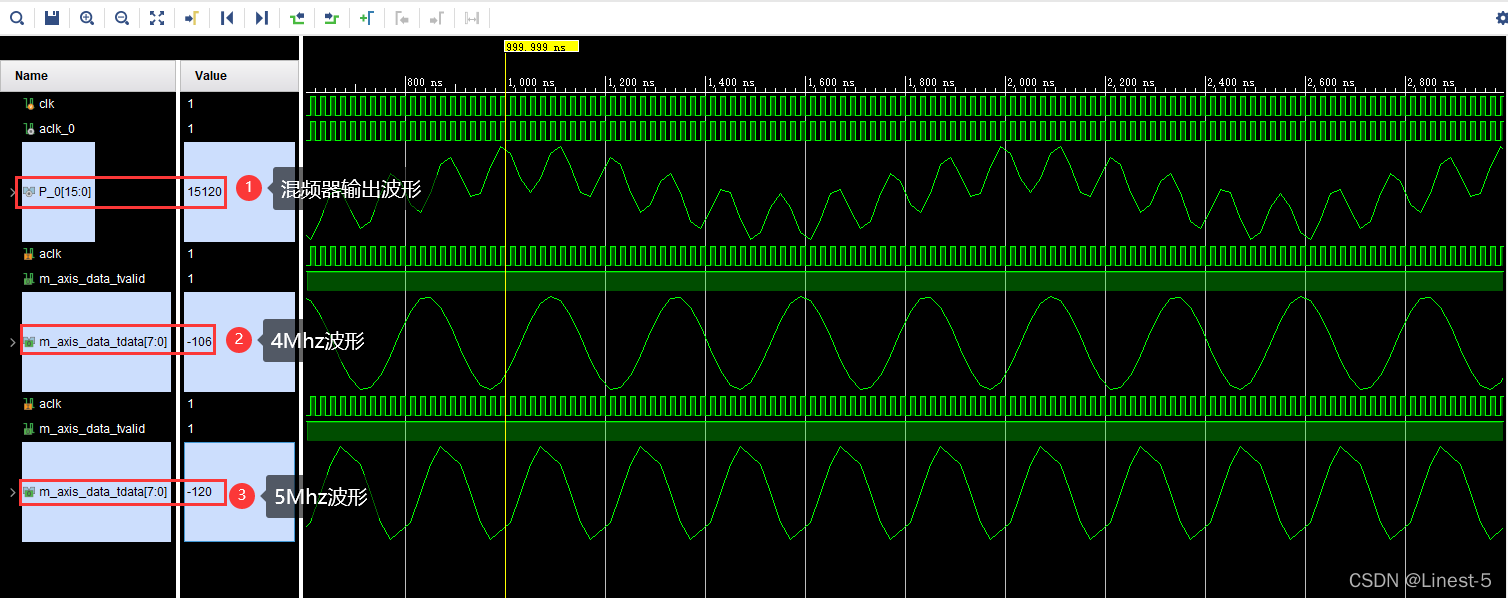

仿真环节

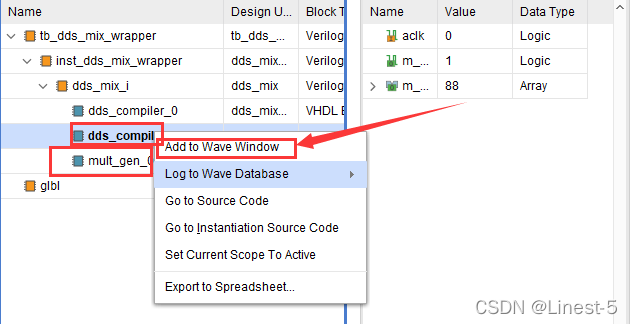

点击仿真simulation,并将两个DDS产生的波形信号添加到窗口中,找到相应的信号,右键添加到窗口中。

然后重新启动仿真,点击菜单栏上的①重新启动,如果波形不够的话,可以点击②让他多跑一会。

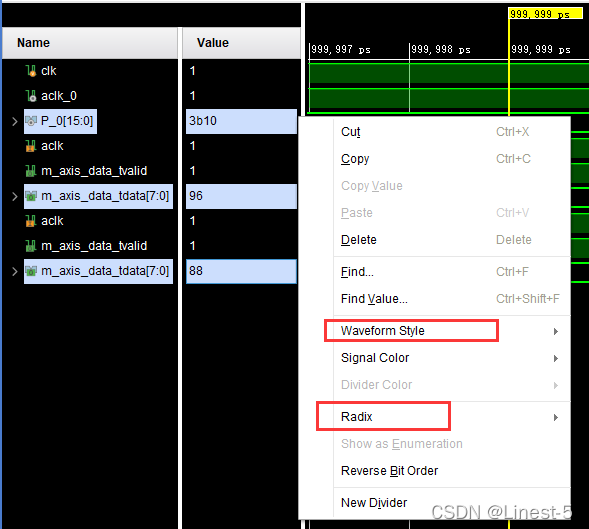

最后将三个要观察的信号改成有符号的十进制数,并且波形改成模拟信号型。

最终可以看到三列波形的对比,①位混频器输出的波形,②位4MHZDDS输出的波形,③位5MHZDDS输出的波形,可以看到放大一点的时候,有频率较大的波形,此波形位频率为两者相加即9mhz,缩小了看有频率较小的频率为两者频率相减即1mhz波形,即实现了混频仿真。