本文转载自:十年老鸟的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

前言

如果只是纯的.v文件仿真那很容易操作,主要是涉及到IP核,那么就必须要对vivado的IP核的库文件进行编译和添加了,难点也在于此。

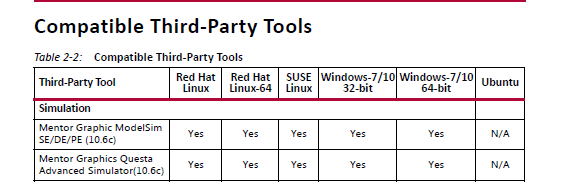

modelsim vivado 支持版本

关于版本对应,目前使用的vivado2018.2对应的modelsim版本至少应该为10.6.c

主要查ug973 文档

不过我目前使用的modeltech64_10.6d 版本,从vivado2018.2到vivado2021.2都用的好好的,所以就一直用吧,直到不能用为止了。

modelsim 编译库及连接库

在vivado 工具栏------tools------compile simulation libraires 选项框中。

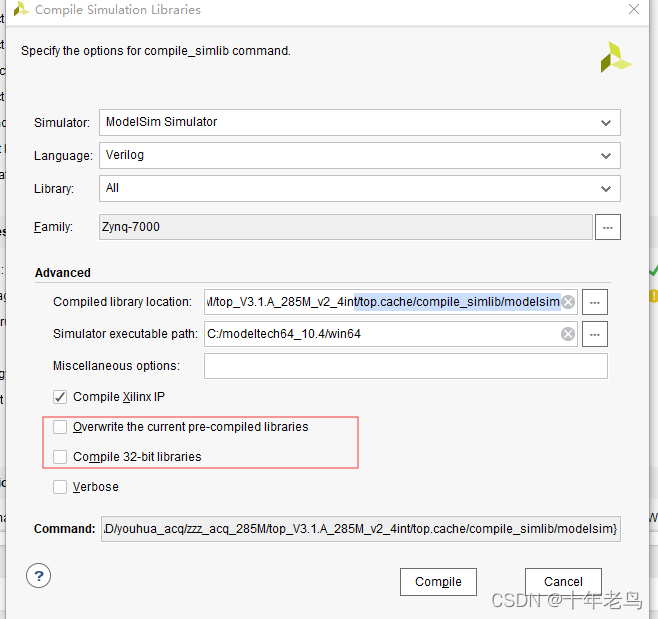

因为我们用的器件是Zynq-7000,因此可以如下设置。

主要查ug973 文档

不过我目前使用的modeltech64_10.6d 版本,从vivado2018.2到vivado2021.2都用的好好的,所以就一直用吧,直到不能用为止了。

modelsim 编译库及连接库

在vivado 工具栏------tools------compile simulation libraires 选项框中。

因为我们用的器件是Zynq-7000,因此可以如下设置。

在一个新目录中,红色方框可以不用勾选,而且现在一般都是64位的软件和电脑了

点击编译后,库文件会保存在Compiled library location中。

将modelsim文件拷贝出来,放到 modelsim安装文件夹中 (C:\modeltech64_10.6d\modelsim)

modelsim文件夹中有一个modelsim.ini配置文件,打开后将

secureip = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/secureip

unisim = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/unisim

unimacro = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/unimacro

unifast = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/unifast

。。。。。。。。。。

xfft_v9_1_0 = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/xfft_v9_1_0

xsdbs_v1_0_2 = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/xsdbs_v1_0_2

zynq_ultra_ps_e_vip_v1_0_3 = E:/NEW_BROAD/modelsim/top_V2.1.3_modelsim/top.cache/compile_simlib/modelsim/zynq_ultra_ps_e_vip_v1_0_3

这一大段复制出来。

打开C:\modeltech64_10.6d中的modelsim.ini(注意这个文件的属性是只读,修改前需改成可读写)。然后将上面复制的一段拷贝到:

secureip=$MODEL_TECH/../modelsim/secureip

unisim=$MODEL_TECH/../modelsim/unisim

unimacro=$MODEL_TECH/../modelsim/unimacro

unifast=$MODEL_TECH/../modelsim/unifast

。。。。。。

xfft_v9_1_0=$MODEL_TECH/../modelsim/xfft_v9_1_0

xsdbs_v1_0_2=$MODEL_TECH/../modelsim/xsdbs_v1_0_2

zynq_ultra_ps_e_vip_v1_0_3=$MODEL_TECH/../modelsim/zynq_ultra_ps_e_vip_v1_0_3

modelsim仿真脚本

.tcl脚本

quit -sim

set RTL_PATH E:/NEW2_BROAD/top.srcs

cd $RTL_PATH

vlib work

vmap work work

vlog -work work $RTL_PATH/sources_1/top/*.v

vlog -work work $RTL_PATH/sources_1/ip/adc_clk/adc_clk_sim_netlist.v

vlog -work work C:/Xilinx/Vivado/2016.4/data/verilog/src/glbl.v

vlog -work work $RTL_PATH/test_top_modelsim/*.v

vsim -L secureip -L simprims_ver -L unifast -L unifast_ver -L unimacro -L unimacro_ver -L unisim -L unisims_ver -voptargs="+acc" test glbl

add wave sim:/test/*

log -r *

run 1209us

do wave.do

以上有一个.v文件的编译语句,有一个IP核的编译语句,xilinx的IP核编译库还是很好用的

某些个别IP找不到库文件怎么办

有些复杂一点的IP没有*_sim_netlist.v文件怎么办呢。我们可以首先在vivado上直接关联modelsim,在vivado打开modelsim进行仿真。打开的时候modelsim的tcl窗口会记录一切操作,把这些操作用到自己的tcl脚本上就可以了。