本文转载自:FPGA技术实战的CSDN博客

前言

在数字信号处理时我们经常会用到数字变频,包数字下变频(DDC)和数字上变频(DUC),这其中会用到Xilinx公司的DDS IP核或者Altera公司的NCO IP核来产生本振频率,以现数字域信号频谱搬移。本文我们通过例化Xilinx公司的DDS IP核来产生混频器本振输入频率,并给出Modelsim仿真测试结果。

1、Xilinx DDS IP简介

Xilinx公司的DDS IP核使用AXI4接口实现高性能、优化的相位产生和正弦波电路。

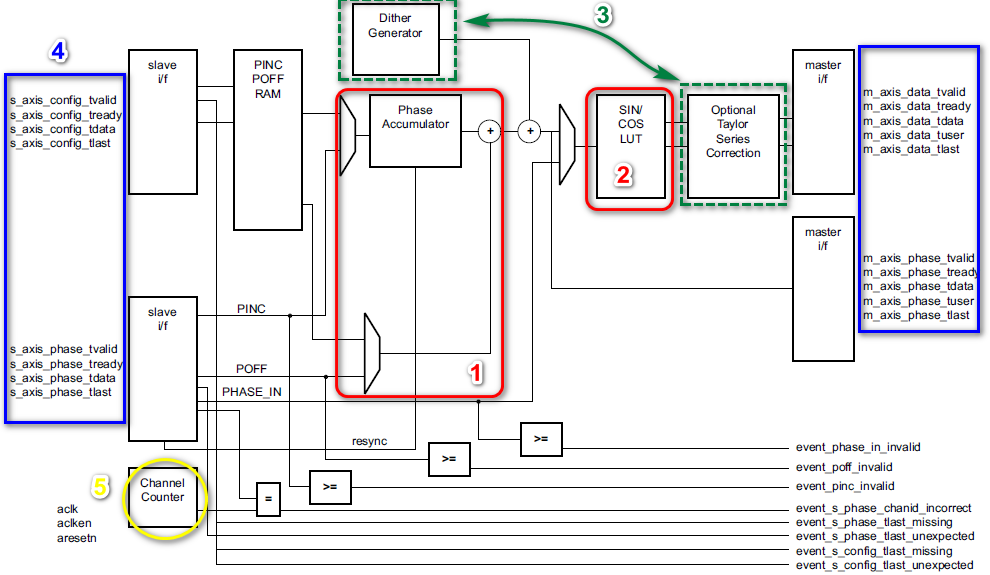

图1、DDS IP核架构

在图1中我们看到DDS IP核主要包括5部分组成,其中DDS核心为相位累加器(标记1所示)和LUT查找表(标记2所示)。相位累加器实现查找表地址的产生,LUT查找表用来存储输出波形。图1标记3部分为抖动产生器和泰勒级数矫正产生模块,主要用来改善SFDR,两者改善的效果、使用的逻辑资源存在差异。标记4部分则为AXI4接口,实现相位累加字配置,多通道配置,相位累加器输出和波形数据输出。标记5部分则在多通道DDS输出时使用。 DDS IP核可以配置为三种模式:相位产生器、SIN/COS LUT或者相位累加器和SIN/COS LUT(即DDS)。

2、DDS IP核工程例程及仿真测试

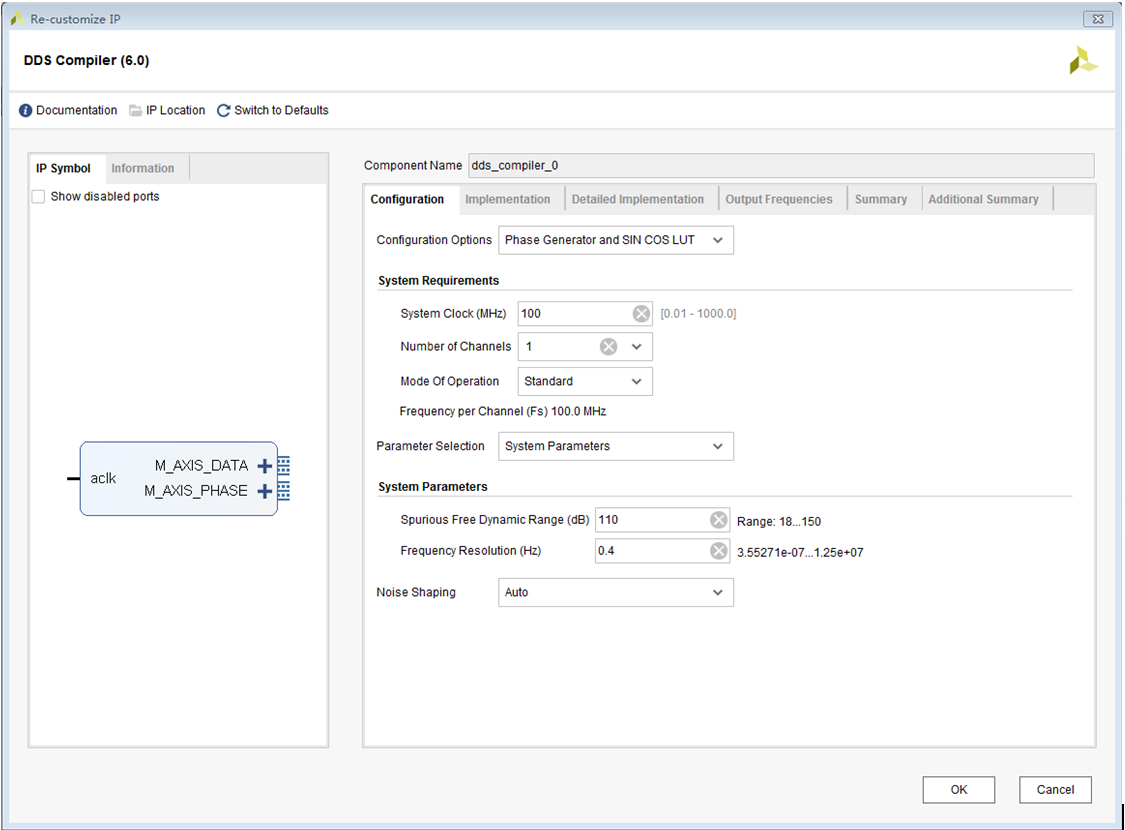

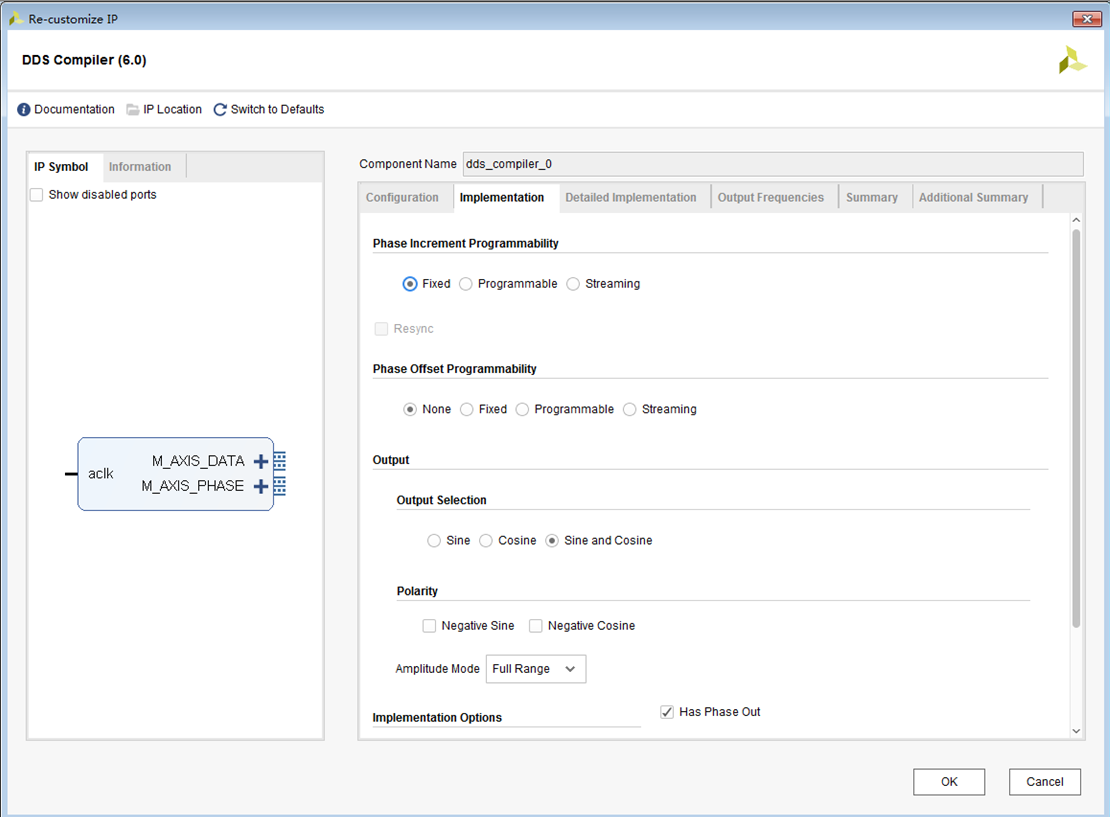

本例程例化两个IP,一个实现单通道DDS输出,一个实现4通道DDS输出,用于对比测试单通道和多通道DDS IP差异以及了解如何进行参数配置。参数配置表如下所示。

|IP核模式 | 系统时钟 | SFDR | 频率分辨率 | 输出频率 | 相位累加器 |

| 单通道 | 100MHz | 110dB | 0.4Hz | 1MHz | Fixed |

| 四通道 | 100MHz | 110dB | 0.4Hz | 1MHz | Programable |

2.1 单通道DDS IP核参数配置

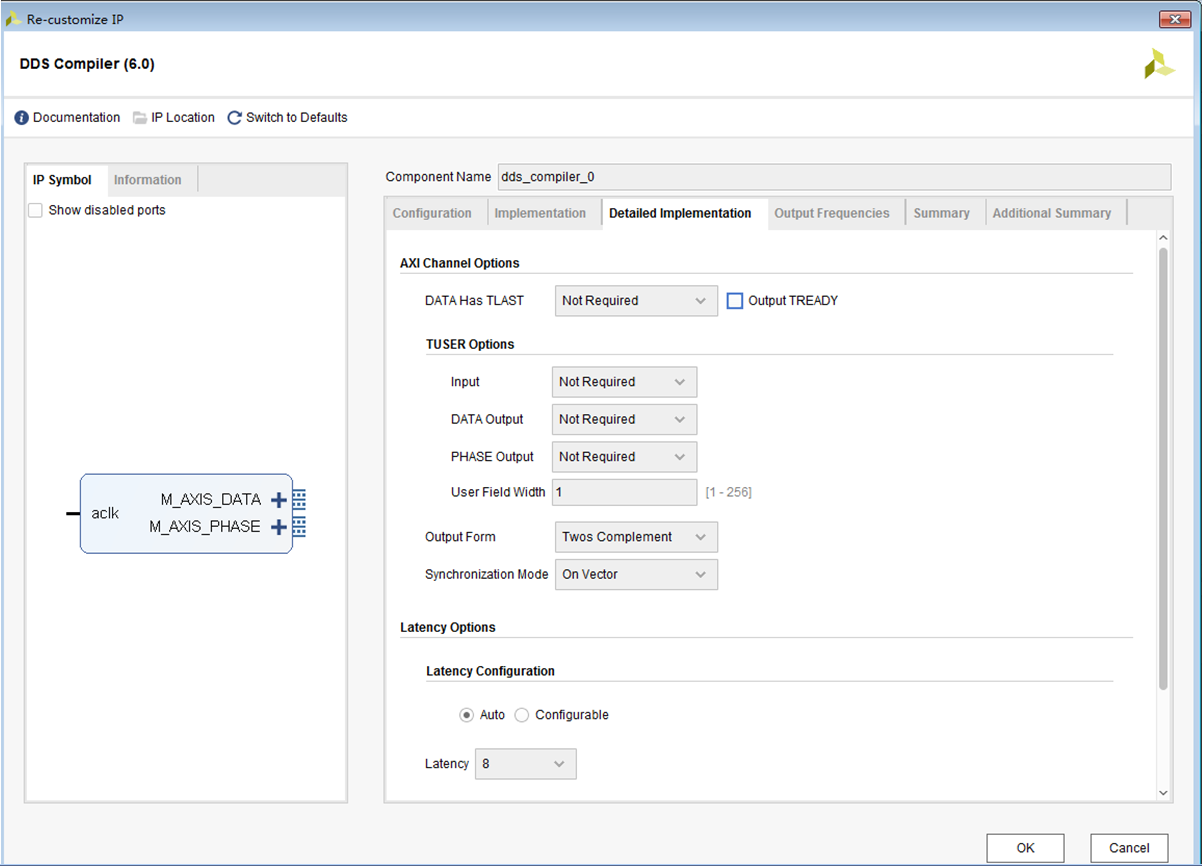

图2

图3

图4

图5

图6

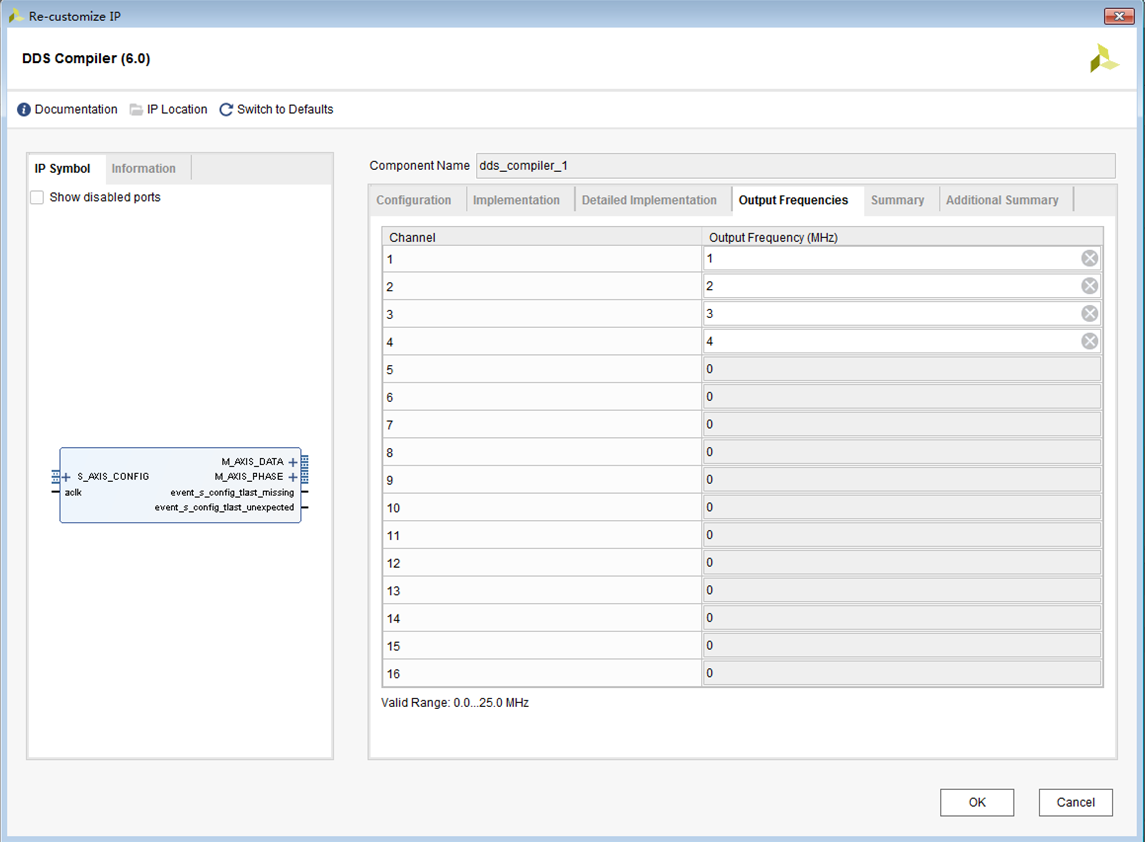

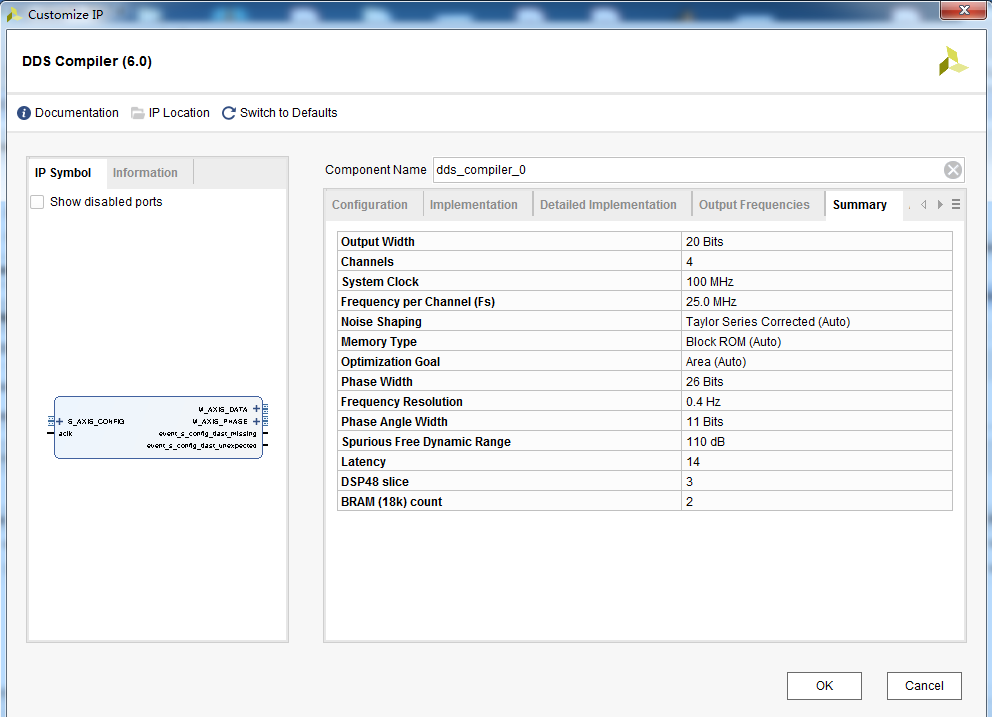

2.2 四通道DDS IP核参数配置

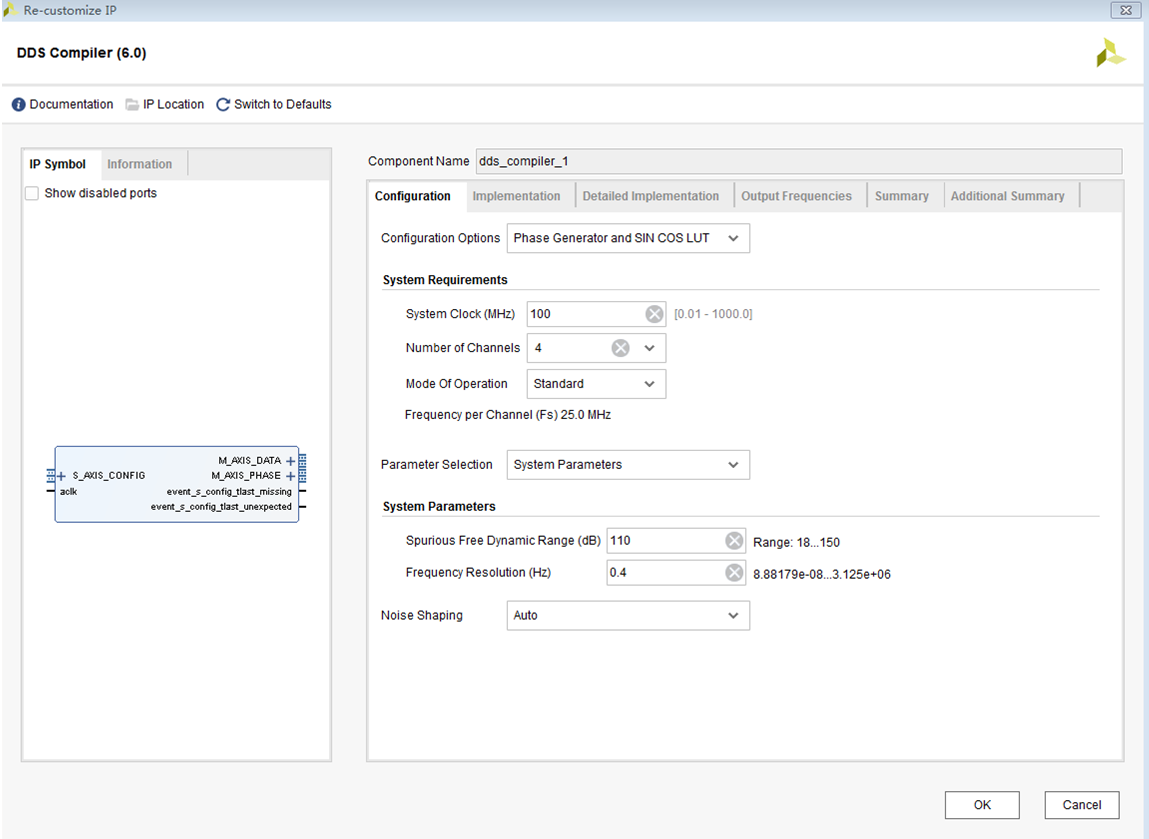

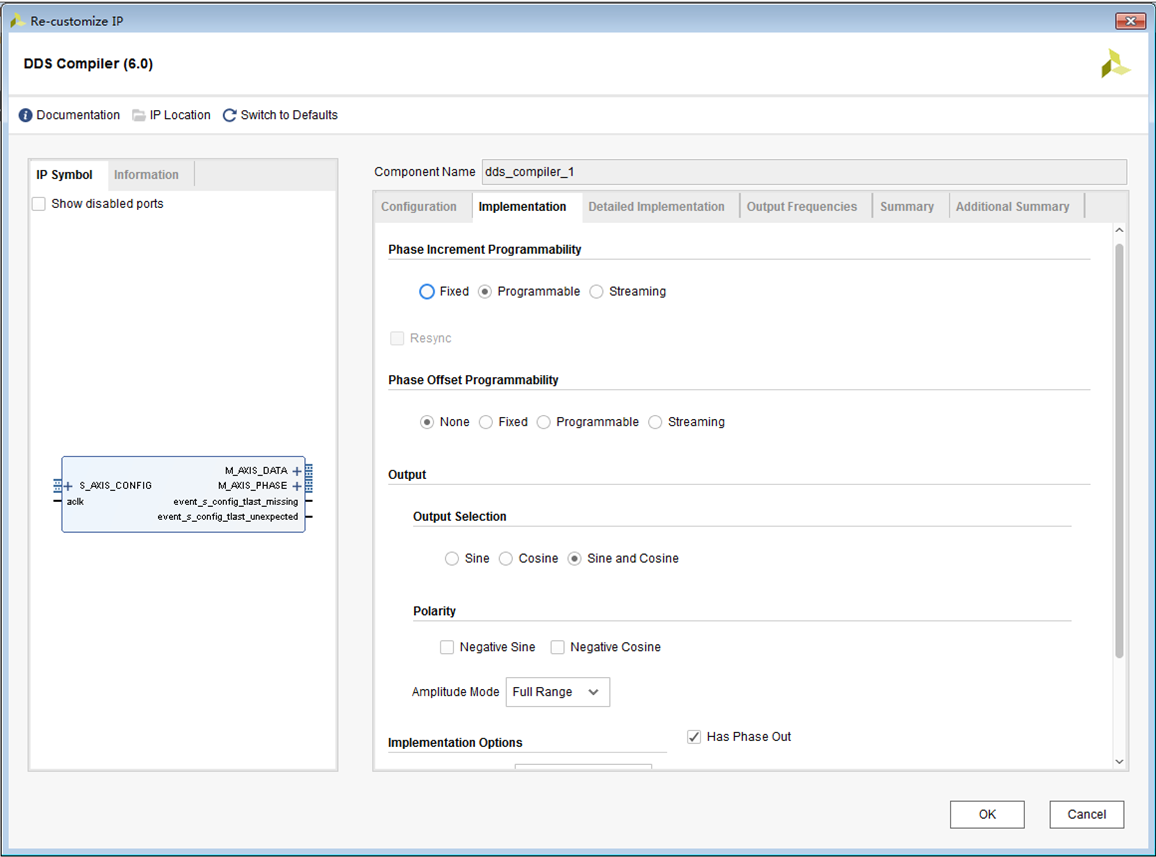

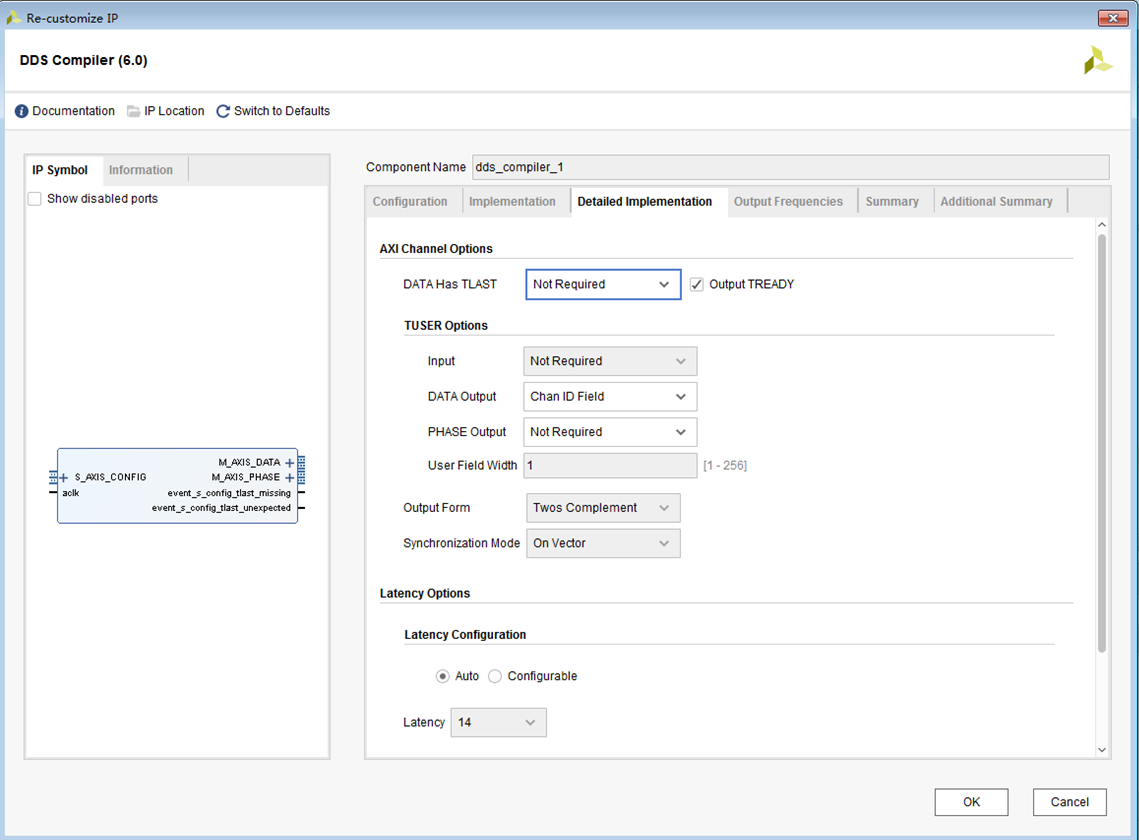

图7

图8

图9

图10

图11

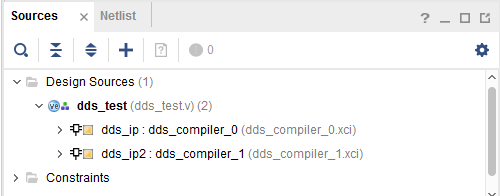

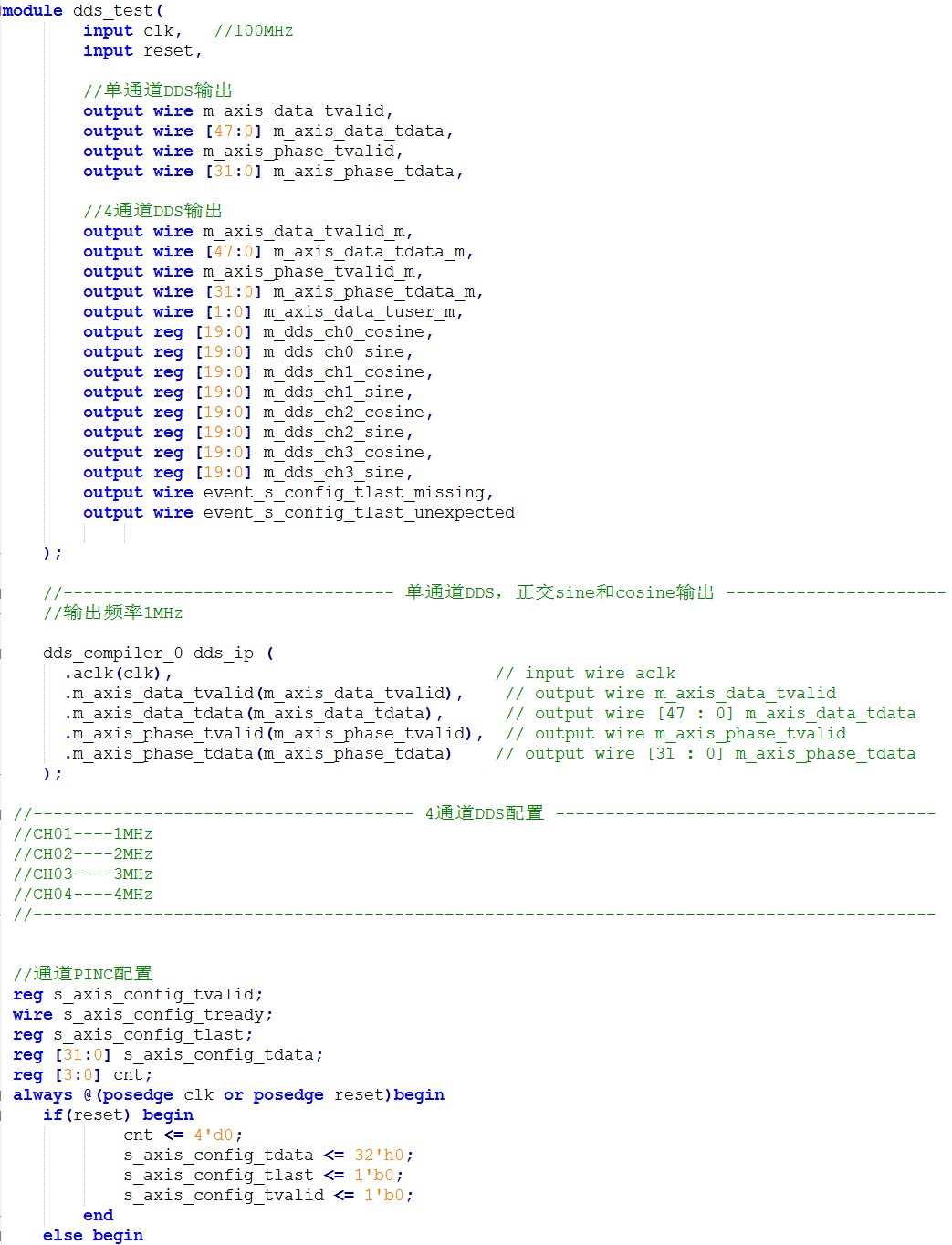

2.3 Vivado 工程建立及FPGA代码编写

DDS测试FPGA工程结构及部分代码如图11、12所示。

图12、DDS工程结构

图13

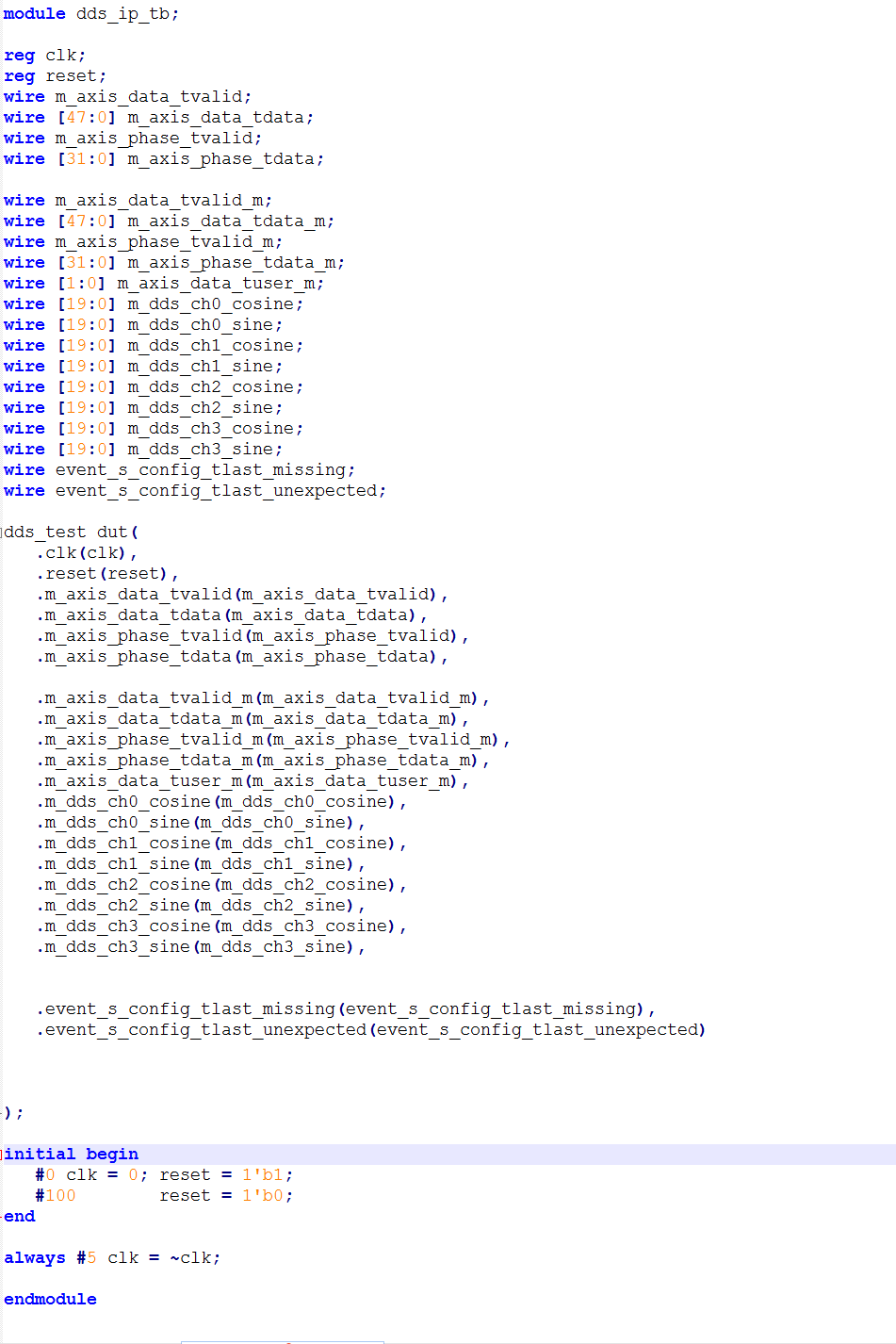

2.4 Vivado仿真测试文件编写

仿真文件代码编写

图14、仿真测试文件代码

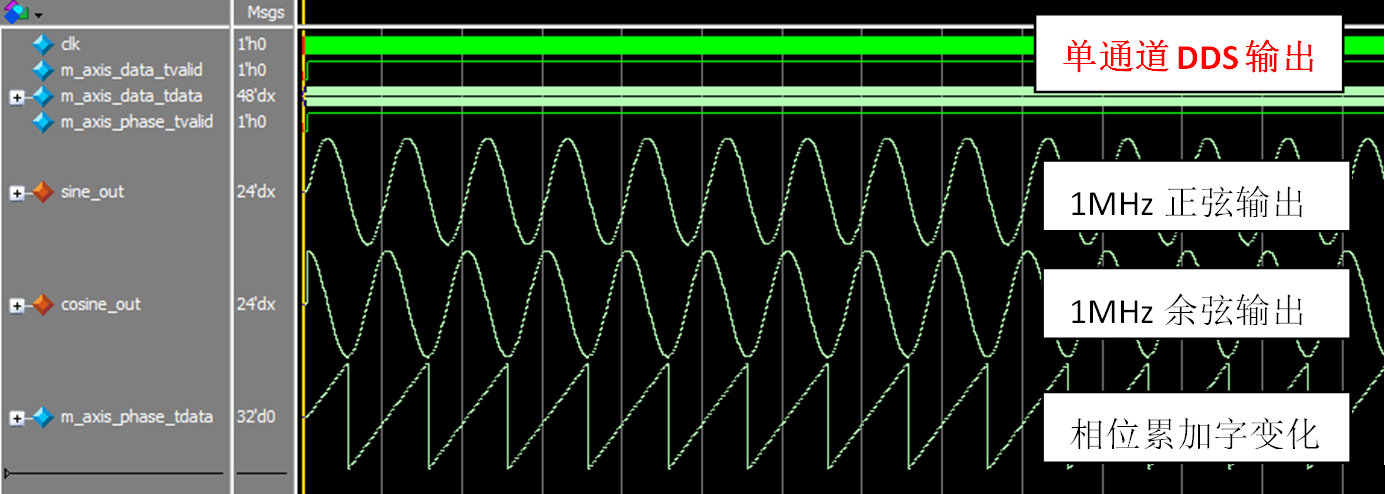

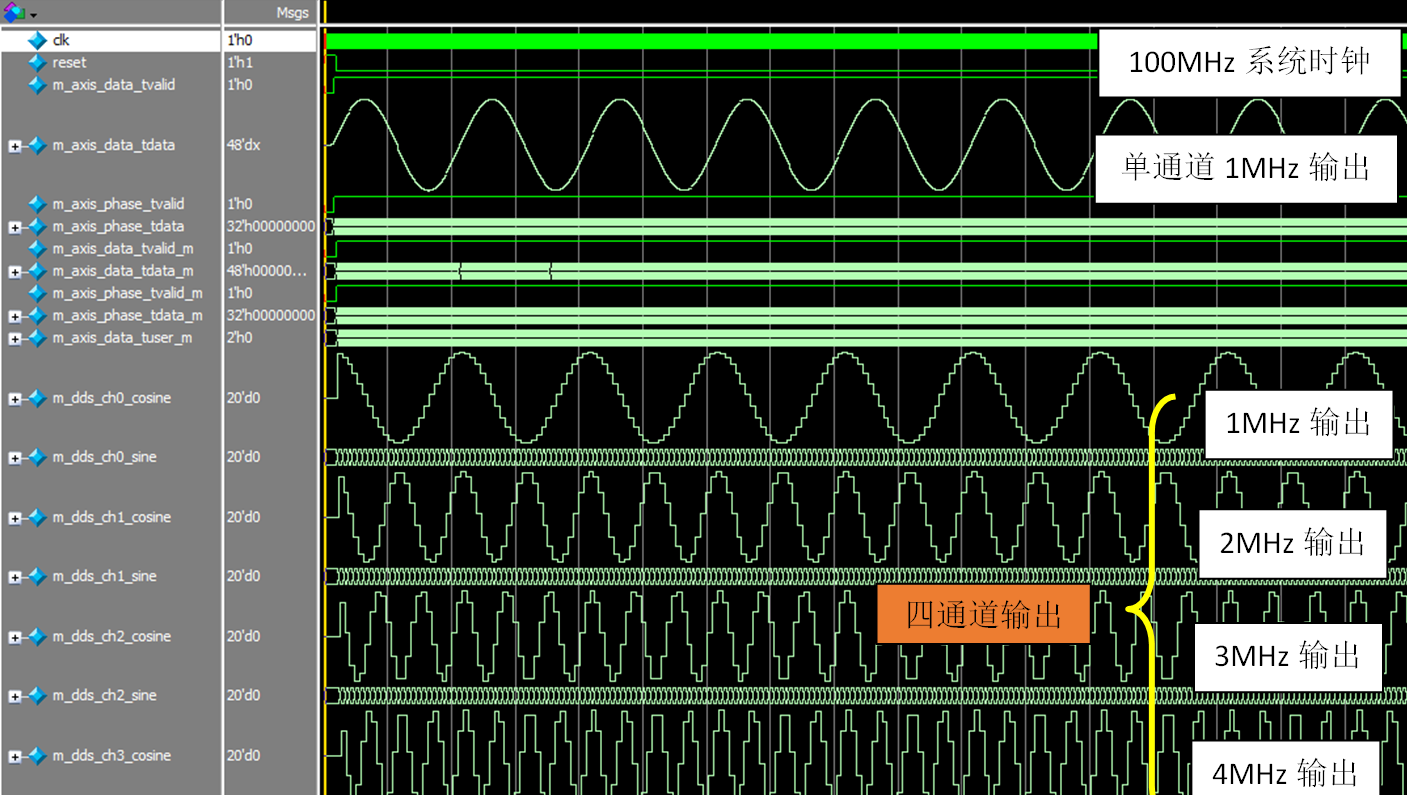

2.5 Modelsim仿真测试

利用Modelsim软件联合Vivado软件仿真,测试结果如图所示。

图15、 单通DDS输出

图16、多通道DDS配置字时序

图17、四通道DDS波形输出

3、总结

Xilinx DDS核经常在数字变频及软件无线电调制解调中应用,我们可以利用IP核来实现,也完全可以自己编写HDL语言来实现复杂波形的产生。对于DDS的实现原理,网络有非常丰富的资料可以查找学习,本文不再详细阐述。