本文转载自: FPGA的现今未微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

最近看到很多人问FPGA如何入门,或者如何学习的问题,突然想起自己刚工作的时候,部门的培养还是做的很不错的,这里把记忆中的东西拿出来分享下,希望对大家有帮助。

对于新人来说,FPGA的学习需要了解的东西还是非常多的,大而杂的学习效果往往不是特别的好,对如初学者来说,FPGA的入门大体可以分成如下几个方面:语言、器件、方案、仿真、编译、上板调试。这里分别介绍下应该如何入门。

语言

会Verilog还是VHDL不重要,如果没有基础上的话,就还是学Verilog吧,因为在国内,这个还是用的多。学习资源只需要2个。

第一个就是随便找一本介绍Verilog语法的书看看,先对Verilog有一个基本的了解,这个阶段最多花1个星期,一般看书的前几章节就好了。

第二个资料就是IEEE发布的规范(备选),这个更多是一个工具书,有需要的时候去查,或者想对某个点有更深入的了解的时候看看,不需要花太多时间。

器件

FPGA器件那么多,不同器件之间还有一些差异,不可能对所有的器件都了解地非常清楚,但是不管什么器件,它们都有一些公共的基础单元,初学者了解这些基础单元就足够了,这些基础单元包括LUT、reg、RAM、DSP等。如果你手上有板子,那你就了解板子上的这款FPGA就好。如果没有,任选一个也行,比如Xilinx的VU9P,intel的Stratcs 10。资料就是你选定的这款FPGA的user guide,重点看里面关于这些基础单元的介绍即可。

这部分学习的过程是枯燥的,没有感觉的,有很多不懂也是正常的,这一步主要是为后续打基础,得到后续需要编译一个工程的时候,就可以看看这些基本单元是什么样子的,在FPGA的什么位置,对器件的了解也会更加深刻。这部分内容最多花1个星期的时间。

方案

在这个阶段,你Verilog学会了,器件也了解点点了,就可以开始动手写写代码了,那写什么了?这是本文的重点,我们要达到2个目的,第一个是对verilog语言的熟练运用,第二个就是有实际意义,即后续项目中会用到。没有实际意义的练习题,不是很建议大家花时间去做。

我们知道,无论多复杂的建筑,都是由砖、钢筋、水泥等巧妙地组合而成。FPGA设计也一样,无论多复杂的FPGA设计,也是由一些基本单元组合而成,初学者把这些基本单元吃透了,后续的项目也就游刃有余了。这里把基本单元以题目的形式出现,初学者先编码完成下面的题目,每个题目都是一个完整的module。

一、边沿检测电路

题目如下,采用Verilog编码:

1、对一个任意输入的信号,分别检测上升沿、下降沿、双沿,以组合逻辑的形式输出一个脉冲。

2、对一个任意输入的信号,分别检测上升沿、下降沿、双沿,以时序逻辑的形式输出一个脉冲。

这个题目除了了解边沿检测电路外,还有就是了解组合逻辑输出和时序逻辑输出的不同。这个题目其实比较简单,初学者建议花1天时间即可。

二、计数器

计数器是FPGA设计中非常非常非常重要的一个组件,应用形式也非常的多样,这里选择几个典型场景,建议初学者花2天时间完成。

1、设计一个计数器,从0-7不停计数;

2、设计一个计数器,从1-6不停计数,即从1开始计数,计到6以后又回到1;

3、设计一个计数器,对输入的信号进行计数,并通过单脉冲的形式输出这个输入信号的长度(cycle数);

4、设计一个计数器,当外部有一个脉冲输入的时候,开始计数,从1计数到6,计数完成后保持计数器的值,等到下一个输入脉冲后重新开始计数。

计数器的输入输出接口可以自己定义,重点在计数器的理解。

三、选择、译码器

选择器和译码器也是常用的逻辑,大学数字电路就已经学过了,这里主要是了解verilog语言是如何实现的,花1天时间足够了。

1、有输入d0、d1……d7,sel[3:0],设计一个8选1的多路选择器,根据sel的值选择对应的dn;

2、输入din、sel[2:0],输出dout0、dout1、……、dout7,选择一个电路,根据sel值,将din送到对应的doutn输出;

四、分频器

分频器在实际应用中不是说对时钟进行分频,往往是对“数据信号”进行分频,在数据采样的时候用的比较多。这部分内容花1-2天时间即可。

1、假定输入时钟100M,输出一个4分频信号,即输出一个25M的时钟,且占空比为1:1;

2、假定输入时钟100M,输出一个5分频信号,即输出一个20M的时钟,对占空比无要求;

六、状态机

状态机在逻辑设计中是应用非常广泛的一个组件,作为初学者,一般都是从序列检测器开始。

1、假定有一个1bit的输入信号,当检测到该输入信号为“01101101”的时候输出一个脉冲。这个题花2天时间即可。

七、RAM

RAM是FPGA器件中的基本单元,首先要了解RAM的结构,再开始如下的练习。

1、生成一个深度为512,宽度为32的简单双口RAM;

2、对RAM进行读写操作,即把0-255这256个数据连续写入RAM,然后立马连续读出来。比如写入0后立马读出0这个数据。

这部分内容建议花1个星期的时间,3天时间了解RAM,资料还是以user guide为主,4天时间完成练习。

八、FIFO

FIFO同RAM一样,也是在设计中常用的基本单元,FIFO的实现常用2种,一种是例化供应商提供的IP,一种是通过RAM自己搭建,学习阶段,采用第二种方式。这部分内容是FPGA设计的重点,建议花2个星期的时间,每个题目用1个星期时间完成。

1、利用RAM,搭建一个同步FIFO,宽度为32,深度为512,将空水限位4,将满水限位480,外部接口信号包括时钟、读写使能、读写数据、空和将空、满和将满、FIFO内已写入数据单元的个数。

2、利用RAM,搭建一个异步FIFO,宽度为32,深度为512,写时钟为150M,读时钟为50M,将空水限位4,将满水限位480,外部接口信号包括时钟、读写使能、读写数据、空和将空、满和将满。这个题目比较有难度,完成了这个题目,相信对异步FIFO的实现会有深刻的认识。

接口时序参考如下:

九、调度

调度FPGA设计中的重点和难点,尤其是多队列的调度,对于初学者从2队列的调度入手即可。这部分内容花1个星期的时间即可。

1、如下图所示,2个FIFO存放报文,报文长度不超过256byte,要求通过RR调度的方式,将2个FIFO中的报文读出。A、B、C三个接口时序相同,如下图所示:

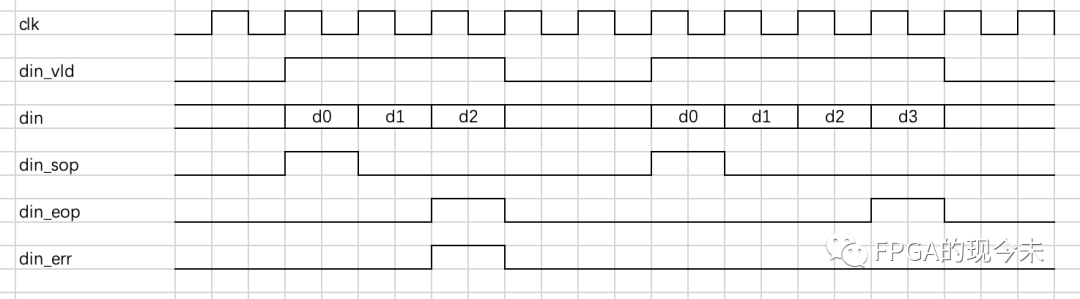

十、丢包逻辑

最后再来一个综合性的练习,丢包逻辑的设计,假定输入端口是连续不断的报文,报文的长度不超过256个cycle,每个报文的最后一个cycle有一个标记,为1表示该报文要丢弃,为0则输出该报文。输入侧接口信号包括,din_vld、din、din_sop(表示数据的第一拍位置)、din_eop(表示数据的最后一拍的位置)、din_err(只在最后一拍有效,表示输入报文是否要丢弃),报文输入接口时序如下,这个题目建议花2个星期的时间完成。

到这里,如果上面的题目都已经很好的完成了,那么恭喜你,已经入门6层了,相信对FPGA的基础设计也有了一些基本的认识。

仿真

做了一个开发人员,不能仅仅是设计,还需要对自己的设计结果负责,即保证自己的设计是没有问题的,那就需要仿真。PS:这里说的仿真是指开发对自己所写 模块的单元仿真。

在这个步骤,给上面的每一个题目(确保每个题目都是一个module)搭建一个小的仿真平台进行仿真,一来熟悉了解仿真的步骤,二来找出自己设计的bug并修正,在这个过程中进一步理解上述基本单元的设计。开发人员具体如何做仿真,网上有很多资料可以查看,后续再做一个总结,这里现不赘述。

编译

到这一步,你完成了上面的所有编码和仿真,保证了代码的正确性,再选择前面了解的器件,用供应商的工具环境中开始实际的编译综合,一来保证代码的正确性,二来熟悉下综合工具的使用。通过上述具体的例子,你会对编码和工具有更进一步的理解。这一步主要学习3个内容:

第一个就是熟悉工具的使用,比如vivado和quartus;

第二个就是消除warning或者error,即会简单的排错;

第三个就是布局布线完成后,看看资源报告,时序报告,看看你设计逻辑在FPGA里是一个什么样子?比如边沿检测电路是怎么实现的?FIFO在FPGA内是一个什么样子的?

这一步的学习,主要还是参考工具的user guide,以及官方的各种文档。

上板调试

这一步不是每个人都有条件,如果你手上有块板子,那就按照板子的教程或者示例,自己做一些小东西后调试。

如果你没有板子,也不用着急,最后这一步先保留,待到后续工作中有调试机会了,再去实践。

总结,本文基于某设备大厂FPGA新员工以前的培养计划做的一个总结,希望对想学习FPGA或者刚入门的朋友有点点帮助,有意义的实践是最好的学习。