版权声明:本文为CSDN博主「尤老师FPGA」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_38828382/article/details/116526633

Vivado hls工具与Vitis统一软件平台的出现和发展,突破了以往使用FPGA进行设计时,使用语言HDL语言进行设计实现的瓶颈,在xilinx FPGA上构建数字系统时,首先使用c/c++/systemc语言进行建模, 然后通过HLS工具将c/c++/system c模型描述直接转换为RTL级的HDL描述,因此大大提高了FPGA设计效率,加速FPGA在高性能信号处理领域的应用与推广。

Modelsim 工具可以进行RTL的建模仿真可以配合Vivado和vivado Hls进行仿真。这里提供一个可以与Vivado2019.2支持使用的Modelsim,版本为10.7。

Modelsim

一、 Modelsim

(1)、以管理员身份运行如下安装程序

(2)、按照截图设置安装选项,设置安装目录

同意安装即可

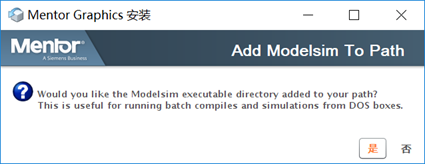

(3)、两个弹窗点击确认

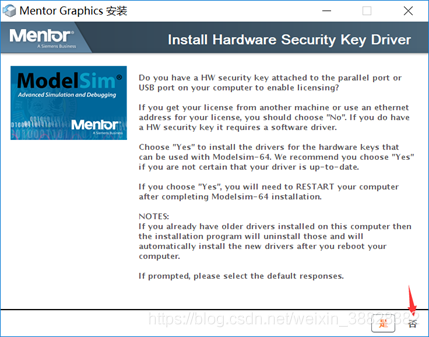

(4)、硬件KEY 选择否,这里不用安装

(5)、完成

二、 Modelsim 软件破解

(1)、复制如下文件到->modelsim安装目录win64下

(2)、双击运行patch64_dll.bat

跳出如下license.txt文件

点击文件另存为一个中文目录下,记住这个目录

我这里另存到如下目录

保存后,关闭文本文件和CMD窗口

(3)、设置环境变量

右键我的电脑->属性->高级系统设置->环境变量->用户环境变量设置如下值(变量值要设置自己的LICENSE安装目录)

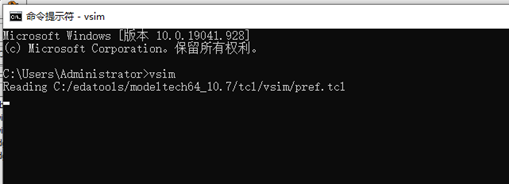

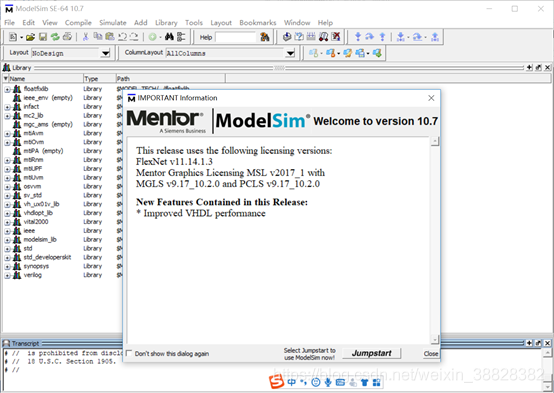

(3)、测试Modelsim 是否安装成功

打开开始->运行->CMD命令行 输入vsim

如果弹出modelsim 工具并且没有提示license错误表示破解成功

译仿真库

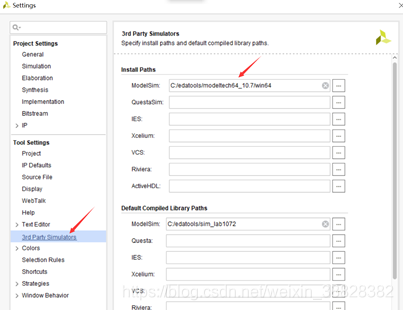

(1)、打开vivado 软件,点击Tools->Settings:

这里modelsim必须是10.7或者更新版本

(2)、设置modelsim 安装路径

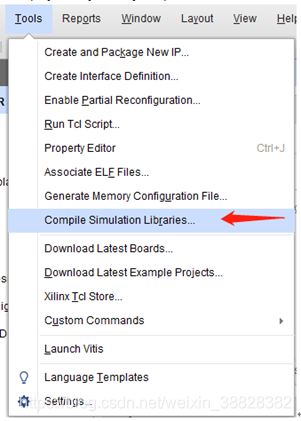

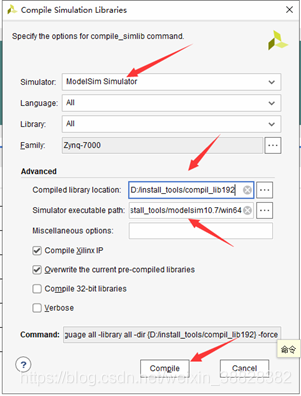

(3)、编译库启动工具,设置modelsim编译库相关选项

(4)、编译完成,查看结果

编译库结果无错即可,有警告没关系