版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_44788470/article/details/119584306

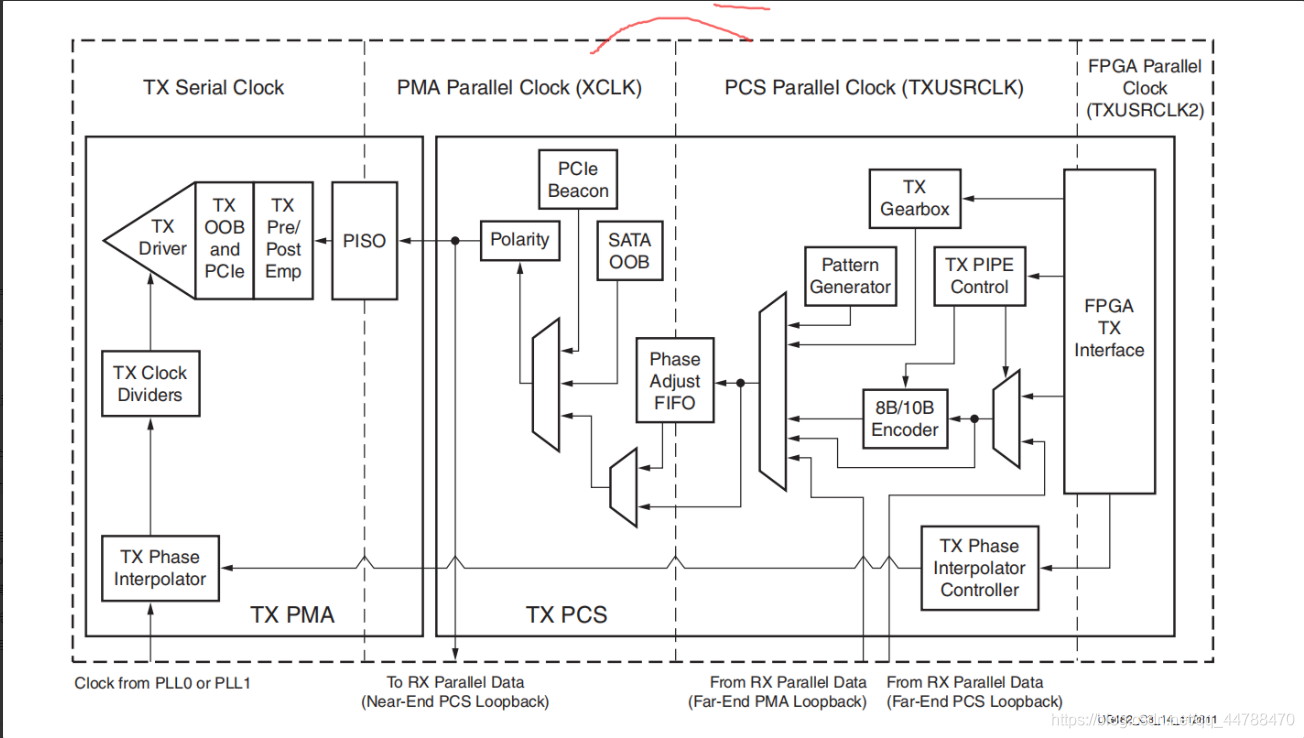

FPGA TX Interface by GTP UG482

FPGA TX的交互方式是 FPGA通过GTP收发器的TX数据路径,应用发送数据通过GTP收发器写数据到TXDATA端口在TXUSRCLK2的上升沿的时候。端口的位宽可以被配置成2或者4字节。实际的尾矿取决于TX_DATA_WIDTH的属性和8B10B使能端口的设置。 端口宽度可以是16,20,32,40bits。TXUSRCLK2的时钟速率由TX line rate决定。 第二个时钟(TXUSRCLK)一定要提供给发送器内部PCS的逻辑。

FPGA交互的数据宽度可以通过配置TX_DATA_WIDTH这个的属性来设置。当使能8B10B编码时,TX_dATA_WIDTH一定要设置成20bit 或者40bit。 当8B/10B编码旁路时, TXCHARDISPMODE和TXCHARDISPVAL作为DATA的数据位。(TXCHARDISMODE和TXCHARDISVAL只有没有8B/10B使能的时候作为数据位使用)

(然后就是在8B/10B使能时,作为极性判断使用)

TXCHARDISPMODE 专注极性是高还是低,而TXCHARDISPVAL提供极性控制。

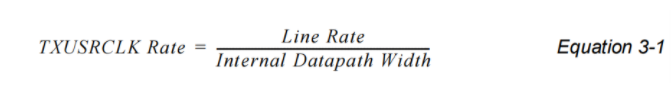

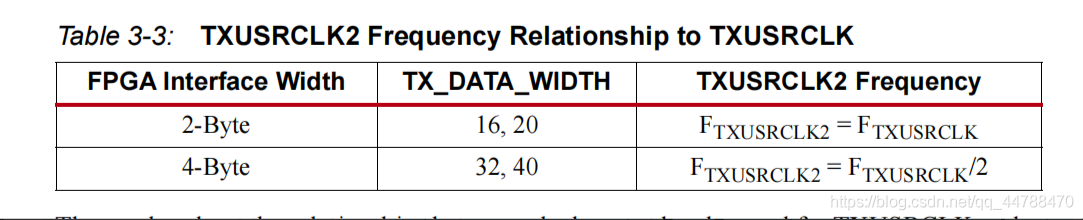

FPGA TX交互包含两个时钟:TXUSRCLK 和TXUSRCLK2。TXUSRCLK是内部时钟给PCS逻辑在GTP收发器中的工作时钟,。它的速率由GTPE2_CHANNEL内部数据宽度和GTP收发器的TX的链路速率决定。

Equation3-1为 TXUSRCLK Rate的速率计算

TXUSRCLK2是主要的同步时钟给所有进入GTP收发器TX端的信号。 大多数进入GTP发送端的信号被采样在TXUSRCLK2的上升沿。TXUSRCLK2和TXUSRCLK由固定的关系基于,TX_DATA_WIDTH的设置。

TXUSRCLK和TXUSRCLK2的关系:1,TXUSRCLK和TXUSRCLK2一定上升沿对齐,两者尽可能的少一些延时,低延时时钟资源(BUFG和BUFHs)应该使用驱动 TXUSRCLK和TXUSRCLK2。尽管它们可能工作在不同频率,发送器的参考时钟一定要来至相同的晶振。因此TXYSRCLK和TXUSRCLK2一定是发送器参考时钟的倍数或者分频。

TXOUCLK 可以驱动TXUSRCLK 和TXUSRCLK2, 在4bytes模式下 要先通过MMCM或者PLL才能驱动TXUSRCLK和TXUSRCLK2。

TX 8B/10B

TX8B/10B的。在多出的2个bits是为了直流均衡和为了更好的时钟恢复。 GTP有一个8B/10B TXPath不占用任何FPGA的资源,使能8B/10B编码器会增加TX路径的延时。 GTP收发器总是最先发送最右边的bit位。

为了使能8B/10B编码器,TXB10BEN必须拉高。TX8B/10B编码器允许字节交错,且绕过编码器。当TX8B10B拉低,所有编码器是关闭的且没有数据来至TXDATA可以被编码。当TX8B10BEN是拉高的时,可以通过TX8B10BBYPASS的控制来,相应字节通道绕过8B10B编码,当Encoder是关闭的,TXDATA端口可以直接描述FPGA TX的交互。

TX Gearbox: Tx 变速器提供2字节和4字节的交互,数据的加扰是完成的在FPGA内部逻辑

一些高速协议支持64B/66B协议 因为8B/10B带来的开销十分的大。

当TX Gearbox执行64B/66B编码器时且使用了2bytes。输入包含两个头bit和16bit数据,在第一个周期时,the header bit 和14bit的数据输出从TX Gearbox,在第二个周期仍然有两个数据bit在先前的周期TXDATA中和14bit数据在当前TXDATA输入到TX Gearbox中,第三个周期第四个周期也一样,在第五个周期时,TX Gearbo输出包含2个数据bit从第一个66bit BLOCK。第二个66bit快的头和28bit数据来至第二个66-bit 块。

GTP收发器的 TX变速器仅仅支持外部序列计数器模式,这一定要在用户逻辑中被执行,TX变速器提供2bytes和4bytes交互在FPGA逻辑。

外部序列计数器工作模式使用TXSEQUENCE【6:0】 ,TXDATA[31:0],and TXHEADER【2:0】inputs,一个bit计数器一定要存在在用户逻辑中去驱动TXSEQUENCE端口,在64B/66B编码器中,计数器 增加0-32然后重新重0开始,64B/67B中计数器从0-66自增然后从0开始,当使用64B/66B编码,TXSQUENCE【6】 位为逻辑0,然后不使用TXHEADER[2]去逻辑0,序列增加范围为({0,32},{0,66})是本身为2bytes和4bytes交互。然而计数器一定要每两个TXUSRCLK2周期当使用2bytes交互时,在4bytes交互时是每个TXUSRCLK2。

TX Buffer

GTP收发器发送数据路径有两个内部并行时钟域被用在PCS。PMA并行时钟域XCLK和TXUSRCLK时钟域。为了发送数据 XCLK速率一定要域TXUSRCLK的速率匹配,所有相位差在两个时钟域之间一定要被解决。

根据上图所示,GTP收发器中的发送器包括一个 TX buffer 和一个Tx相位对齐电路去解决 XCLK和TXUSRCLK两个时钟域之间的相位差。这个TX相位对齐电路是当TX buffer是旁路状态的时候使用。所有数据路径一定使用Tx Buffer 或者 Tx Phase alignment 电路。

USing the TX Buffer

TX buffer应该复位当TXBUFSTATUS表面溢出或者下溢环境。TX缓冲器可以复位通过GTTXRESET.TXPCSRESET或者GTP收发器内部产生Tx Buffer 复位在速率改变时(当TXBUF_RESET_ON_RATE_CHANGE = TRUE)。分配GTTXRESET触发一个复位序列 GTP收发器的发送器完全复位。通过下面设置TX_BUFFER去解决XCL和TXUSRCLK时钟域的相位问题。

TX BUFFER BYPASS

TX 缓存区旁路是 7系列GTP 收发器的一种先进特征。Tx相位对齐电路通常去调整PISO和TX XCLK两者之间的相位差去传输数据从PCS到PISO。Tx相位对齐电路它也帮助 TX延时对齐通过连续调整TXUSRCLK去补偿温度和电压带来的消耗。 TX相位和延时对齐一定需要用户手动去对齐。

Tx Buffer Bypass use modes

Tx相位对齐可以被执行在一个通道上或者一组通道分析一个TXOUTCLK。对于GTP收发器来说TXbuffer旁路支持提供单端链路和多端链路的应用。

Using TX buffer bypass in single - lane 模式

这些GTP收发器的设置被用于 TX buffer 旁路

1. TXBUF_EN=FALSE

2. TX_XCLK_SEL= TXUSR

3. TXOUCLKSEL= 3’b011 or 3’b100去选择GTP收发器参考时钟作为TXOUTCLK的时钟源。

当GTP收发器的时钟被选择,TXOUTCLK作为TXUSRCLK的源时钟,用户必须确保TXOUTCLK和选择GTP收发器参考时钟工作在渴望的频率中,当Tx buffer 是旁路,Tx相位对齐一定要在下列环境之后。

1.复位或者上电GTP收发器的TX

2.复位或者上电PLL

3.改变GTP收发器参考时钟源或者频率

4改变TX line 的速率。

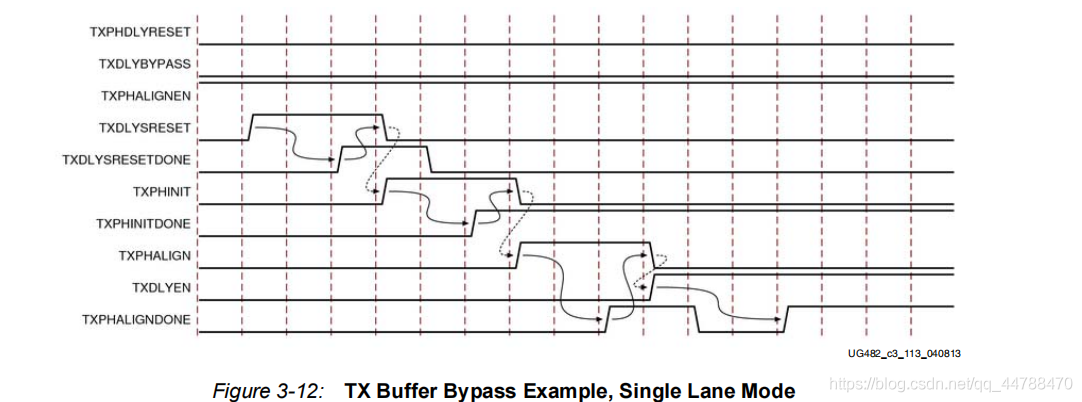

3-12表示每一步 TX相位对齐和使用TX delay对齐去调整TXUSRCLK去补偿温度和电压的变化。

1. 这个序列是事件-3-12 未按比例绘制

2. 设置TXSYNC_OVRD属性为1’b1;

3. 设置TXPHDLYRESET和TXDLYBYPASS是低电平给所有链路

4. 设置TXPHALIGNEN为高电平

5. 分配TXDLYSRESET保持高电平知道TXDLYSRESETDONE被分配

6. 在TXDLYSRESETDONE被分配后 TXDLYSRESET才能失配(拉低)。

7. 当TXLLYSRESET失配,分配TXPHINT,保持这个信号为高电平知道TXPHINITDONE的上升沿被观测到。

8. 失配TXPHINIT

9. 分配TXPHALIGN,保持这个信号为高电平直到,TXPHALIGNDONE上升沿被观测到。

10. 失配TXPHALIGN。

11. 分配TXDLYEN,这个导致TXPHALIGNDONE失配

12. 保持TXDLYEN为高电平直到TXPHALIGNDON的上升沿被观测到

13. TX delay对齐连续调整TXUSRCLK去补偿温度和电压带来的变化

Using TX相位对齐去最小化 TX链路到链路之间的延迟。

Tx相位对齐电路可以最小化在GTP收发器之间的延迟,Figure-3-13展示了TX相位对齐电路如何可以减少链路延迟通过对齐XCLK时钟域的多GTP收发器去一个普同时钟域**。Figure3-22,**展示了多个GTP收发器链路工作在Tx相位对齐一个普通时钟域前后。在TX相位对齐前,所有的XCLK有一个随意的相位差。在对齐TX相位后,仅仅相位差是偏斜来至普通时钟,所有链路发送数据同时地只有数据延时是匹配的。TXUSRCLK和TXUSRCLK2给所有GTP收发器一定来自于同意的源和一定是通过低偏斜的时钟资源比如 BUFG给TX相位对齐电路是有效的。

Using Tx缓存区旁路在多链路模式

这节描述每一步执行多链路Tx 缓存区旁路对齐产生器。

1.主:在多链路应用中,缓存器旁路主设备是作为链路源通道的输出时钟。

2.从:所有链路分享相同的TXUSRCLK/TXUSRCLK2,而这两个时钟产生是从主设备缓存器旁路TXOUTCLK产生。

这些GTP收发器设置是被用作旁路TX缓存器。

1. TXBUF_EN=FALSE

2. TX_XCLK_SEL= TXUSR

3. TXOUCLKSEL= 3’b011 or 3’b100去选择GTP收发器参考时钟作为TXOUTCLK的时钟源。

当GTP收发器的时钟被选择,TXOUTCLK作为TXUSRCLK的源时钟,用户必须确保TXOUTCLK和选择GTP收发器参考时钟工作在渴望的频率中,当Tx buffer 是旁路,Tx相位对齐一定要在下列环境之后。

1.复位或者上电GTP收发器的TX

2.复位或者上电PLL

3.改变GTP收发器参考时钟源或者频率

4改变TX line 的速率。

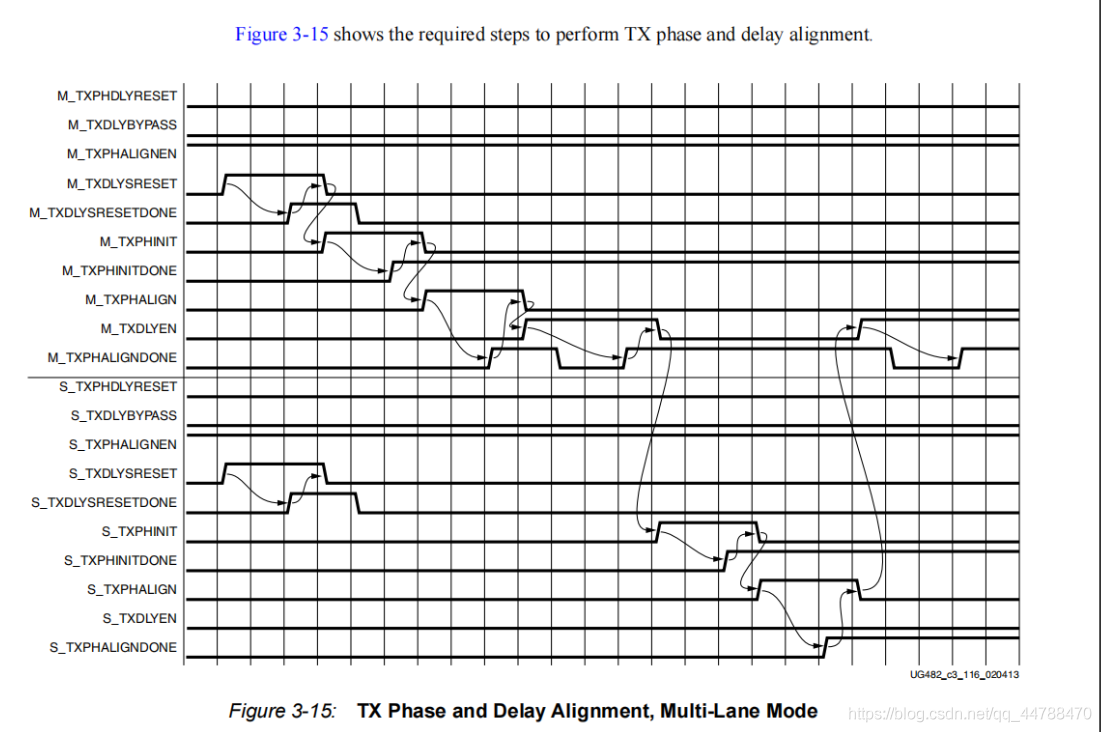

1.这个序列事件展示了Figure3-15并非按比例绘制。

1. M*表示端口关于主设备链路

2. S* 表示端口关于从设备链路

3. GTP收发器:设置TXSYNC_OVRD属性为1’b1;

4. 设置TXPHDLYRESET和TXDLYBYPASS为低给所有链路

5. 设置TXPHALIGNEN是高电平给所有链路

6. 分配TXDLYSRESET给所有链路。保持这个信号为高电平直到TXDLYSRESETDONE的被声明。

7. 解除分配 TXDLYSRESET给所有链路当TXDLYSRESETDONE被声明时。

8. 当TXDLYSRESET的所有链路解除分配时,声明TXPHOINT给所有主设备链路。保持TXPHINIT这个信号为高电平直到主设备的TXPHINITDONE的上升沿被观测到。

10.解除分配TXPHINIT给所有主设备链路

声明TXPHALIGN给所有主设备链路。保持这个信号为高电平直到主设备链路的TXPHALIGNDONE被观测到

12.解决分配TXPHALIGN给所有主设备链路

13.声明TXDLYEN给所有主设备链路。这个导致TXPHALIGNDONE将被解除分配。

14.保持TXDLYEN给所有主设备电路为高电平直到主设备的TXPHALIGNDONE被观测到。

15.解除分配TXDLYEN给所有主设备链路

16.分配TXPHINIT给所有从设备链路,保持TXPHINIT这个信号为高电平直到TXPHINITDONE这个信号的上升沿在从设备被观测到。

17.失配TXPHINIT给所有从链路,当TXPHINITDONE被声明时。

18.当TXPHINIT给所有从设备链路是解除声明时,声明TXPHALIGN给所有从设备链路。并保持TXPHALIGN这个信号为高电平直到TXPHALIGNDONE的上升沿在从设备被观测到。

19.解除声明TXPHALIGN给所有从设备链路,当TXPHALIGNDONE是声明时

20.当TXPHALIGN给所有从设备链路是解除声明时,声明TXDLYEN给所有主设备链路。这个导致主设备链路的TXPHALIGNDONE将解除声明

21.等待直到主设备链路的TXPHLIGNDONE重新声明。相位和延时对齐给多重链路交互是完成的。继续保持TXDLYEN给所有主设备为高去调整TXUSRCLK去补偿温度或者电压的改变。。

这边的分配和声明可以理解为拉高, 失配和解除声明可以理解为拉低。