本文转载自:Vuko-wxh的CSDN博客

前言

RFSoC中最重要的部分是射频直采ADC和DAC的配置,除了前文介绍的DAC和ADC的基本功能以外,还有其他的相关功能和配置,可以用于配置射频数据转换器,本文参考官方手册,主要对正交调制器校正、粗延迟设置、动态更新配置、PLL以及中断处理操作进行介绍。

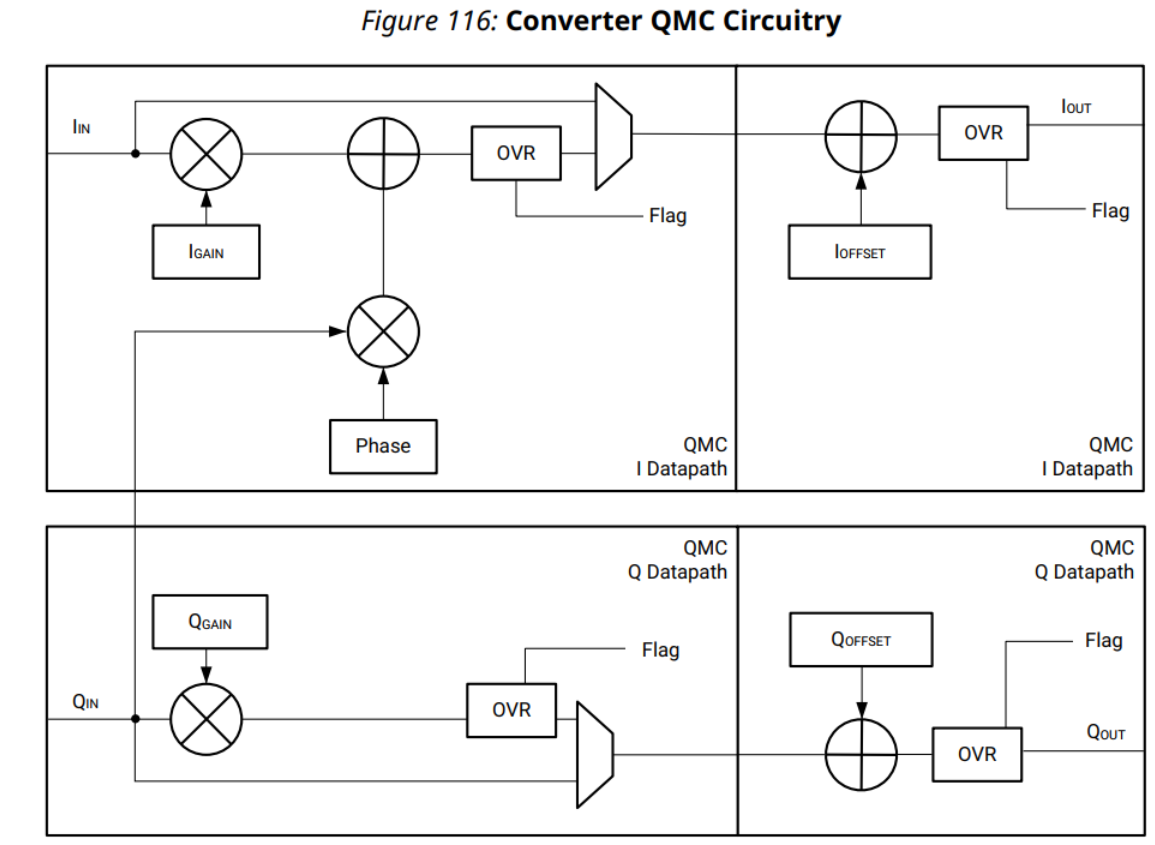

正交调制器校正

当使用外部模拟正交混频器设备时,必须使用一对转换器(RF-ADC 或 RF-DAC)来处理转换后的 I 和 Q 数据路径。 由于外部事件或环境,可能会在模拟 I 和 Q 信号路径中引入错误或不平衡,如果不加以纠正,可能会导致系统性能下降。 使用正交调制器校正 (QMC) 电路可以完成使任何系统从降级中恢复的必要校正。

如下图所示,QMC 电路仅用于校正。 错误和/或不平衡检测必须由内部互连逻辑中的特定应用代码完成。

QMC 电路可以补偿以下内容:

增益校正是通过将信号乘以增益因子来完成的。 该因子的范围为 0 到 2.0,可以将各个因子应用于 I 和 Q 数据路径。 块的输出分辨率为 16 位。

相位校正是通过将 Q 的比例分数添加到 I 值来实现的。 这种加法的结果会导致增益误差,必须由增益误差校正块来校正。

相位校正的范围约为 ±26 度。

偏移校正是通过向采样信号添加一个固定的 LSB 值来完成的。 范围是 -2048 到 2047。

要获得完整的 QMC 功能,需要设置一对转换器并在 I/Q 模式下使用。 当禁用相位校正因子时,QMC 模块可以为实模式下使用的转换器提供增益和偏移校正。 在这种情况下,转换器无需配对即可使用 QMC 模块功能。

更新 QMC 设置

可以使用 RFdc 驱动程序 API 设置增益、相位和偏移校正因子值。 使用 API 的示例如下。

// Initial Setup XRFdc_QMC_Settings QMC_Settings_I, QMC_Settings_Q; // RF-ADC block0 is I, RF-ADC block1 is Q QMC_Settings_I.EventSource = XRFDC_EVNT_SRC_TILE; // QMC Settings are updated with a tile event QMC_Settings_Q.EventSource = XRFDC_EVNT_SRC_TILE; .... // Update Gain/Phase/Offset for I/Q RF-DACs in tile0 QMC_Settings_I.GainCorrectionFactor = 0.9; // Set Gain for I QMC_Settings_I.PhaseCorrectionFactor = -5.0; // I/Q imbalance factor applied to I side, approx in degrees. QMC_Settings_I.EnableGain = 1; QMC_Settings_I.EnablePhase = 1; QMC_Settings_Q.GainCorrectionFactor = 0.95; QMC_Settings_Q.EnableGain = 1; XRFdc_SetQMCSettings(ptr, XRFDC_ADC_TILE, 0, 0, &QMC_Settings_I); // Write settings for ADC0,0 - I ADC XRFdc_SetQMCSettings(ptr, XRFDC_ADC_TILE, 0, 1, &QMC_Settings_Q); //Write settings for ADC0,1 - Q ADC XRFdc_UpdateEvent(ptr, XRFDC_ADC_TILE, 0, 0, XRFDC_EVENT_QMC); //Generate a Tile Update Event - applies all QMC Settings at once

还可以使用 XRFdc_GetQMCSettings RFdc 驱动程序 API 命令从任何转换器读回 QMC 设置。 这将使用来自硬件的值填充 QMC_Settings 结构。

I/Q RF-ADC 命名约定

在 I/Q 对中使用转换器时,I 通道始终使用偶数块编号,而 Q 通道始终使用奇数块编号。 例如,在 Dual RF-ADC tile 中,I RFADC 是 block0,Q RF-ADC 是 block1。 对于 Quad RF-ADC 块或 RF-DAC 块,I 通道是 block0 和 block2,而相关的 Q 通道分别是 block1 和 block3。

QMC 溢出

相对于输入信号设置过多的增益、相位或偏移校正因子会导致数据路径溢出。 为了帮助系统调试,QMC 模块包含内置的溢出检测和饱和模块。 这些模块生成标志,这些标志使用数据路径中断连接到 IP 中断机制。

QMC 模块的相关中断标志是:

XRFDC_IXR_QMC_GAIN_PHASE_MASK

XRFDC_IXR_QMC_OFFST_MASK

这些中断可以为每个转换器通道启用。

增益校正乘数范围在 0 和 2.0 之间。

相位校正乘数的范围约为±26 度,或幅度为±0.5。

粗延迟

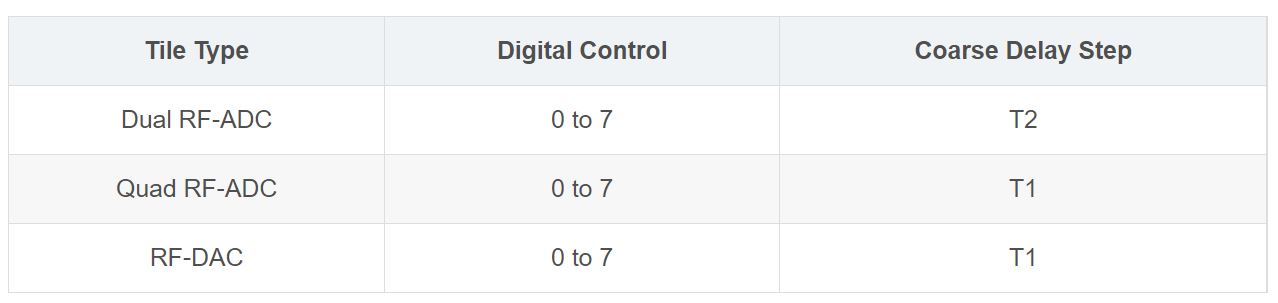

粗延迟允许调整数字数据路径中的延迟,这对于补偿系统实现中的延迟失配很有用。 这里的补偿仅限于采样时钟的某个周期。下表显示了用于 Gen 1/Gen 2 器件的延迟调整功能的采样时钟周期数(T1 或 T2 = 2*T1)。

延迟调整采样时钟周期(第 1 代/第 2 代)

下表显示了 Gen 3 器件的这种延迟调整功能的采样时钟 (T1) 周期数。

延迟调整采样时钟周期(第 3 代)

动态更新事件

RF-ADC 和 RF-DAC 块中的某些数据路径功能可以在运行时更新。根据应用程序,可能需要立即更新设置或等待某个事件来应用更新。 例如,在重置 NCO 相位时,使用 SYSREF 事件允许在多个图块上同时应用相位重置操作。

下表显示了可用的事件类型。

旨在动态更新的功能必须被编程为对这些更新事件之一敏感。 更新是一次性事件。 第一个触发器在布防后锁定在更新中。 每个功能的事件源都是灵活的,可以单独设置。 以下功能支持此动态更新:

旨在动态更新的功能必须被编程为对这些更新事件之一敏感。 更新是一次性事件。 第一个触发器在布防后锁定在更新中。 每个功能的事件源都是灵活的,可以单独设置。 以下功能支持此动态更新:

精细混频器/NCO

正交调制器校正 (QMC)

粗延迟

更新事件使用

RFdc 驱动程序 API 使用特定函数的 EventSource 参数来设置该函数的触发事件。 它还可以发出事件的子集。 以下代码显示了设置Tile事件源后跟Tile事件的示例。

// Initial Setup - Mixer settings for 2 DDC blocks XRFdc_Mixer_Settings Mixer_Settings_0; XRFdc_Mixer_Settings Mixer_Settings_1; // Mixer Settings for both DDC blocks are updated with a tile event Mixer_Settings_0.EventSource = XRFDC_EVNT_SRC_TILE; Mixer_Settings_1.EventSource = XRFDC_EVNT_SRC_TILE; .... // Make changes to mixer settings and write them to both DDCs Mixer_Settings_0.freq = 1.23; Mixer_Settings_1.freq = 1.43; XRFdc_SetMixerSettings (ptr, XRFDC_ADC_TILE, 0, 0, &Mixer_Settings_0); XRFdc_SetMixerSettings (ptr, XRFDC_ADC_TILE, 0, 1, &Mixer_Settings_1); // Generate the event for DDC block 0 // This maps to the Tile event, which updates both DDCs at the same moment XRFdc_UpdateEvent(ptr, XRFDC_ADC_TILE, 0, 0, XRFDC_EVENT_MIXER);

PLL

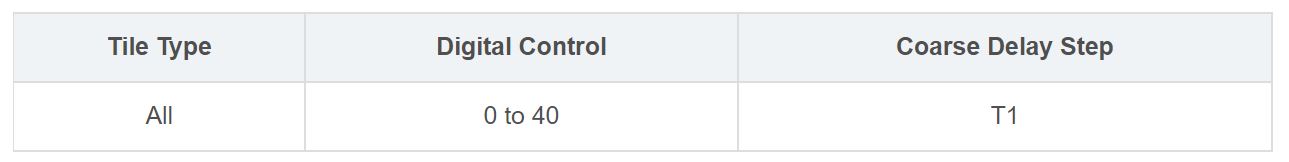

每个 RF-ADC 和 RF-DAC 块都包括一个时钟系统,该系统带有一个输入时钟分频器、一个 PLL 和一个输出分频器。 当与 SYSREF 输入一起使用时,时钟系统可以在多块或多器件设计中同步。 当使用 PLL 时,输出采样时钟被馈送到多路复用器,在它被路由到 tile 的时钟网络之前,它也可以被直接输入时钟使用(如下图所示)。 来自 PLL 的时钟用于块中 RF-ADC 或 RF-DAC 的模拟和数字部分。 tile 中的每个 RF-ADC 或 RF-DAC 都有一个本地分频器,用于分频和分配来自 PLL 的极低抖动时钟或直接输入到每个 RF-ADC 或 RF-DAC 功能中的不同功能。

100Ω ODT 仅在 tile 启用时可用,不建议在 tile 禁用时驱动输入时钟级。

使用 Vivado设置 PLL 的操作参数以指定默认 PLL 配置,或者如果需要对 PLL 进行运行时调整,则通过 RFdc 驱动程序 API 设置。 如果需要使用 API 进行运行时调整,必须首先在 Vivado IDE 中启用 PLL。

内部 PLL 框图如下图所示。 使用内部 PLL 时,IP 向导或专用于配置 PLL 系统的 API 函数将参考分频器值设置为整数,将反馈分频器值设置为整数,将输出分频器值设置为整数,以达到最佳性能 在正确范围内使用 VCO 的 PLL。 在任何频率配置中,当 PLL 系统能够选择参考分频器 1 时,相位噪声的最佳性能会实现。

对于任何内部 PLL 使用,频率系统具有公式 Fs = (Fin/R)*(FBDiv/M),

如下图所示,其中 Fs 是 PLL 频率输出,Fin 是参考频率。

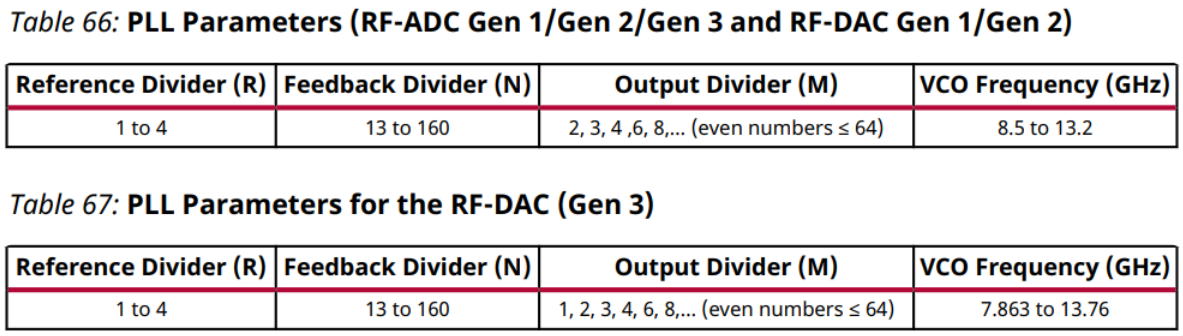

PLL 参数

下表显示了片上 PLL 的关键参数。

对于 Gen 3,片上 PLL 覆盖了 RF-ADC 的所有可能采样频率,而对于 RF-DAC,有一个片上 PLL 不支持的“漏洞”。 IP 将迫使您避免频率范围内的这个“漏洞”。

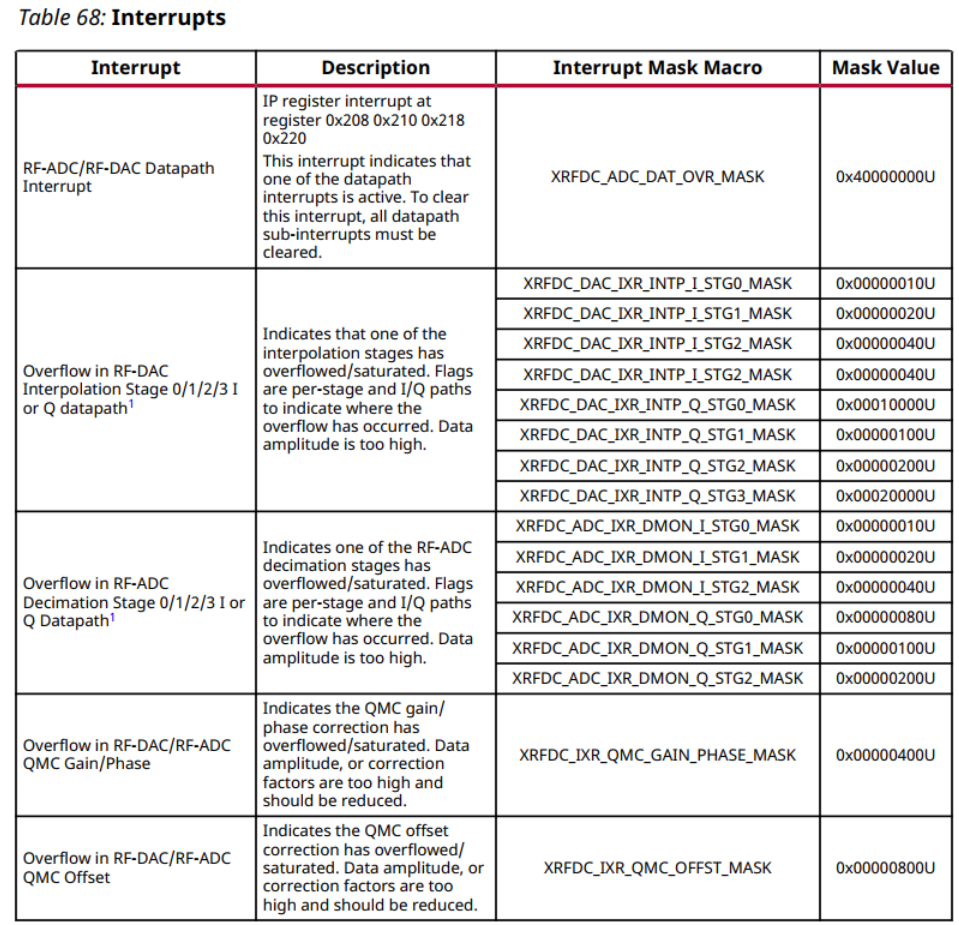

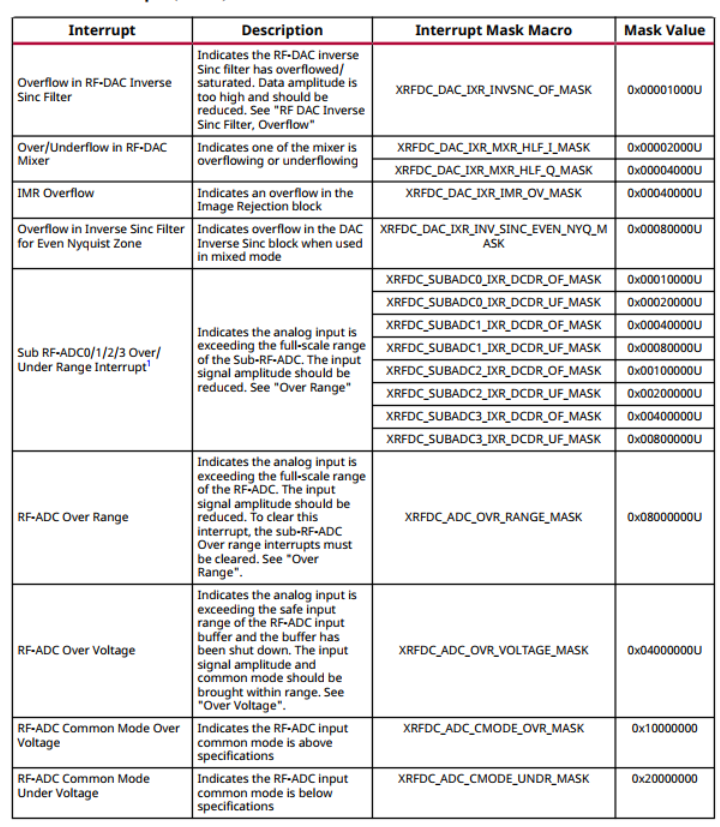

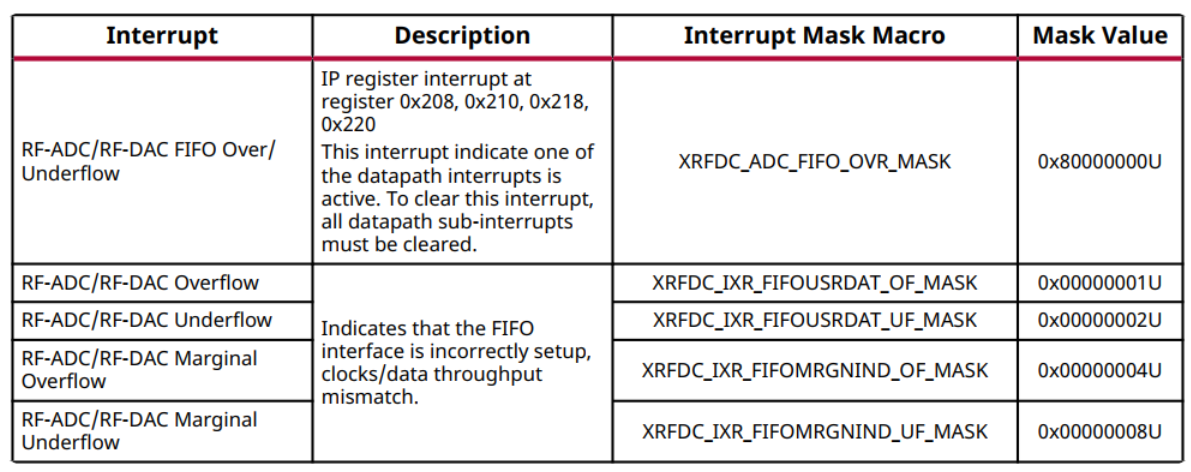

中断处理

RF-ADC 和 RF-DAC 块可以在操作期间产生中断,这有助于调试或避免潜在问题。 中断如下表所示。

中断层次结构

中断层次结构

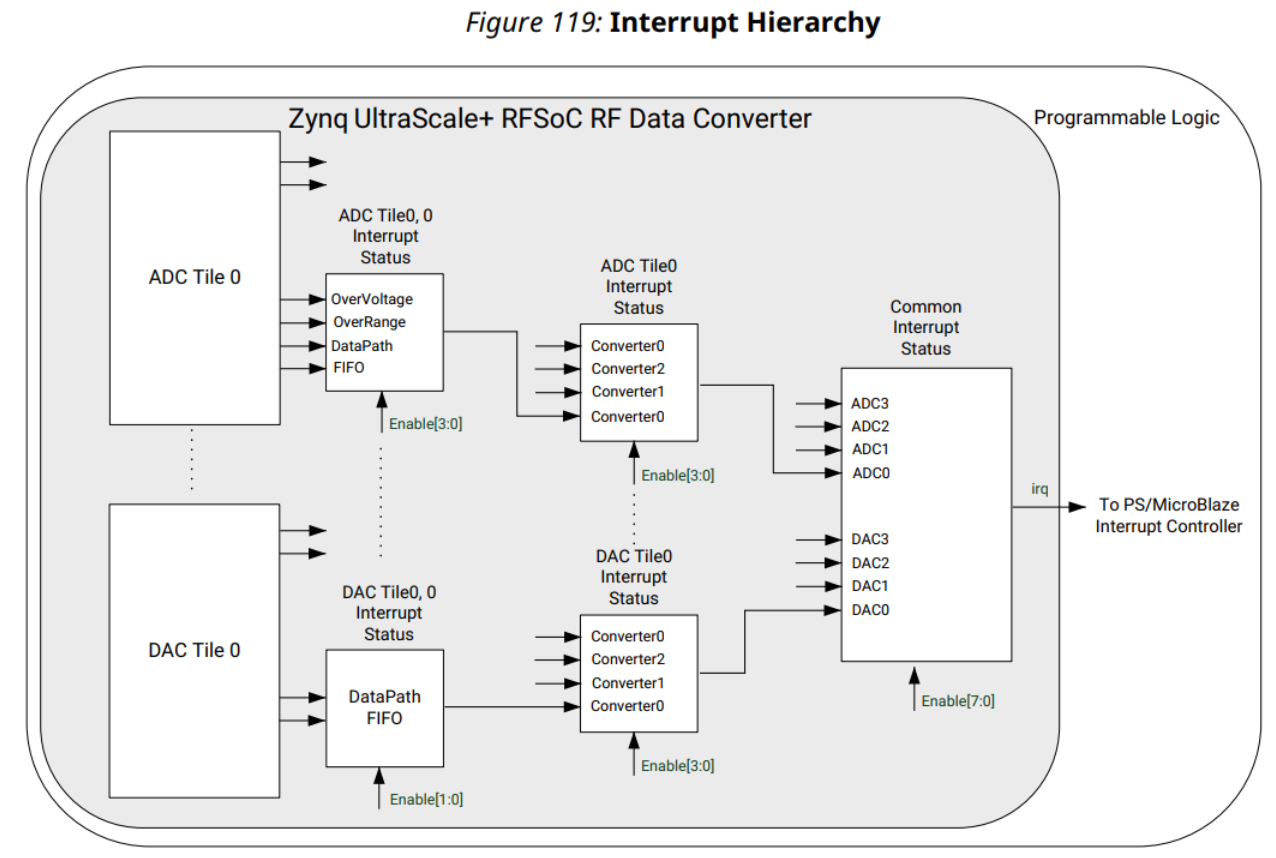

下图显示了 IP 内核中的中断层次结构。

数据路径溢出表示信号链中的子模块检测到输出信号幅度已超过满量程,并且已饱和。 如果检测到溢出,则表明信号幅度太高,或者信号幅度的模块设置不正确。 例如,对接近满量程的信号使用较大的增益校正因子会导致 QMC 增益溢出。

上图中显示的所有中断均由 RFdc 驱动程序 API 的中断函数启用和处理。 默认的中断状态处理程序(XRFdc_IntrHandler)会自动按照上图中的中断层次结构来确定中断的来源,然后将此信息传递给用户定义的状态处理程序进行响应。

中断设置和处理示例

以下代码显示了中断设置和处理示例。

//

// Handler

//

// User-Defined interrupt status handler

void RFdcHandler (void *CallBackRef, u32 Type, int Tile, u32 Block, u32 Event) {

// Check the type of interrupt event

if (Type == XRFDC_DAC_TILE) {

xil_printf("\nInterrupt occurred for ADC%d,%d :", Tile_Id, Block_Id);

if(Event & (XRFDC_IXR_FIFOUSRDAT_OF_MASK | XRFDC_IXR_FIFOUSRDAT_UF_MASK)) {

xil_printf("FIFO Actual Overflow\r\n");

}

if(Event & (XRFDC_IXR_FIFOMRGNIND_OF_MASK | XRFDC_IXR_FIFOMRGNIND_UF_MASK)){

xil_printf("FIFO Marginal Overflow\r\n");

}

if(Event & XRFDC_DAC_IXR_INTP_STG_MASK)) {

xil_printf("Interpolation Stages Overflow\r\n");

}

// ... Other handling code ...

}

else {

xil_printf("\nInterrupt occurred for ADC%d,%d :\r\n", Tile_Id,Block_Id);

// ... ADC handling code ...

}

}

//

// Setup

//

// Register the user-defined interrupt handler

XRFdc_SetStatusHandler(ptr, ptr, (XRFdc_StatusHandler) RFdcHandler);

//

// Setup for RF-DAC tile 0, block 0 - FIFO Interrupt

//

XRFdc_IntrEnable(ptr, XRFDC_DAC_TILE, 0, 0, XRFDC_IXR_FIFOUSRDAT_MASK);

//

// Test

//

// Force a FIFO interrupt by setting the FIFO write words to a different value from the design requirements.

// Note: Assumes a value of 1 is invalid for this design.

XRFdc_SetFabRdVldWords(ptr, 0, 0, 1);此示例显示了 RFdc 驱动程序特定的中断处理以及通过更改 FIFO 参数来强制中断。 没有显示使用 PS 或 MicroBlaze™ 中断控制器设置和注册 RF 数据转换器 irq 输出。

reference