作者:专注陈,来源:雷达系统工程师

更新原因

因整个FPGA的工程逐渐趋于完整,芯片的运行功耗相比本文初稿时又有了明显的增长,故更新最新的数据情况,以供后来者在硬件设计时参考之用,同时利用已调通的板载电源监控系统读取了各电源的电压、电流值。

唠嗑之言

最近在为专业组内设计的一款相控阵雷达数字接收机板卡做开发,又当了一回FPGA和嵌入式代码猿,但这回自己只设计方案,由团队的精干小伙来具体操刀原理图和PCB,不用自己画板子了。这次的板子有些新玩意,换了处理平台,开始用上了Xilinx家的Zynq UltraScale+ MPSOC,本次为一颗中高端型号XCZU9CG,所选封装型号在PL和PS资源上具有一定的伸缩性,拥有5个兼容型号,在资源需求较低的应用场景中可降一个型号等级,在更高需求场景中则可提升一个等级;这一点在实现硬件复用时是非常重要的,同样的板卡,根据不同的需求可选择不同的配置,当然也有土豪可能会直接用顶配通吃所有应用场景。

FPGA核心电源设计的重要性

众所周知,中高端FPGA的电源中有两大耗电大户,VCCINT核心电压,和MGT高速收发器,实际工作电流取决于资源使用率、时钟频率、逻辑翻转率等。因此若用到高速率DDR4且频繁读写,该部分逻辑功耗必然不低;

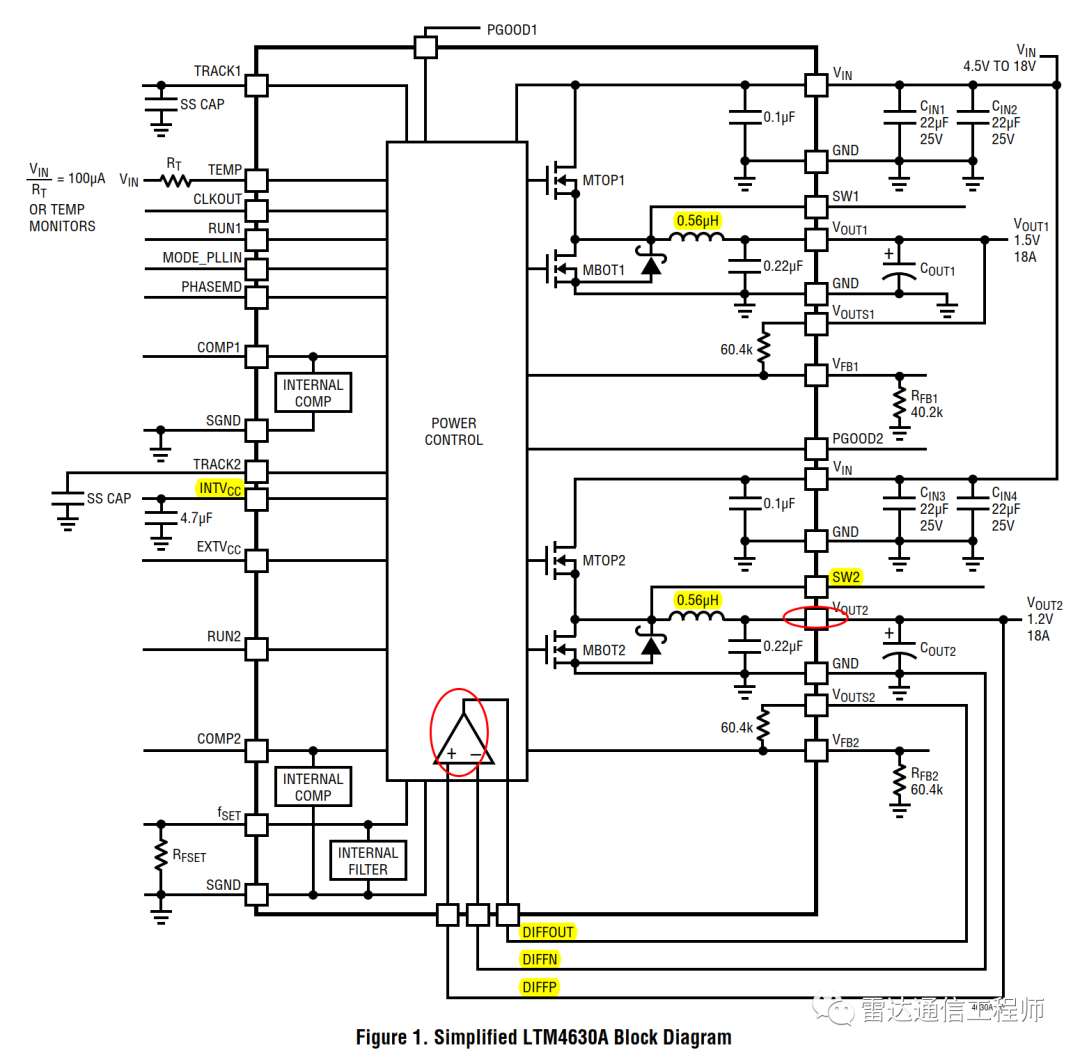

类似Zynq UltraScale+ MPSOC这类芯片,PL和PS的核心均为0.85V,官方推荐的PL域可靠范围是850±25mV,25mV虽然不算小,但是当电流达到10A级别时,一般的电源设计就很难再满足这个需求,例如10A电流时从电源芯片到FPGA电源管脚之间1毫欧的电阻就将带来10mV的压降,即使是铺铜的电源平面,通常也不止1毫欧的电阻;举个更极端的例子,如X86的i7、i9 CPU,英伟达的3060、3070、3080 GPU,TDP功耗都超过100W,其核心电压也很低,电流可达近100A级别,线路损耗的影响将更加明显。为此,这类应用的电源都带有Remote Sense电压补偿功能,其通过一对差分线获取靠近负载端的电压,并稳定该点的电压为设置值,而不是像普通电源芯片稳的是电源的输出点。下图为ADI的LTM4630A的原理框图,其详细画出了Remote Sense电压补偿功能的机理,本质上是变换了闭环控制环路的反馈取样点(负载芯片)

实际案例

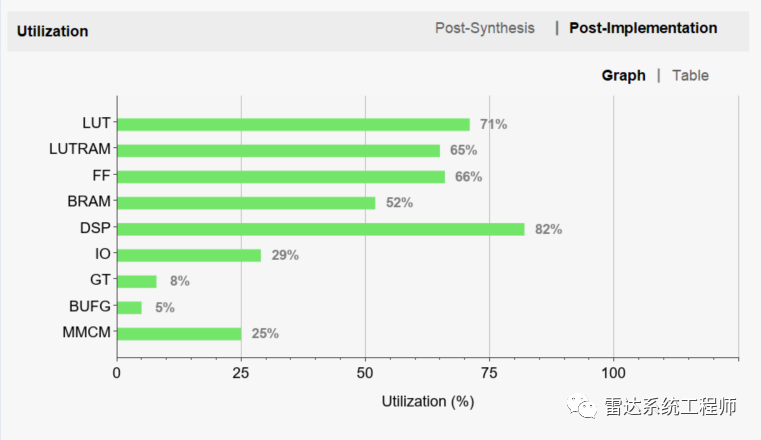

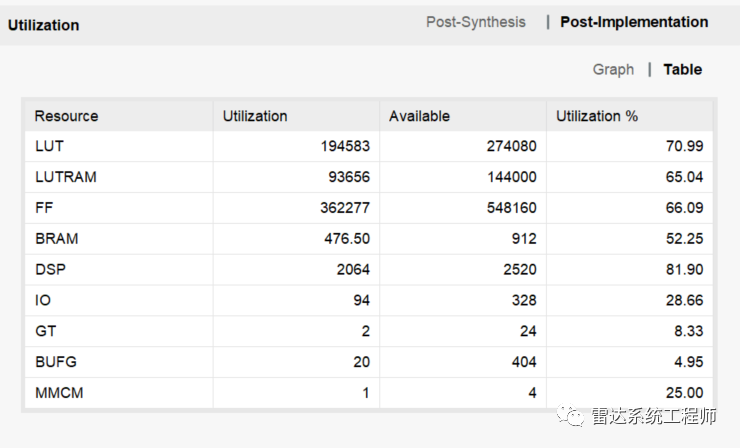

本案列中FPGA实现一个64路数字接收机系统,即一共包含128路IQ通道,因频段间隔较小,对滤波器要求较高,因此DSP资源占用率很高(71%),时钟120MHz;此处还不包括PL的DDR、ADC接口逻辑、和高速光口通信的接口,PS(双核A53)也仅仅跑了一个裸机用于配置时钟芯片等外设;具体资源使用情况如下图:

案列中PS和PL核心电压共用同一电源(规格0.85V@36A);在此条件下测量电源芯片的输出,达到了0.95V,而FPGA芯片背面的电容上电压为0.85V,两者相差100mV;这100mV正是线路损耗引起的,经测量,实际电流为12.5A(包含PL+PS的核心电压);此处如果没有Remote Sense的电压补偿功能,则到达MPSOC的电压将降到0.75V而导致系统无法正常工作。待PL+PS的设计完成,核心电流还会升高,压降也将更大;注意:虽然该板因有Remote Sense功能目前是正常工作的,但是100mV的压降同时导致了额外的功耗和热耗(100mV*12.5A=1.25W),该1.25W的功耗全在供电线路上转换成了热量;因此核心电压电源设计和Layout需要特别关注该点,虽然压降不可避免,但可以通过设计使其控制在合理的范围内,而如何评估这个压降则需要用到电源完整性仿真(PI),可在PCB设计Layout后仿真计算出压降值;可见另一篇文章ADS仿真-电源完整性仿真PIPro(PI-DC)

温度对电流的影响

温度主要影响FPGA内部晶体管的漏电流,手册中体现为静态电流(无bit的空白状态时),下图为某国产型号的温度、静态电流数据,可以看到25摄氏度和125摄氏度时相差20倍。

更新内容

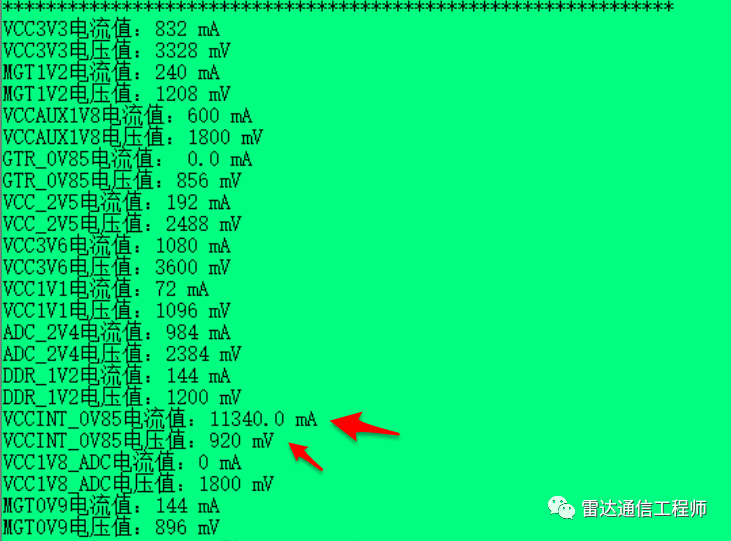

下图为板载电源监控模块监测的电压电流信息,其中VCCINT 0.85V的电流达到了11.3A。