作者:李西锐 校对:陆辉,来源: FPGA技术江湖微信公众号

在之前的学习当中,我们已经学习了Vivado的基本操作,接下来我们将继续学习软件的下板验证过程。

本次试验我们仍然使用上一节中使用的实验内容,用二输入与门来进行此次下板验证。

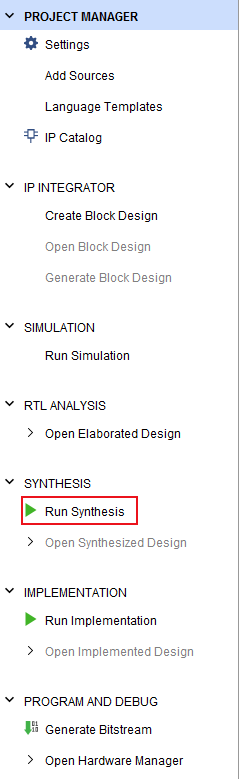

我们打开与门工程,先编译一下。

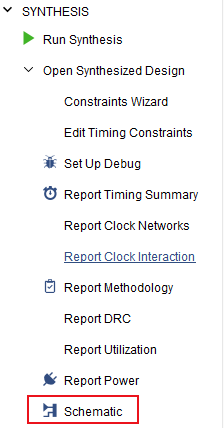

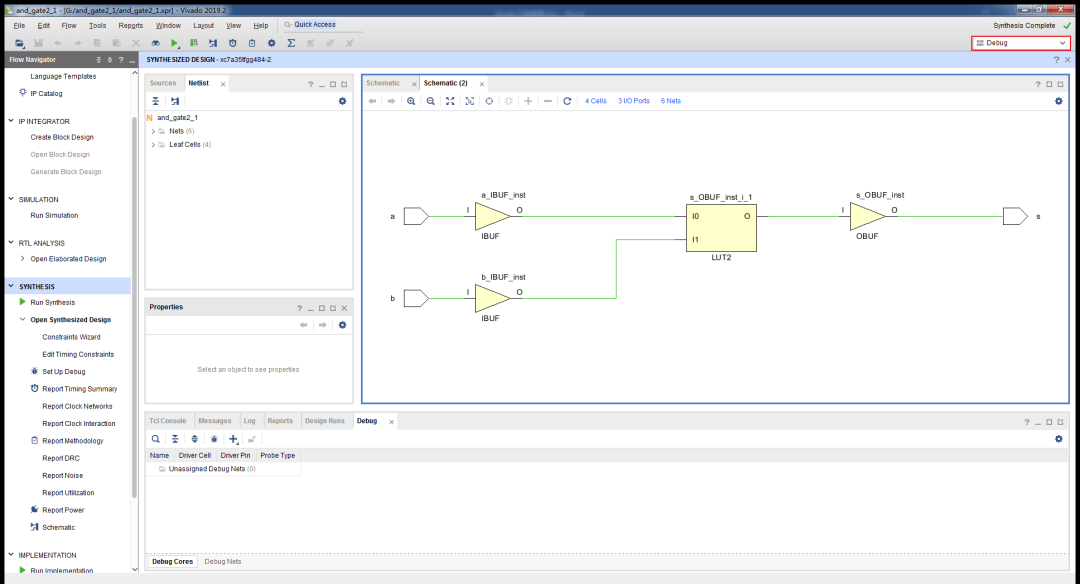

编译成功后,点击open synthesized design打开,然后选择最后一个选项schematic打开原理图。

然后在界面右上角点击打开I/O planning。

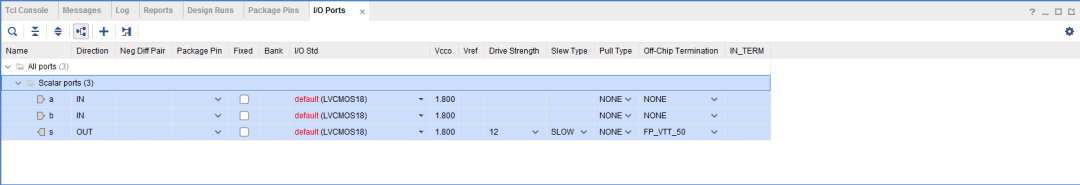

打开后,在界面下方打开I/O Ports。

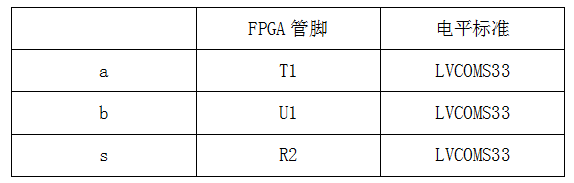

在这个界面,我们需要分配引脚以及电平标准才能下板,此次实验,我们以SANXIN-B04为基础进行下板。管脚约束如下表:

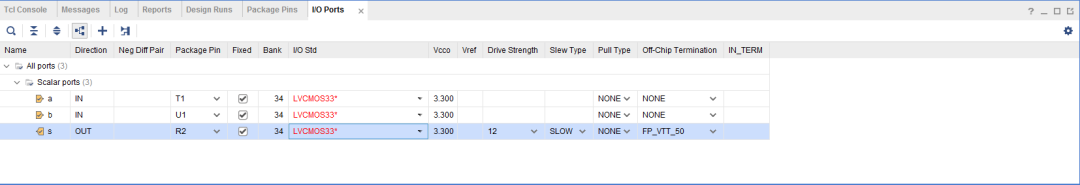

分配好之后,如下图:

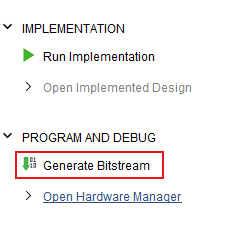

分配好之后点击保存,会生成一个XDC文件。然后点击生成bit流。

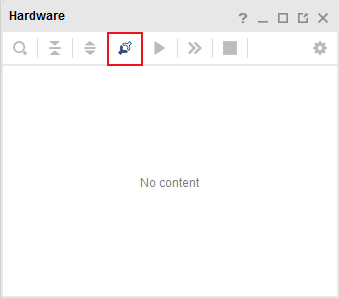

这个文件是我们下板的文件,生成之后点击open hardware manager打开下板界面,连接开发板。点击自动连接。

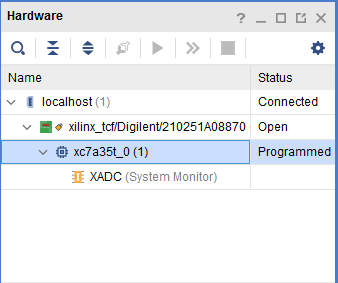

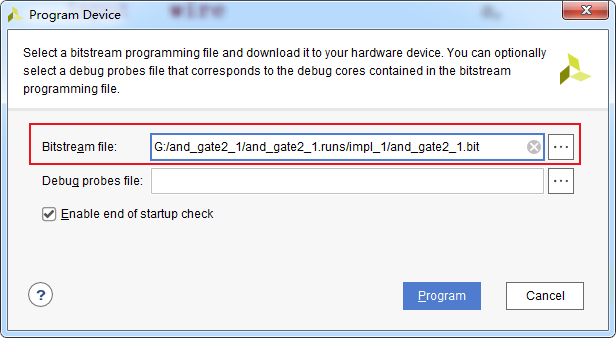

然后选中芯片,如图。鼠标右键点击,选择program device,就会有提示框提示要下载的文件以及逻辑分析仪文件。在所选框中会默认选择此工程生成的下板文件,在下一行为逻辑分析仪的下载文件,我们暂时用不到,在此我们先不做过多讲述。确认没有问题之后点击program。

下板成功之后观察开发板现象,我们会看到led0是一直亮的状态。

当我们按下按键,灯会熄灭。按键按下为0,led为1时点亮。那么按照我们与门的逻辑,验证结果正确。

由于开发板种类各有不同,大家可以根据自己使用的开发板去操作下板验证。

持续更新,欢迎各位关注。