本文转载自:Vuko-wxh的CSDN博客

写在前面

ZYNQ固化时,正常情况下都需要DDR参与,但是有时硬件设计时,可能将DDR去掉或设计出错,这将导致ZYNQ无法正常固化,之前有写过一个使用静态链接库进行无DDR固化的文章,当时那个是压缩了FSBL的相关代码只保留FLASH模式下的功能,对于其他模式可能无法正常使用,本文将无DDR固化的情况进一步进行介绍,讲解如何修改FSBL实现ZYNQ的程序固化,给出一个demo进行演示测试。

适用范围

不论是之前提到的静态链接库的版本还是本文版本(暂且叫做运行在OCM版本)。都只适合PS端的轻量级代码,PL端无特殊要求,但是PL PS交互部分如果需要太多驱动可能也会超出片上RAM的空间。本工程根本思想就是将fsbl分配到较大的com0上,其余应用工程分配到ocm1上。

建立工程

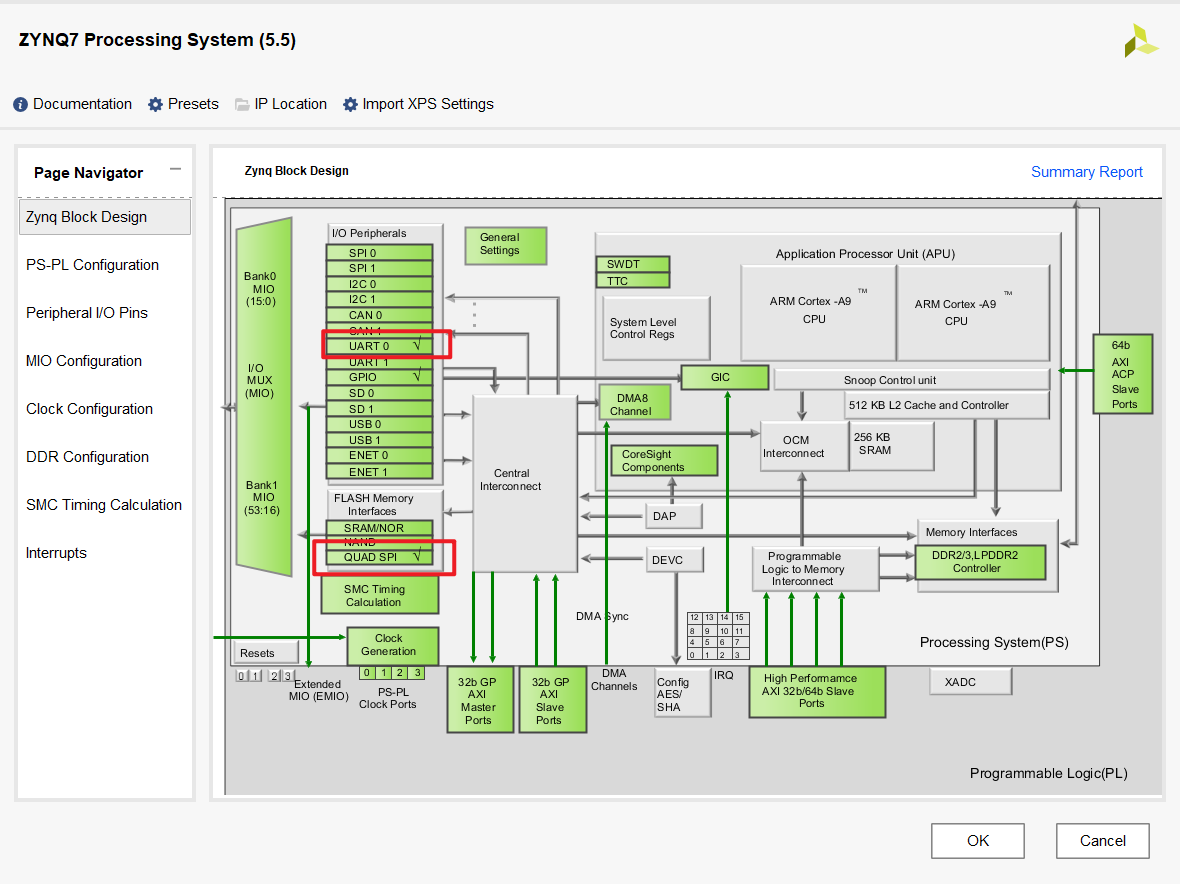

建立一个Block design,添加zynq核,然后勾选,FLASH和UART部分。

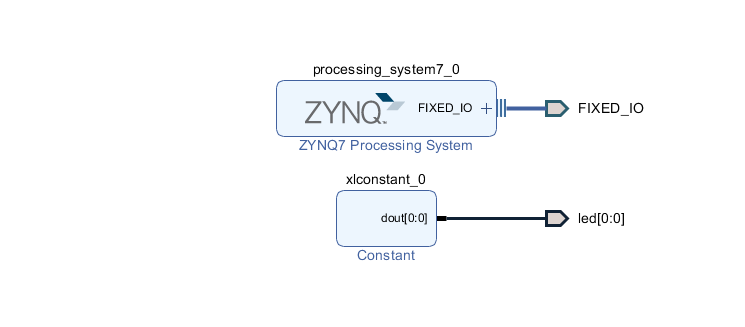

这里为了验证PL端功能正常启动,添加了一个逻辑常数用于驱动LED灯。

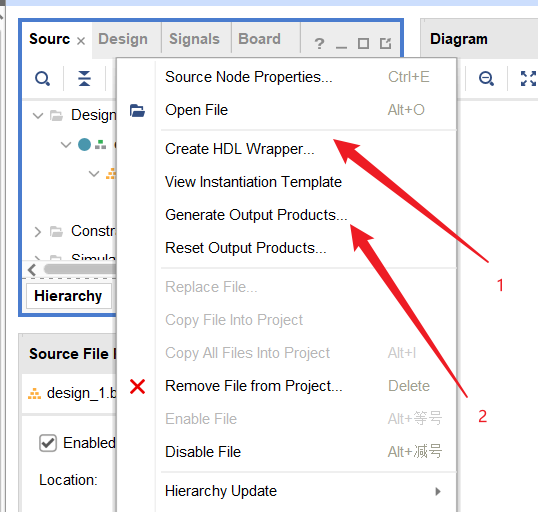

创建HDL顶层,生成output products,因为涉及到PL端部分,所以需要综合导出生成bitstream,不要忘记加管脚约束。

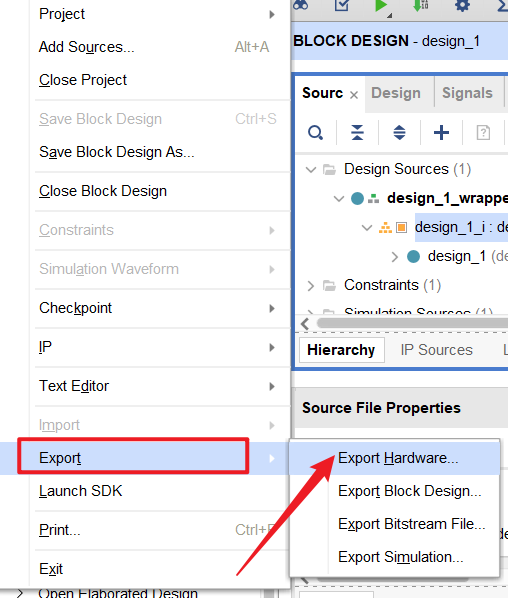

当运行生成bitstream后,导出硬件,并且包含bit流文件。

准备好硬件平台后就可以进行SDK的FSBL代码的修改了。

SDK代码修改

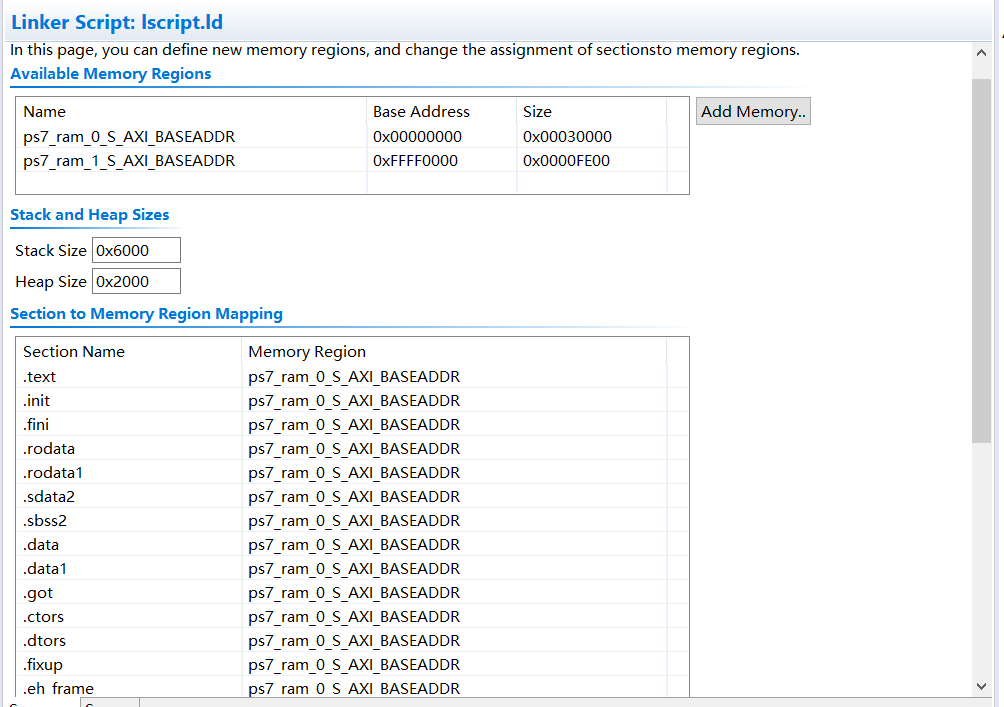

新建应用工程建一个helloworld工程,打开lscript.ld文件将helloworld的代码段映射区对应到ps7_ram_1,保存编译。

新建应用工程建一个fsbl工程,打开lscript.ld文件将helloworld的代码段映射区对应到ps7_ram_0,保存编译。

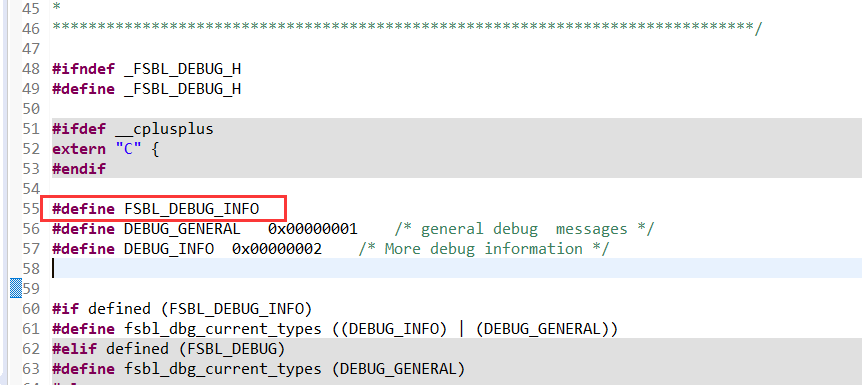

打开fsbl代码的fsbl_debug.h文件,增加FSBL_DEBUG_INFO的宏定义方便进行查看fsbl的调试信息。

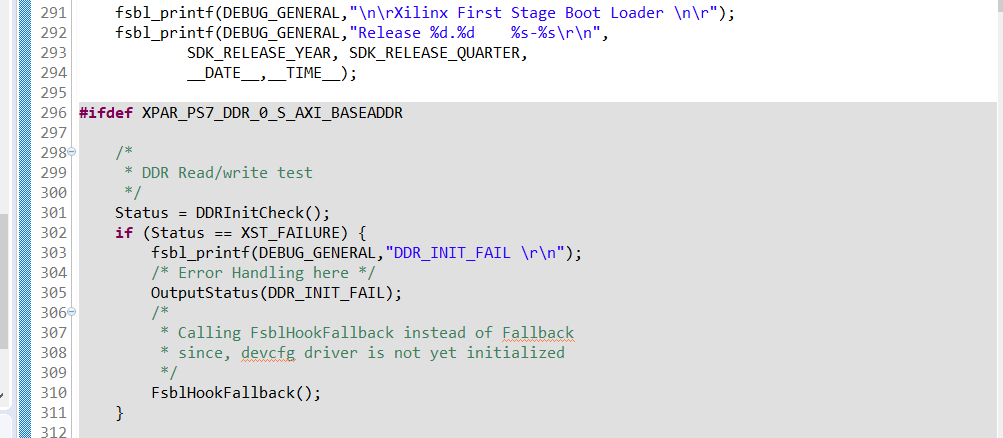

打开main.c文件,找到main函数,定位到296行附近,在这里可以看到因为缺少ddr的部分,该部分代码将不会正常执行,将会跳转到下面的代码中。

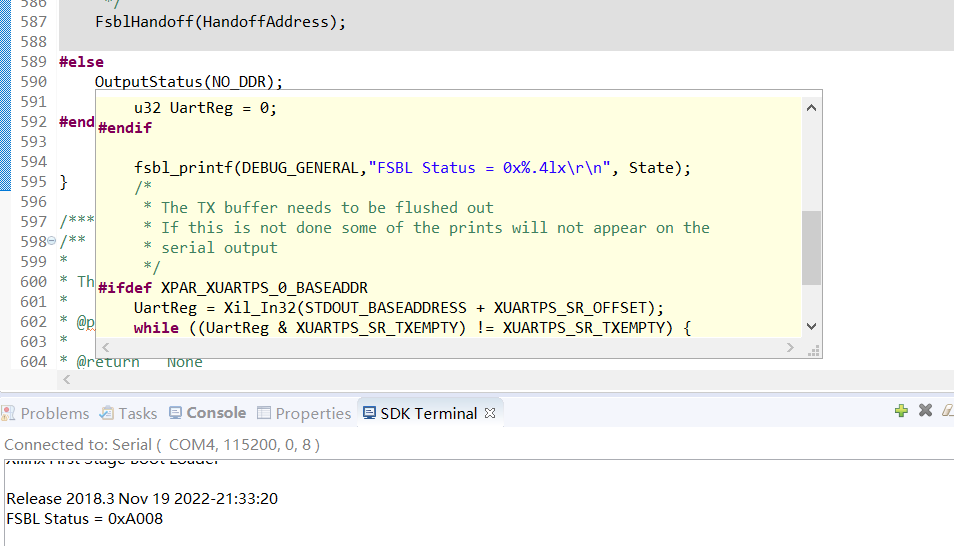

代码以下两行代码执行后FSBL 状态打印输出0XA008,在fsbl.h文件中对应DDR missing 的状态。

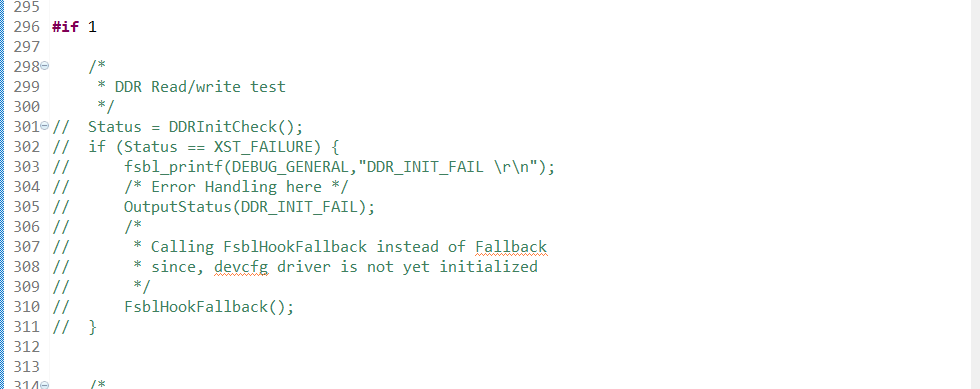

因此要想使得代码正常运行就要将正常存在ddr时的代码正常运行,仅删除和DDR强有关的部分(影响编译和运行的),然后将代码运行地址设置到OCM上。

所以,取消对296行的定义改成如下内容。

此时如果使用当前版本的fsbl的可执行文件可以正常进行烧写固化了。但是可能此时还是无法正常启动,下面步骤用于演示并定位具体问题。

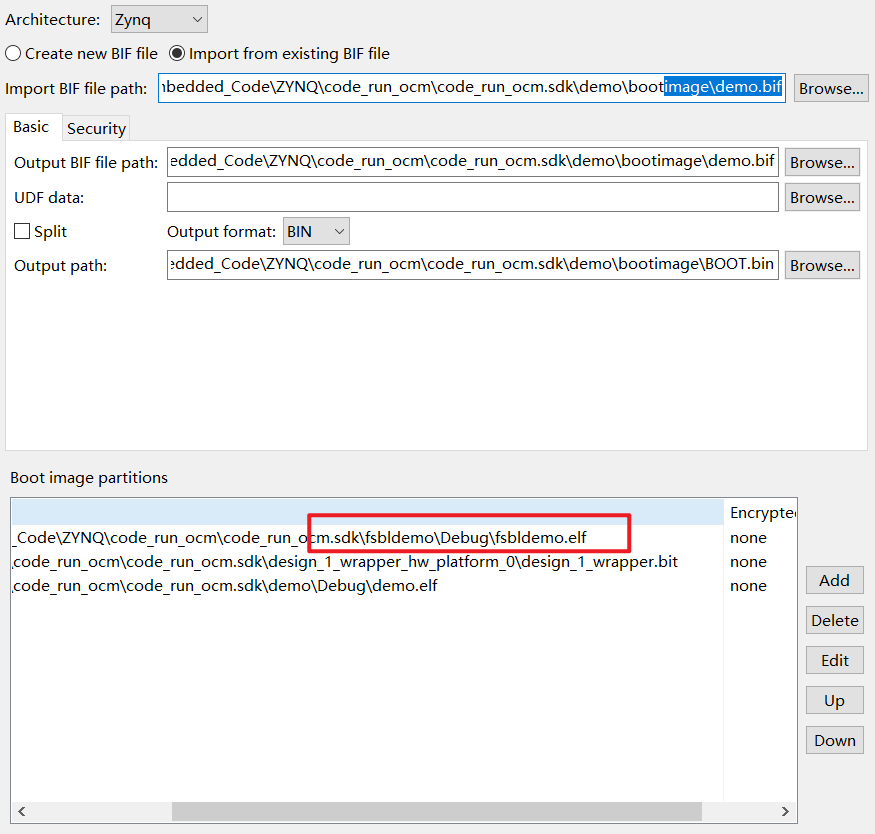

选中helloworld工程创建镜像工程。

BootLoader选中刚刚修改好的fsbl.elf。

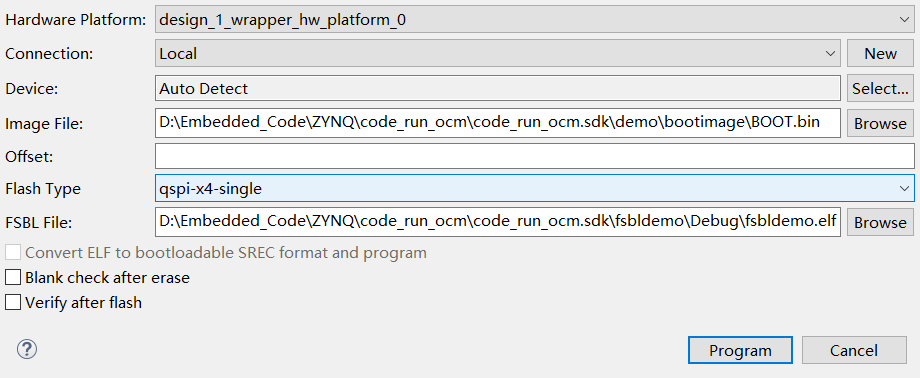

打开开发板,选择jtag模式下烧写,选择创建好的镜像和刚刚的fsbl的elf文件。

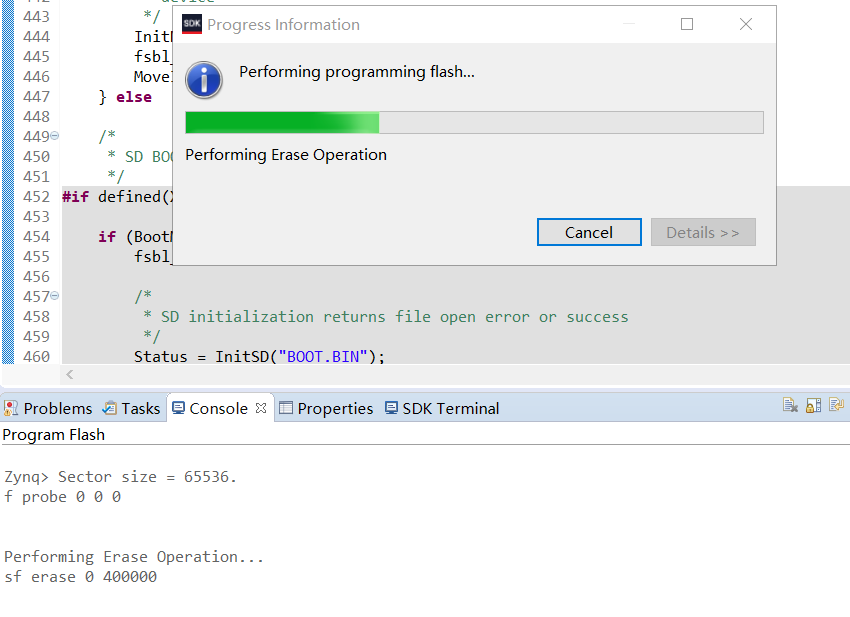

正在烧写…

烧写完成后关掉开发板,切换到flash模式下打开串口观察应用程序能否正常启动。在我的开发板FPGA done的指示灯和PL端的LED等都只是闪烁了一下,不能正常启动。

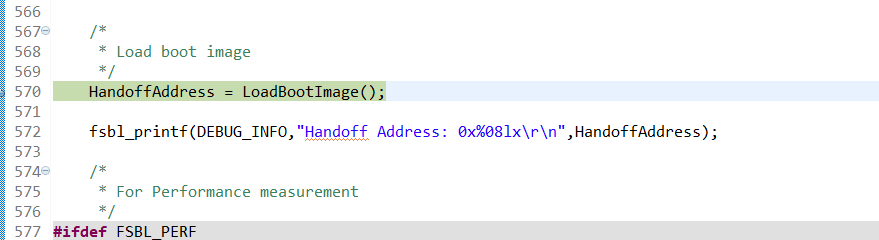

此时还在flash模式下去尝试在线烧写。从调试信息可见,FLASH正常启动,启动初始化后存在失败,单步调试后发现main函数的在570行的LoadBootImage()运行后就会存在上述问题。

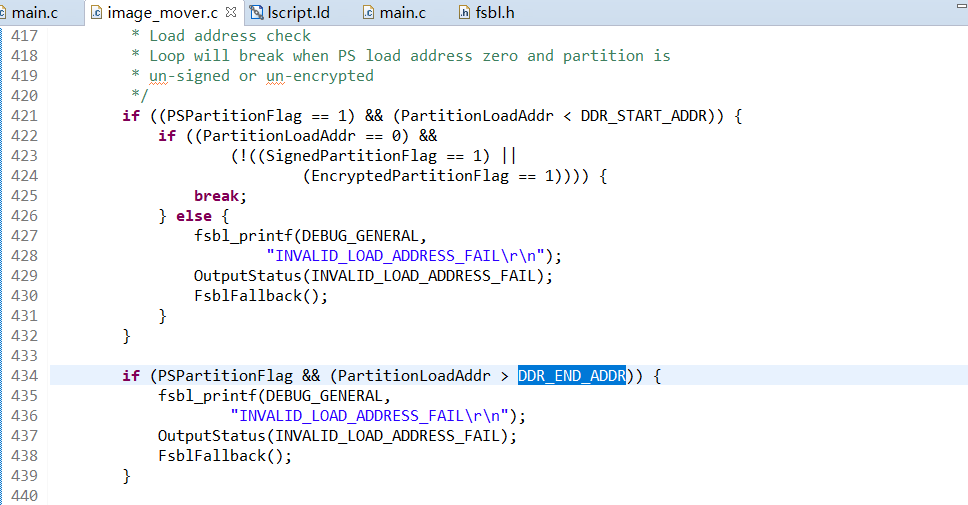

定位到image_mover.c的436行,发现此处的DDR_END_ADDR的默认定义是0X00,无法正常执行下面的程序。

所以这里修改DDR_END_ADDR为片上rom的结束地址。

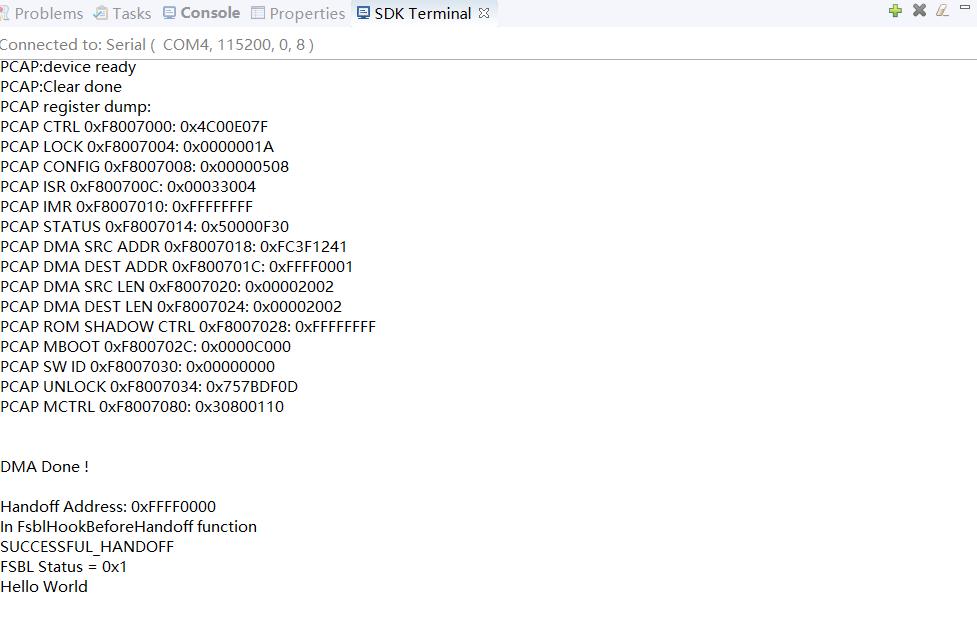

再次重复操作,完成镜像生成后,jtag模式烧写,flash模式启动,观察打印调试信息。从调试信息中可以看到,PS端正常启动,此时挂在PL端的LED灯也能正常点亮。