作者: 张海军,来源: 傅里叶的猫微信公众号

VCS+Verdi的组合是EDA仿真中必备神器,以前只会用Vivado自带的仿真器或者Modelsim来进行仿真,但用了VCS+Verdi后,就不想再用vivado自带的仿真器了,Verdi看波形、追信号实在是快太多了。

首先就是要用VCS把xilinx的仿真库都编译一遍,这样才能用vcs进行仿真。

打开vivado,在Tools下面有个Compile Simulation Libraries.

选择VCS,再指定库文件存放的路径;如果VCS的环境变量设置好了,那么会自动跳出Simulator executable path的路径的。

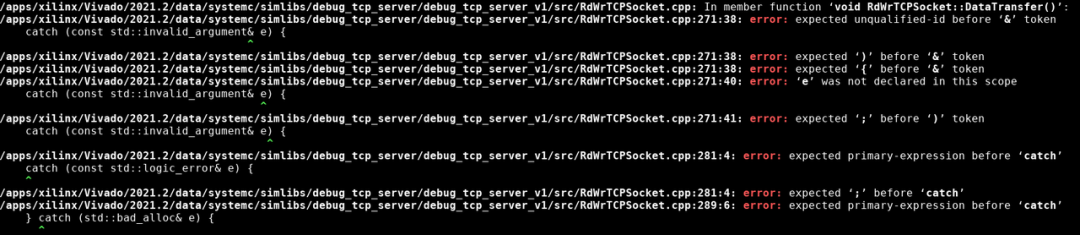

在编译过程中,可能会提示错误:

/apps/xilinx/Vivado/2021.2/data/systemc/simlibs/debug_tcp_server/debug_tcp_server_v1/src/RdWrTCPSocket.cpp: In member function ‘void RdWrTCPSocket::DataTransfer()’:

/apps/xilinx/Vivado/2021.2/data/systemc/simlibs/debug_tcp_server/debug_tcp_server_v1/src/RdWrTCPSocket.cpp:271:38: error: expected unqualified-id before ‘&’ token

catch (const std::invalid_argument& e) {

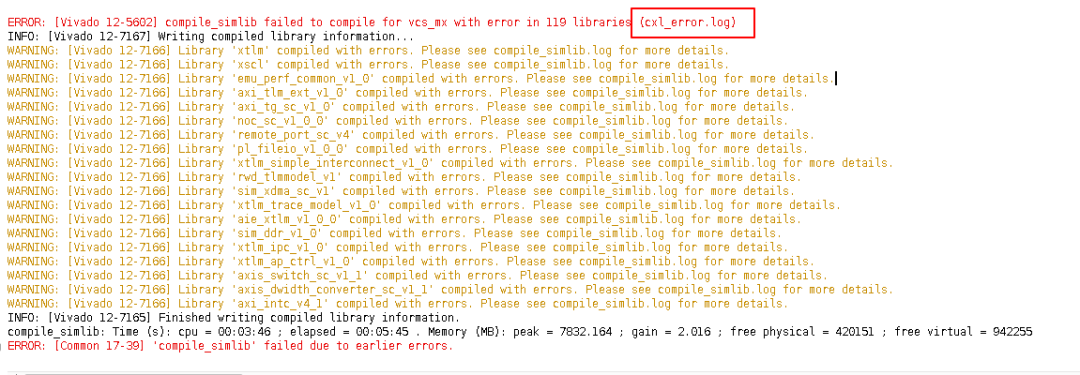

打开cxl_error.log

可以看到,提示我们gcc版本有问题,而且在提示中,已经指明了需要使用gcc 7.3,而我们当前是11.2的版本。

更换gcc版本后,再重新编译,就可以成功编译出仿真库。