本文转载自:FPGA Zone微信公众号

本文继续简单介绍一下基于FPGA的以太网ARP通信,该项目主要用于实现FPGA端以太网接口和上位机进行ARP请求和应答的功能。文章末尾有该工程源码获取方式,有需要的小伙伴可以点赞、分享、投个币支持一下~

RGMII接口

以太网的通信离不开物理层PHY芯片的支持,以太网MAC和PHY之间有一个接口,常用的接口有MII、RMII、GMII、RGMII等。

MII(媒体独立接口):MII支持10Mbps和100Mbps的操作,数据位宽为4位,在100Mbps传输速率下,时钟频率为25Mhz。

RMII(Reduced MII):RMII是MII的简化版,数据位宽为2位,在100Mbps传输速率下,时钟频率为50Mhz。

GMII(Gigabit MII):GMII接口向下兼容MII接口,支持10Mbps、100Mbps和1000Mbps的操作,数据位宽为8位,在1000Mbps传输速率下,时钟频率为125Mhz。

RGMII(Reduced GMII):RGMII是GMII的简化版,数据位宽为4位,在1000Mbps传输速率下,时钟频率为125Mhz,在时钟的上下沿同时采样数据。在100Mbps和10Mbps通信速率下,为单个时钟沿采样。

在千兆以太网中,常用的接口为RGMII和GMII接口。RGMII接口的优势是同时适用于10M/100M/1000Mbps通信速率,同时占用的引脚数较少。但RGMII接口也有其缺点,就是在PCB布线时需要尽可能对时钟、控制和数据线进行等长处理,且时序约束相对也更为严格。

ETH_RXC:接收数据参考时钟,1000Mbps速率下,时钟频率为125MHz,时钟为上下沿同时采样;100Mbps速率下,时钟频率为25MHz;10Mbps速率下,时钟频率为2.5MHz,ETH_RXC由PHY侧提供。

ETH_RXCTL(ETH_RX_DV):接收数据控制信号。

ETH_RXD:四位并行的接收数据线。

ETH_TXC:发送参考时钟,1000Mbps速率下,时钟频率为125MHz,时钟为上下沿同时采样;100Mbps速率下,时钟频率为25MHz;10Mbps速率下,时钟频率为2.5MHz,ETH_TXC由MAC侧提供。

ETH_TXCTL(ETH_TXEN):发送数据控制信号。

ETH_TXD:四位并行的发送数据线。

ETH_RESET_N:芯片复位信号,低电平有效。

ETH_MDC:数据管理时钟,该引脚对ETH_MDIO信号提供了一个同步的时钟。

ETH_MDIO:数据输入/输出管理,该引脚提供了一个双向信号用于传递管理信息。

RGMII接口时序

PHY芯片的RGMII接口时序,其时钟、控制信号和数据的对齐方式,一般由MDIO接口或者硬件上的特殊引脚进行配置。

接收时序

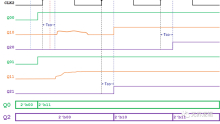

RXC的上下边沿与RXD和RX_CTL信号对齐,相位相同。

RGMII接收端口时钟和控制/数据信号增加延时的时序图如下:

RXC的上下边沿与RXD和RX_CTL信号的中间位置对齐,RXC的时钟周期为8ns,单个高电平或者低电平为4ns,RXC相对于RXD和RX_CTL延时约2ns。

YT8511 RGMII接收端口的信号对齐模式由硬件上的特殊引脚外接上下拉电阻进行配置,如下图所示,当管脚LED_10_100接上拉电阻时,表示RXC时钟相对于RXD信号,会增加约2ns的延时。

发送时序

RGMII发送端口正常模式下,需要满足TXC的上下边沿与TXD和TX_CTL信号对齐,相位相同。YT8511在硬件上面没有做TX端的delay模式,可根据实际情况,选择是否在代码中进行延时(因为一般对端设备的接收端会有延时处理的功能,因此发送端也可以不延时),延时后的时序图如下所示:

由RGMII的接口时序可知,RGMII发送端口在TXC时钟的上升沿传输TXD的低4位和TX_CTL的使能信号;下降沿传输TXD的高4位和TX_CTL的错误信号(实际上是使能信号和错误信号的异或值);RGMII接收端口在RXC时钟的上升沿传输RXD的低4位和RX_CTL的使能信号;下降沿传输RXD的高4位和RX_CTL的错误信号(实际上是使能信号和错误信号的异或值)。

实现功能

该项目采用FPGA端以太网接口,和上位机实现ARP请求和应答的功能。当上位机发送ARP请求时,FPGA返回ARP应答数据,当FPGA发送ARP请求时,上位机返回ARP应答数据。

功能测试

ARP接收

ARP发送

利用上位机端wireshark软件抓取FPGA端发来的ARP请求数据包,如下图所示:

下图中下方红框为FPGA发送的16进制数据(去掉前导码、SFD和CRC值),可以看到,后面的18个0就是我们在发送时填充的18个字节数据。