对FPGA的管脚进行约束的时候,常常看到这样的电平标准,例如LVCOM18,LVCOS25,LVDS,LVDS25等等,其实这些都是一系列的电平标准。

针对数字电路而言,数字电路表示电平的只有1和0两个状态,在实际的电路中,需要约定什么样的电压为1,什么样的电压为0。

数字电路中的双阈值是这样定义的,例如TTL接口电平标准:对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.5V;对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V;也就是需要大于某一个阈值表示电平1,小于某一个阈值表示电平0.

电平标准的分类

常见IO接口可分为单端IO接口和差分IO接口,详细的IO标准参见下图。单端IO接口和差分IO接口均满足高速接口传输,区别在于应用场合不同。

TTL

TTL是Transistor-Transistor Logic的英文缩写,从其命名就可以看出,这种接口电平标准的初衷是用于基于三极管结构的数字系统之间的。

工作于TTL接口标准下的数字电路,其内部有源器件的标准电源供给应为5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.5V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V;

LVTTL

由于2.4V与5V之间还有很大空间,这对改善噪声干扰并没有什么明显的好处,而且还会增加系统的功耗,并且由于数字状态1、0之间电平相差较大,还会影响到数字电路的响应速度。因此后来就把TTL的电压范围进行了一些压缩,从而形成了LVTTL——Low Voltage Transistor-Transistor Logic,也即低压TTL电平标准。以下介绍两种目前常用的LVTTL标准:

LVTTL3V3

LVTTL3V3的意思,即其内部有源器件的标准电源供给为3.3V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V;

对比输出、输入端的电压要求可知,为了保证双阀值判定的稳定性和抗噪性,输出端的电压要求仍比输入端的双阀值判定标准要严格,这点对于所有的数字系统接口标准是一样的,以后不再赘述。

LVTTL2V5

LVTTL2V5的意思,即其内部有源器件的标准电源供给为2.5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.0V,状态0的电压要求为小于等于0.2V;

对于输入端,状态1的判定要求为大于等于1.7V,状态0的判定要求为小于等于0.7V

CMOS

CMOS是Complementary Metal Oxide Semiconductor的英文缩写,从其命名就可以看出,这种接口电平标准的初衷是用于基于NMOS、PMOS组成的MOS管结构的数字系统之间的。

工作于CMOS接口标准下的数字电路,其内部有源器件的标准电源供给为5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于4.45V,状态0的电压要求为小于等于0.5V;

对于输入端,状态1的判定要求为大于等于3.5V,状态0的判定要求为小于等于1.5V。

CMOS与TTL接口相比,有了更大的噪声容限,并且其输入阻抗也远大于TTL输入阻抗。

LVCOMS

同TTL一样,鉴于功耗和响应速度的考虑,CMOS也同样衍生出了LVCMOS接口标准,并且由于MOS管相对于三极管的导通门限更加低,因此LVCMOS比LVTTL更容易使用较低的电压进行通信。以下介绍几种目前常用的LVTTL标准:

LVCOMS33

LVCMOS3V3的意思,即其内部有源器件的标准电源供给为3.3V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于3.2V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.7V。

LVCOMS25

LVCMOS2V5的意思,即其内部有源器件的标准电源供给为2.5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.0V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于1.7V,状态0的判定要求为小于等于0.7V。

LVCOMS18

LVCMOS1V8的意思,即其内部有源器件的标准电源供给为VCC=1.8V,当然这是有一定容忍度的,不过与之前介绍的电平标准不同,这个容忍度会影响它的输出、输入情况,介绍如下:

对于输出端,状态1的电压要求为大于等于VCC-0.45V(若VCC精确等于1.8V,则为1.35V),状态0的电压要求为小于等于0.45V;

对于输入端,状态1的判定要求为大于等于0.65倍的VCC(若VCC精确等于1.8V,则为1.17V),状态0的判定要求为小于等于0.35倍的VCC(若VCC精确等于1.8V,则为0.63V)。

LVCOMS15

LVCMOS1V5的意思,即其内部有源器件的标准电源供给为VCC=1.5V,它的容忍度也会影响到其输出、输入情况,介绍如下:

对于输出端,LVCMOS1V5没有明确的要求,但是肯定是状态1越接近VCC越好,状态0越接近0V越好;

对于输入端,状态1的判定要求为大于等于0.65倍的VCC(若VCC精确等于1.5V,则为0.975V),状态0的判定要求为小于等于0.35倍的VCC(若VCC精确等于1.5V,则为0.525V)。

LVCOMS12

LVCMOS1V2的意思,即其内部有源器件的标准电源供给为VCC=1.2V,它的容忍度也会影响到其输出、输入情况,介绍如下:

对于输出端,LVCMOS1V2也没有明确的要求,但是肯定是状态1越接近VCC越好,状态0越接近0V越好;

对于输入端,状态1的判定要求为大于等于0.65倍的VCC(若VCC精确等于1.2V,则为0.78V),状态0的判定要求为小于等于0.35倍的VCC(若VCC精确等于1.2V,则为0.42V)。

LVDS

低电压差分信号。其特性如下:LVDS的电压摆幅仅有350mV左右,电流也仅有3.5mA左右,而且又是差分传输,因此具有高速、超低功耗、低噪声和低成本等优良特性。

RS232

RS232是美国电子工业协会EIA(全称为Electronic Industry Association)制定的一种串行物理接口标准。RS是Recommended Standard的缩写,中文意思为推荐标准,232为标识号。RS232总线标准共设有25条信号线,这里我们仅讨论其数字电平接口判定标准。

RS232的标准电源供给为±12V或±15V,状态1的电压要求为-15V到-3V之间,状态0的电压要求为3V到15V之间。

RS485

RS485相当于RS232的升级版,与LVDS类似,RS485也是采用差分的形式来传递信息(不过RS485是真的传了两路电压信号过去),因此抗干扰性要优于RS232。这里,我们同样仅关心其数字电平接口判定标准。

RS485的状态1,其两线之间的电压差要求为2V到6V之间;状态0,其两线之间的电压差要求为-6V到-2V之间。

不同标准之间能否混连?

有时候受限于两方的一些配置情况,可能并不能找出统一的电平标准来进行通信,那么此时,是不是除了设计接口转换电路板以外就没有别的方法了呢?并不是的,其实,有些不同的接口电平标准是可以兼容的。

首先单端和差分是不可能兼容的,因为从物理连线上它们就不一样。但是对于同种类的接口,如果A电平标准的输出符合B电平标准的输入,那么就称A的输出可驱动B的输入,如果反之亦然,那么称A、B两种电平标准可相互驱动。

例如,CMOS的输出是可以驱动TTL输入的,但是反之则不行,因为TTL的状态1输出仅为大于等于2.4V,并不能达到CMOS判决状态1所需要的大于等于3.5V;但是LVTTL3V3和LVCMOS3V3却可以相互驱动,因为它们的输出都能满足彼此的输入判定要求。

如何得知FPGA上面的引脚是上面标准

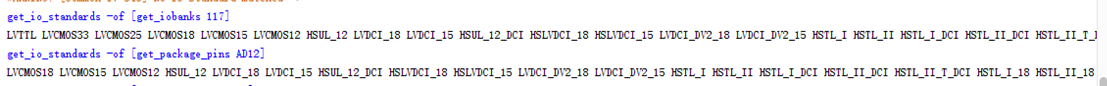

电平标准分为板子内部和外部的拓展。面对芯片内部的引脚,通常我们使用VIVADO的TCL命令get_io_standards -of,具体方法如下图。当我们面对外部的拓展引脚,通常采用查询该外部拓展的电平手册的方式来进行。

以BANK117为例子,其支持的电平标准结果如下:

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/dalingertong/article/details/134419844