本文转载自:FPGA入门到精通

“SRL_STYLE”属性是Vivado中用于控制移位寄存器(Shift Register Logic, SRL)映射方式的关键属性。

本文将详细介绍SRL_STYLE的工作原理、可选值及其在实际设计中的应用代码示例。

一、什么是SRL_STYLE?

SRL_STYLE属性用于指导Vivado综合工具如何将SRL映射为硬件实现。

在Xilinx FPGA中,SRL可以由不同类型的硬件资源实现,包括寄存器(Flip-Flops)、查找表(LUTs)以及块RAM(Block RAM)。

不同的实现方式具有不同的性能特点和资源消耗,因此选择合适的SRL_STYLE对于优化设计至关重要。

二、什么是移位寄存器?

移位寄存器是一种重要的数字逻辑电路,它能够在时钟信号的驱动下,将存储的数据按位进行左移或右移。

这种电路在串行通信、数据处理和存储器设计中有着广泛的应用。

三、SRL_STYLE的可选值

“SRL_STYLE”属性有六个可选值,分别是:

1、register

使用纯寄存器(Flip-Flops)实现SRL,默认是这个属性。

这种方式通常提供较好的时序性能,因为寄存器的时钟到输出的延迟(Tco)较小。

2、srl

使用查找表(LUT)来实现SRL。

这种方式可以节省寄存器资源,适用于小深度的SRL。

3、srl_reg

使用LUT和触发器的组合来实现SRL,最后一级深度使用触发器。

这种方式结合了LUT和寄存器的优点,适用于中等深度的SRL。

4、reg_srl

同时使用寄存器和LUT资源实现SRL,寄存器放在第一级。

这种方式适用于需要在SRL的输出端提供较好的时序特性的场景。

5、reg_srl_reg

第一级和最后一级深度使用触发器,中间级别使用LUT。

这种方式在SRL的两端使用寄存器,中间使用LUT,适用于需要两端时序保证的SRL。

6、block

使用块RAM(BRAM)来实现SRL。

对于大深度的SRL,这种方式可以有效节省LUT资源,并且提供稳定的存储能力。

四、SRL_STYLE的影响因素:

1、性能

不同的SRL_STYLE实现方式对时序性能有不同的影响。

例如,寄存器实现的SRL通常具有更好的时序特性,而LUT实现的SRL可能在某些情况下提供更高的数据吞吐量。

2、资源消耗

SRL_STYLE的选择直接影响设计中LUT和寄存器的消耗。

例如,使用block实现方式可以节省大量的LUT资源,但可能会增加BRAM的使用。

一般不用使用默认的register就行,因为实际项目中大部分是LUT和BRAM资源不够用,FF资源都有富余。

3、功耗

不同的实现方式也会影响设计的静态和动态功耗。

寄存器实现的SRL可能具有较低的静态功耗,而LUT实现的SRL在活动因子较低时可能具有较低的动态功耗

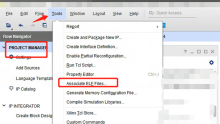

五、如何使用SRL_STYLE?

为了更好地理解SRL_STYLE的应用,我们来看一个简单的设计示例。

假设我们需要实现一个4位移位寄存器,我们将使用不同的SRL_STYLE选项来展示它们的实现方式。

1、使用register选项

module srl_register_example (

input wire clk,

input wire data_in,

output wire data_out

);

parameter SHIFT = 4;

reg [SHIFT-1:0] reg_shift;

always @(posedge clk) begin

reg_shift <= {data_in, reg_shift[SHIFT-1:1]};

end

assign data_out = reg_shift[0];

endmodule

在这个例子中,我们没有SRL_STYLE属性,实际就是用了register选项,综合工具将使用触发器来实现SRL。

2、使用srl选项

module srl_lut_example (

input wire clk,

input wire data_in,

output wire data_out

);

parameter SHIFT = 4;

(* SRL_STYLE = "srl" *) reg [SHIFT-1:0];

always @(posedge clk) begin

reg_shift <= {data_in, reg_shift[SHIFT-1:1]};

end

assign data_out = reg_shift[0];

endmodule

这里,我们指定了SRL_STYLE为srl,综合工具将使用LUT来实现SRL。

3、使用block选项

module srl_block_example (

input wire clk,

input wire [3:0] data_in,

output wire [3:0] data_out

);

parameter SHIFT = 4;

(* SRL_STYLE = "block" *) reg [4*SHIFT-1:0] block_srl;

always @(posedge clk) begin

block_srl <= {data_in, block_srl[4*SHIFT-1:4]};

end

assign data_out = block_srl[3:0];

endmodule

在这个例子中,我们使用了`block`选项,综合工具将使用BRAM来实现SRL。

六、结论

`SRL_STYLE`属性为FPGA设计师提供了灵活的SRL实现选项,可以根据设计的具体需求来选择最合适的实现方式,实现性能、资源和功耗之间的最佳平衡。

一般不用使用默认的register就行,因为实际项目中大部分是LUT和BRAM资源不够用,FF资源都有富余。