版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/weixin_45962327/article/details/137047058

数字逻辑电路根据逻辑功能的不同,可以分成两大类:组合逻辑电路和时序逻辑电路,这两种电路结构是FPGA编程常用到的,掌握这两种电路结构是学习FPGA的基本要求。

1.组合逻辑电路

组合逻辑电路概念:任意时刻的输出仅仅取决于该时刻的输入,与其它时刻的输入状态无关

组合逻辑的Verilog_HDL的描述:根据组合逻辑的电路行为,有两种常用的RTL描述方式。一种是always触发为电平敏感列表信号;另一种是assign的数据流赋值语句。

举例说明:

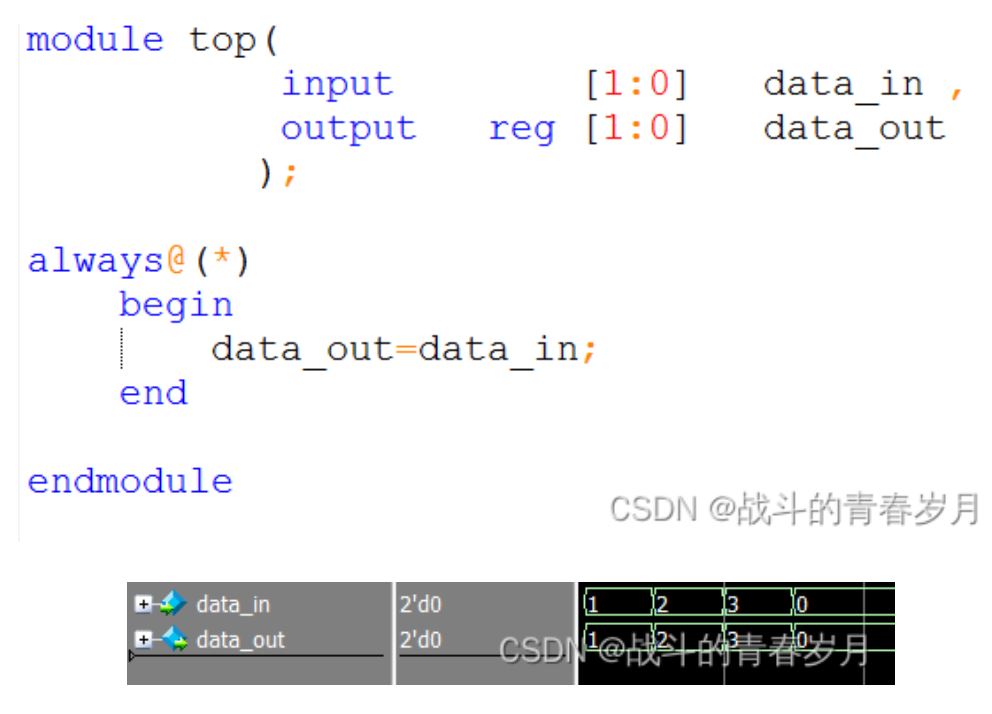

always模块实现组合逻辑

从仿真结果来分析,确实如同组合逻辑电路的概念一样,data_out的输出结果只取决于当前data_in的逻辑数值。

使用always描述组合逻辑

always既可以用于描述组合逻辑电路,也可以用于描述时序逻辑电路。在描述组合逻辑电路时,always在使用上有以下几个特点:

1)在敏感列表中使用电平敏感事件,不要使用边缘敏感事件。

2)为变量赋值使用阻塞赋值(=),不要使用非阻塞赋值(<=)。

另外,在always块内被赋值的变量必须为reg型变量。

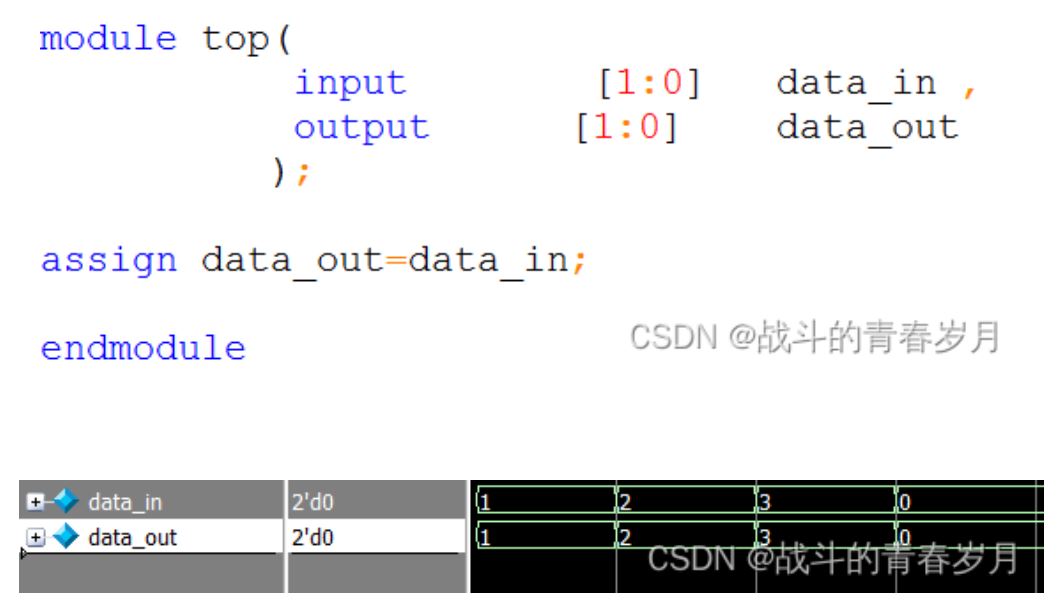

Assign赋值语句实现组合逻辑

使用assign描述组合逻辑电路

用assign描述的部分都是组合逻辑,注意assign只能对wire型变量进行赋值。

2.时序逻辑电路

时序逻辑电路概念:任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关;从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

时序逻辑的Verilog_HDL的描述:根据时序电路的行为,使用always模块的敏感信号为沿变化的进行描述。

举例说明:

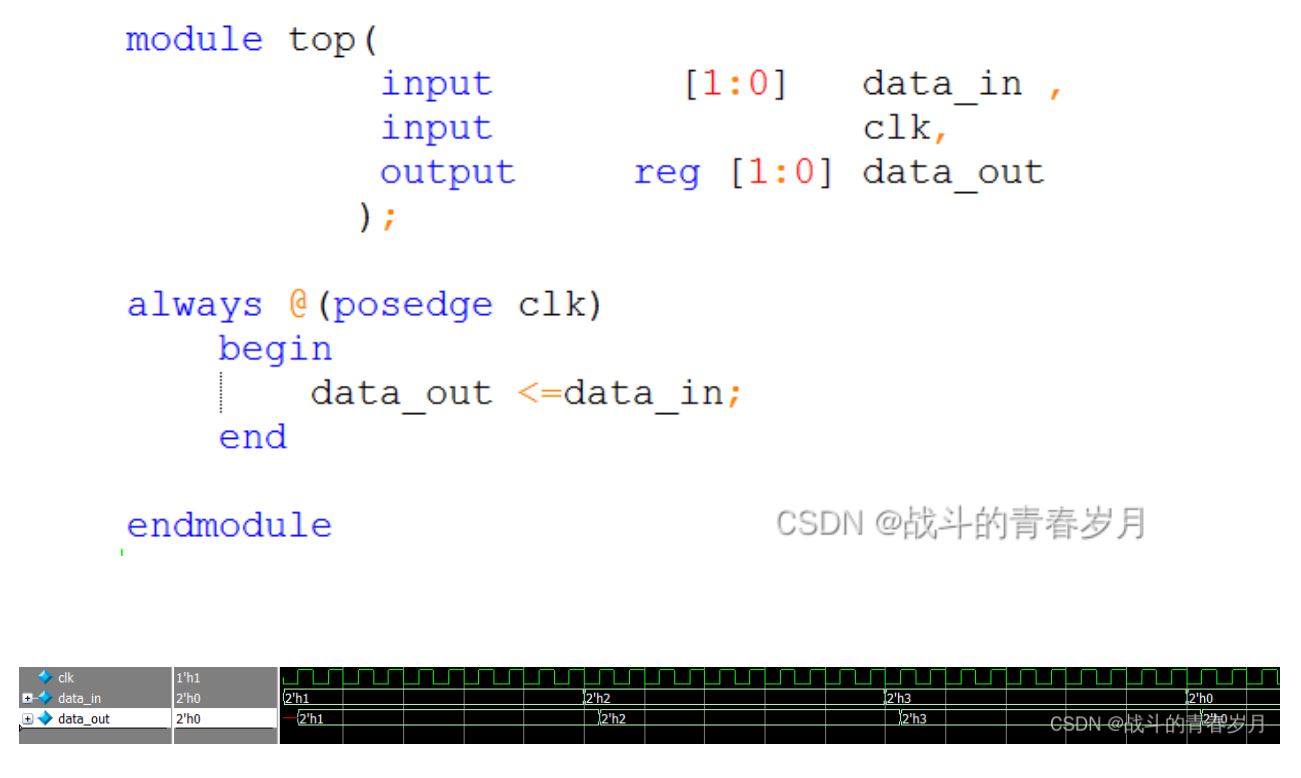

使用always描述时序逻辑

使用always描述时序逻辑

(1)在描述时序电路的always块中的reg型信号都会被综合成寄存器,这是和组合逻辑电路所不同的。

(2)时序逻辑中推荐使用非阻塞赋值“<=”。

(3)时序逻辑的敏感信号列表只需要加入所用的时钟触发沿即可,其余所有的输入和条件判断信号都不用加入,这是因为时序逻辑是通过时钟信号的跳变沿来控制的。

3.章节总结

本章节主要是对编程中常用到的两种时序进行、注意点进行了简单的介绍,想要学习好FPGA的编程,必须要掌握这两种时序。