本文是该系列的第12篇,上一篇介绍了在System Generator设计中使用Black Box调用HDL代码的方法,并使用Simulink+Vivado Simulator进行了协同仿真。本文将对该block及其中涉及到的MATLAB配置文件作详细介绍。

HDL文件使用限制

想在Black Box中导入HDL文件,Verilog/VHDL文件必须遵循以下限制:

MATLAB配置文件

将需要导入的VHDL/Verilog文件放在slx文件所在目录下。添加一个Black Box到model中,会自动弹出一个窗口,选择好需要关联的HDL文件。初始化完毕后,软件会自动生成一个name_config.m的MATLAB配置文件(name为HDL文件名称),这个文件与设置的HDL文件相对应,配置了HDL文件在Simulink环境中的具体信息。

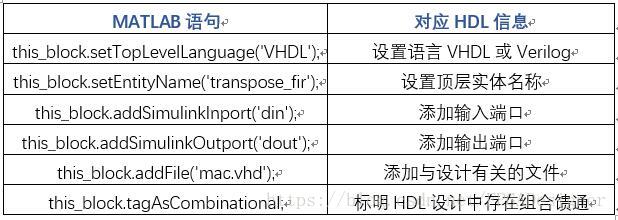

通常这个M文件不修改也可以使用,当HDL设计比较复杂时还是需要手工修改(如第11篇中的设计),因此了解该配置文件仍有必要。下表给出了配置文件中的关键语句及对应信息:

上表中的“组合馈通”(combinational feed-through)指的是输入没有经过任何寄存器直接到达输出(即路径上只存在组合逻辑)。当HDL设计中存在这样的路径时,必须使用上表中语句申明。

为了保证Black Box在Simulink中能够正确运行,MATLAB配置文件中还包含以下三个部分:

1.输出端口设置:

软件是无法检测到我们如何规定输出端口的某些信息的,因此这部分必须我们手工设定,如下:

dout_port = this_block.port('dout');

dout_port.setType('Fix_26_23');

dout_port.setRate(theInputRate);

上面将输出端口速率设置与输入端口速率不同。如果输出端口速率为输入端口速率的2倍,则可以设置为:“dout_port.setRate(2*theInputRate);”。这部分设置主要是让Simulink可以正确的从Black Box中获取输出结果,保证仿真正确运行。

2.输入类型检查:

检测该block的输入数据类型是否正确,如不正确则提示相关信息(如这里HDL中din为12Bits数据,此处检测向block输入的数据是否为12Bits):

if (this_block.inputTypesKnown)

if (this_block.port('din').width ~= 12);

this_block.setError('Input data type for port "din" must have width=12.');

end

end

3.输入速率检查:

以下语句便是完成了时钟信号速率的设置,setup_as_single_rate函数中读取了Simulink环境设置的系统采样率,如果采样率设置正确,则会用该速率驱动时钟信号clk:

if (this_block.inputRatesKnown)

setup_as_single_rate(this_block,'clk','ce')

end

setup_as_single_rate这个函数内容比较多,这里不再赘述。读者可以按照本系列第11篇的设计进行,打开相应的MATLAB文件查看。

block参数设置

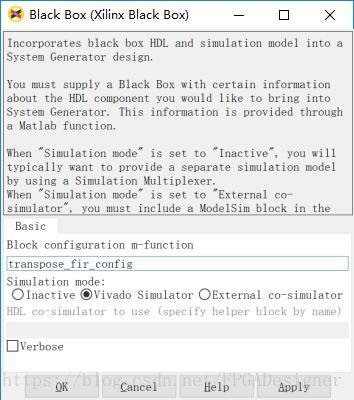

Black Box的参数设置界面如下:

“Block confituration m-function”设置了MATLAB配置文件,该文件一般与slx模型文件在同一目录下。编辑框中不能包含后缀“.m”。

“Simulation mode”设置仿真时所选用的模式:

需要添加对应ModelSim block,且在“HDL co-simulator to use”中标明block名称。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人