作者: ChuanjieZhu

前言:

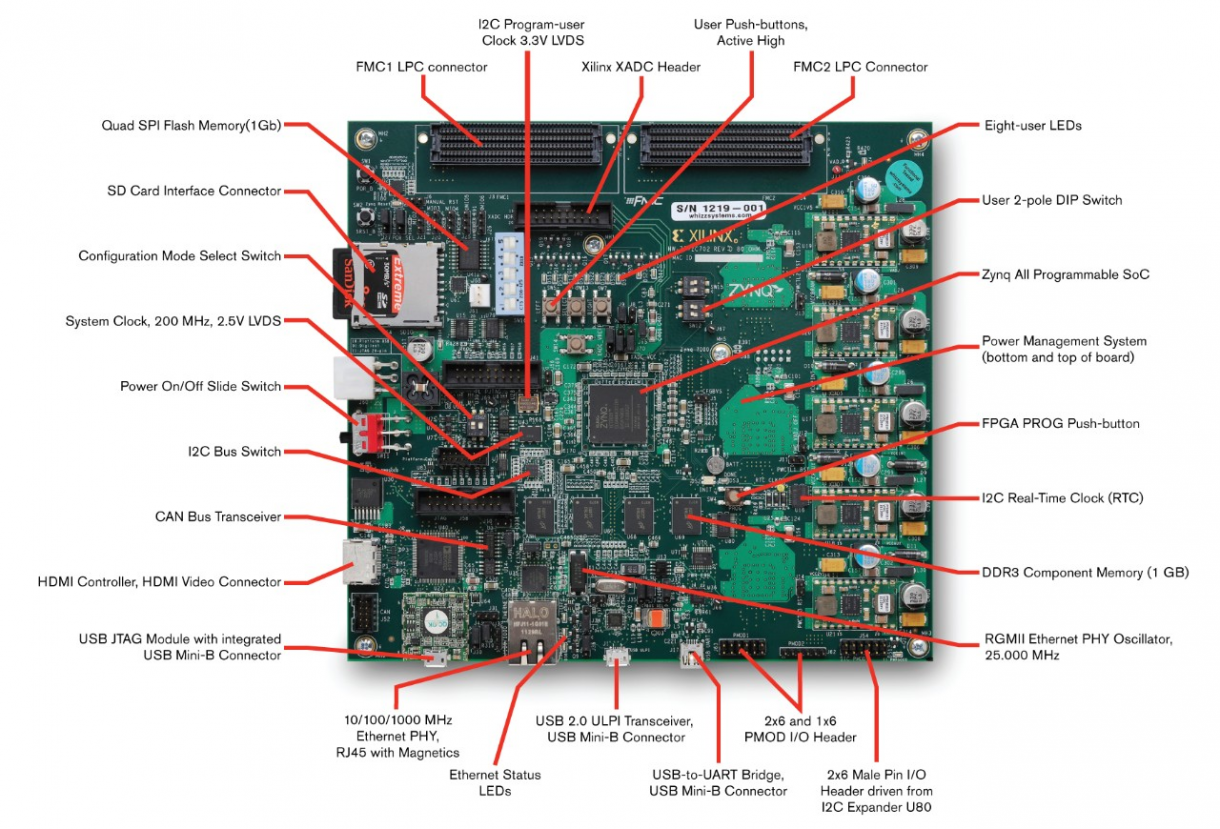

学习Xilinx的ZYNQ 7000系列,用的板子是zc702(注意不是zedboard),SOC型号是xc7z020。虽然设计思路一样,但不同的套件引脚和io标准是有区别的,zc702评估板的的外观图如下,可以对照下自己的板子:

作为入门体验,本设计实现的功能是控制8个流水灯,循环闪烁,每隔1s移位一个。我们用到的部分是SoC和user LEDs。声明一下本文仅仅用PL编程,并不是PS+PL。

步骤:

1.新建Vivado工程,这里命名为LedTest,next选择新建PTL Project,next选择Boards,输入z7c02,单击后finish:

各类文件所在文件夹,source选项卡下:

2.新建设计文件,命名为Led(这里用到了差分时钟信号,后面会介绍):

module Led(

input clk_p,

input clk_n,

input RSTn_i,

output reg [7:0]LED_o

);

reg [31:0]C0;

IBUFGDS IBUFGDS_inst (

.O(CLK_i),

.I(clk_p),

.IB(clk_n)

);

always @(posedge CLK_i)

if(RSTn_i)

begin

LED_o <= 8'b0000_0001;

C0 <= 32'h0;

end

else

begin

if(C0 == 32'd200_000_000)

begin

C0 <= 32'h0;

if(LED_o == 8'b1000_0000)

LED_o <= 8'b0000_0001;

else

LED_o <= LED_o << 1;

end

else begin

C0 <= C0 + 1'b1; LED_o <= LED_o; end

end

endmodule

3.仿真。这一步可有可无。规范设计应该有。新建仿真文件,命名为Led_tb:

module Led_tb();

reg CLK_i;

reg RSTn_i;

wire [7:0] LED_o;

parameter ClockPeriod=10;

initial

begin

CLK_i=0;

forever

#(ClockPeriod/2) CLK_i=~CLK_i;

end

initial

begin

RSTn_i=1;

#100 RSTn_i=0;

#100 RSTn_i=1;

end

Led Led_inst(

.CLK_i(CLK_i),

.RSTn_i(RSTn_i),

.LED_o(LED_o)

);

endmodule

仿真时没有用差分时钟,所以需要修改下源文件的时钟输入信号,改为:input CLK_i; 即可。另外为了快速看到流水灯信号变化,可以将源文件判断中的计数信号C0改为100。

4.添加约束。

这里约束文件的作用是给各个信号分配管脚(Pin),指定电气标准。

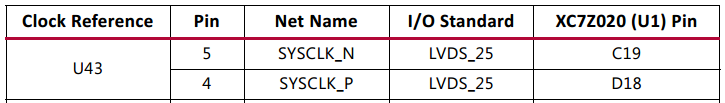

官方的user guide里:

可以看到系统时钟频率为200M,输出电压是差分的,差分信号可以抑制共模噪声,使用输入的差值,而我们要把它转化为正常信号使用,转化方法是调用IBUFGDS模块:

IBUFGDS IBUFGDS_inst (

.O(CLK_i), // Clock buffer output

.I(clk_p), // Diff_p clock buffer input (connect directly to top-level port)

.IB(clk_n) // Diff_n clock buffer input (connect directly to top-level port)

);

新建约束文件,命名为Led_pin:

set_property PACKAGE_PIN D18 [get_ports {clk_p}]

set_property IOSTANDARD LVDS_25 [get_ports {clk_p}]

set_property IOSTANDARD C19 [get_ports {clk_n}]

set_property IOSTANDARD LVDS_25 [get_ports {clk_n}]

set_property PACKAGE_PIN G19 [get_ports {RSTn_i}]

set_property IOSTANDARD LVCMOS18 [get_ports {RSTn_i}]

#GPIO PMOD1

set_property PACKAGE_PIN E15 [get_ports {LED_o[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[7]}]

set_property PACKAGE_PIN D15 [get_ports {LED_o[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[6]}]

set_property PACKAGE_PIN W17 [get_ports {LED_o[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[5]}]

set_property PACKAGE_PIN W5 [get_ports {LED_o[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[4]}]

#GPIO PMOD2

set_property PACKAGE_PIN V7 [get_ports {LED_o[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[3]}]

set_property PACKAGE_PIN W10 [get_ports {LED_o[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[2]}]

set_property PACKAGE_PIN P18 [get_ports {LED_o[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[1]}]

set_property PACKAGE_PIN P17 [get_ports {LED_o[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_o[0]}]

也可以综合后在IO planning里约束,约束好后右击 export io ports,保存到之前新建的约束文件中:

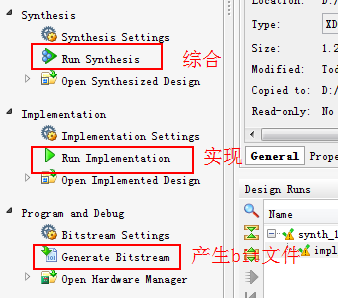

5,依次 综合,实现,产生bit文件。

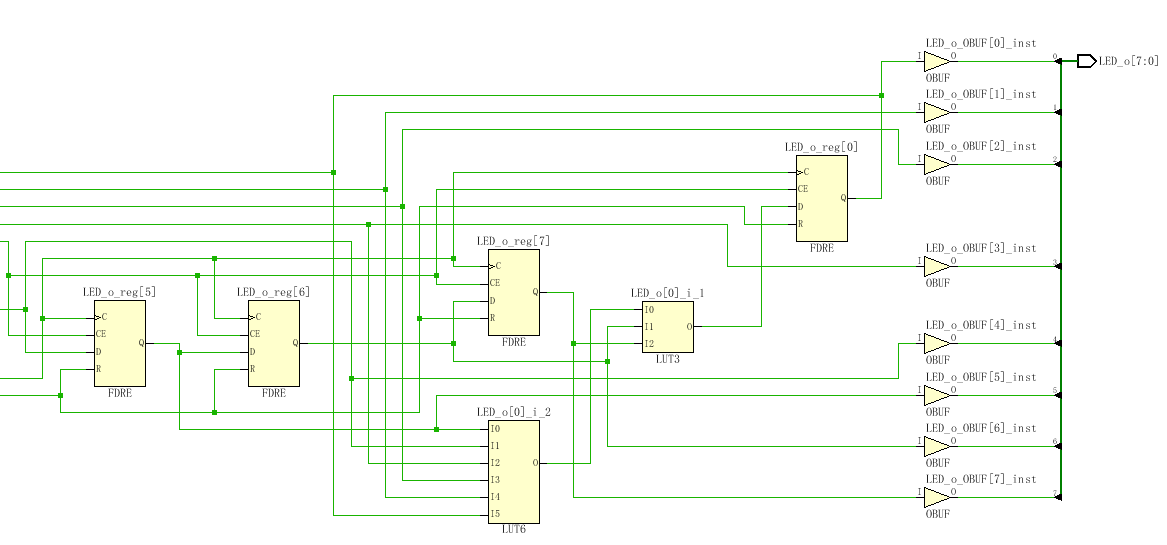

综合是将RTL级描述转化为门级描述,综合时将进行逻辑优化,并映射到Xilinx的器件原语。综合后设计表现为层次(模块的实例)和基本元素(查找表,触发器,RAM,DSP,时钟,IO等)的互连网表。本设计综合后的部分网表结构:

实现是将综合的网表加入物理约束和时钟约束相当于模拟实际电路的工作。

生成比特流数据(可编程文件)是为了下载到硬件。

6.给fpga上电,连接好下载线。

7.下载程序。

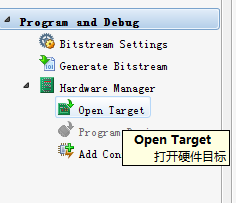

点击open target,如果是第一次下载,点击open new target,一直next,finish后,点击program device,选择xc7z020_1,在弹出的对话框里点击program,等待下载完成,流水灯就闪起来了,每隔1s移位一次,从左3往右循环。

总结:

Vivado环境下编写纯PL代码,熟悉整个设计流程,包括仿真,添加约束,综合,实现,生成可编程文件,下载程序。其中可能会卡住的地方就是系统时钟的使用和约束文件的编写,牵涉到的一项重要技能就是学会查阅官方文档,看电路图和user guide,这些东西虽然可以轻易下载到,但由于是英文文档或第一次接触,往往会被难住。

本文转载自: https://blog.csdn.net/u014485485/article/details/78056980