作者:Art Pini,Digi-Key 北美编辑

我们处在一个由数字计算机控制的模拟世界里。因此,物联网 (IoT) 设备的设计人员需要将模拟值高效地转换为采样数字表示。答案看似简单,使用一个前置的模数转换器 (ADC) 便能解决问题,然后 ADC 并非千篇一律。因此,设计人员需要了解各种拓扑,以及它们与应用的对应关系。

例如,ADC 可能设计用来优化采样率、功耗和精度等不同特征。本文将会讨论一些常见 ADC 架构的设计要求,然后介绍采用这些架构的应用,并展示其实现方法。

ADC 的作用

ADC 是一种常用的电子集成电路或模块化器件,用于将模拟信号(通常为电压)转换为一系列经采样的离散数字表示(即数字)。ADC 执行三种不同操作:采样、量化和编码。它们构成了电压计、示波器和频谱分析仪等许多常见数字仪器的核心。它们还应用于数字电路的前端,用于处理麦克风、加速计、光学传感器和其他需要将输出转换为数字域的变送器所提供的模拟信号,从而让微处理器能够处理这些数据。

目前人们已开发出多种 ADC 架构或拓扑来对模拟信号进行采样和数字化。每种形式的 ADC 都有自己的特性、优势和不足之处。针对具体应用选择特定类型的 ADC,往往取决于速度、分辨率、精度、功耗和物理尺寸等测量要求。

ADC 的关键特征

ADC 必须执行的第一项操作是对模拟信号进行采样。采样操作由采样和保持电路或跟踪和保持电路执行。采样操作或奈奎斯特定理要求,采样率必须高于信号带宽的两倍,才能从数字化样本重建模拟信号。因此,ADC 的第一个重要特征就是采样率,它决定了可以进行数字化的最大信号频率分量。

ADC 必须对每个样本进行量化,将采样的电压分解为有限数量的离散幅度电平。此特征通常描述为分辨率位数。例如,如果将信号分解为 8 位,则意味着存在 28 即 256 个离散电平。16 位 ADC 会将电压范围划分为 65,536 个量化电平。

分辨率和最大采样率均取决于 ADC 硬件。一般而言,ADC 的分辨率越高,最大采样率越受限制。

ADC 的精度同时取决于分辨率和采样率。分辨率会影响幅值精度和准确性。其他影响幅值精度的因素还包括量化过程的线性度和垂直噪声的影响。采样率决定了定时精度和准确性。

物理尺寸和功耗是另外两个依赖电路拓扑的属性。它们对于一些具有尺寸或可用功率限制的应用,例如物联网设备或电池供电的便携式仪器而言,是非常重要的考虑因素。物理尺寸和功耗高度依赖 ADC 拓扑。

闪速、直接或并行?

在概念上,最简单的数字化仪莫过于闪速 ADC。闪速 ADC 也称为直接或并行 ADC(图 1)。

图 1:闪速 ADC 使用多个阈值电压均匀递增的比较器,将模拟电压转换为数字值。该示例展示了一个具有 8 电平分辨率的 3 位 ADC。(图片来源:Digi-Key Electronics)

闪速 ADC 的输入通常源自采样和保持或跟踪和保持电路,模拟输入在此电路中采样并在转换期内保持恒定。经采样的信号被应用于一系列模拟比较器,这些比较器的阈值电压在 ADC 输入电压范围内均匀间隔,间隔值等于一个最低有效位 (LSB)。每个比较器的输出会在输入电压超过分压器为该比较器设定的阈值时改变状态。图中的示例显示了一个 3 位 ADC,它需要 7 个比较器来生成 8 个可能的状态。

一般情况下,一个 N 位闪速转换器需要 (2N-1) 个比较器。比较器所产生的就是所谓的“温度计码”。输入电压越高,自底而上达到“1”状态的比较器数量就越多。此代码将应用于一个优先编码器,并由该编码器将其转换为二进制码。

闪速转换器的主要优势是速度。转换时间仅包括比较器和解码器的延迟。商用闪速转换器的最大采样率可达每秒 5 千兆次采样 (GS/s)。闪速转换器分辨率的限制因素就是所需要的比较器数量。8 位闪速 ADC 需要 255 个比较器。

分辨率每增加一位,该数量就会增加一倍。这意味着 ADC 的物理尺寸会随分辨率呈指数级增长。此外还会造成另一项限制,即闪速转换器所需的功率。这会限制它在线路供电型应用中的使用。闪速分辨率的实际限制约为 8 位。

二进制编码

ADC 的二进制输出可采用多种方式进行编码。如果所转换的信号为单极信号,则通常将其编码为单极标准二进制码。此代码将零值表示为全零 (0000…),将最大输入值表示为全一 (1111…)。

如果信号为双极信号,则通常表示为偏移二进制或二的补码二进制。表 1 详细说明了一个 4 位示例。

表 1:双极数字信号的常见二进制编码。二的补码二进制是微处理器或数学处理器最常用的编码方式。(图片来源:Digi-Key Electronics)

二的补码二进制编码是大多数基于微处理器或数学处理器的系统所用的编码类型,因为此编码有利于数学运算。

流水线、分段式和两步式 ADC

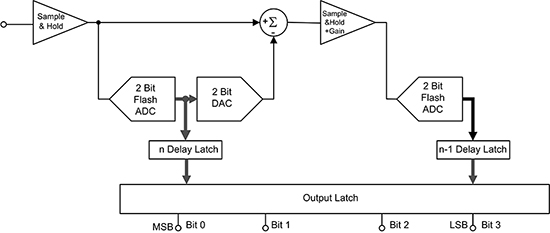

可通过将转换操作分解为两步或更多步并在每一级转换较少的位数,来减少闪速转换器中的比较器数量。如果将闪速 ADC 拆分为两个部分,则称其为两步式或分段式 ADC。如果将其拆分为两个以上的部分,则称其为流水线 ADC。两步式 ADC 仍能以每秒几百兆次采样 (MS/s) 的速率进行采样(图 2)。

图 2:4 位两步式或分段式 ADC 的功能框图显示,它将 4 位转换器分解为两个 2 位转换器,以减少比较器的数量。(图片来源:Digi-Key Electronics)。

此两步式转换器将需要 15 个比较器的 4 位转换器分解为两个 2 位的分段。每个分段使用三个比较器,共计六个比较器。该转换器的工作原理是先转换两个最高有效位 (MSB)。第一个分段的数字输出包含一个数模转换器 (DAC),用于将信号转换为模拟值,并从输入信号中将其扣除。

所得的差值会被放大,并用于转换两个 LSB。然后在输出锁存器中捕获组合结果。该转换过程将会重复两次,因此最大采样率将会低于闪速转换器的采样率。例如,Analog Devices AD9203ARUZRL7 便是一个 10 位、40 MS/s 流水线 ADC,可用于解决高速模数转换存在的问题。

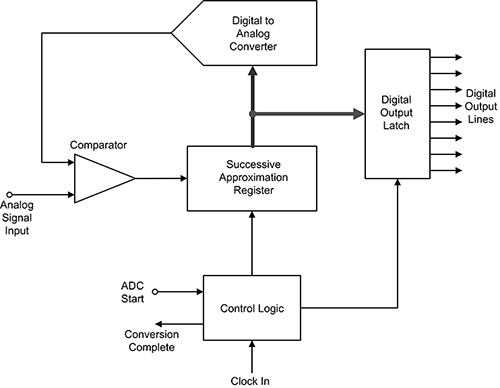

逐次逼近寄存器 (SAR) ADC

当应用需要更高的分辨率,同时不需要闪速或流水线 ADC 那么快的速度时,逐次逼近寄存器 (SAR) 转换器不失为一种不错的选择(图 3)。SAR ADC 的分辨率为 12 到 16 位,采样率高达 1 到 2 MS/s。

图 3:SAR ADC 以中低功率要求实现了良好的分辨率。(图片来源:Digi-Key)

与闪速 ADC 一样,SAR ADC 使用前置采样和保持或跟踪和保持电路,在转换过程期间维持样本值。源自采样和保持电路的信号将施加到比较器上。逐次逼近寄存器从量程中段开始,使用 DAC 将该值转换为模拟电压。

此“猜测”电压将与比较器的信号输入进行比较。如果比较器输出保持低电平,则将寄存器值递增四分之一量程。基本上,寄存器值按照两个步长因子降低或升高,直至比较器指示 DAC 转换的寄存器内容等于输入信号电压。这时,转换器会发出“转换完成”的信号,并将数字值锁存到输出锁存器中。

此转换时间与 ADC 分辨率成正比,而分辨率取决于寄存器的长度。SAR ADC 以中低功率要求实现了良好的分辨率。例如,Maxim Integrated 的 MAX11665AUT-T 便是一款低成本、低功耗的 SAR ADC。作为一款每秒 500 千次采样 (kS/s) 的 12 位 SAR ADC,它非常适合对传感器输出进行数字化。

双斜率积分 ADC

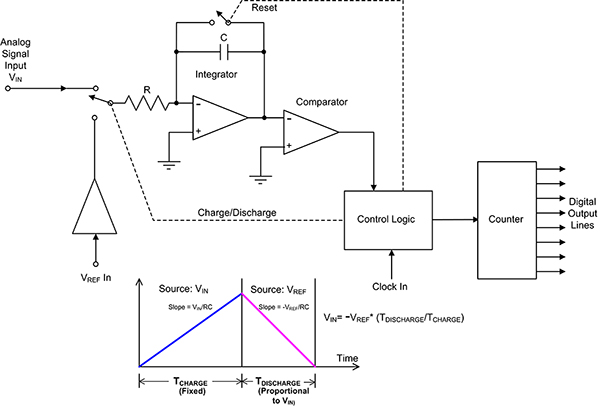

积分 ADC 具有高分辨率,同时可最大限度降低噪声影响。双斜率 ADC 是最常见的积分 ADC(图 4)。

图 4:双斜率积分 ADC 的方框图中包含的图表显示了如何使用充电/放电时间确定未知的输入电压。(图片来源:Digi-Key Electronics)

一开始,输入连接到积分器。输入信号对电容器 C 进行固定时间充电。充电时间结束后,积分器被连接到基准电压。这会将电容器放电到比较器所确定的零值。同时有一个计数器会测量电容器放电所用的时间。该时间与充电周期内施加于电容器的输入电压成正比。借助已知的充电时间与测量的放电时间之间的简单关系,即可计算出输入电压。

由于信号输入被应用于积分器,因此积分器的均化效应会将任何噪声信号的影响降至最低。双斜率转换器是需要高精度的高分辨率应用的理想选择。常见的分辨率为 12 到 16 位,最大采样率可达 100 KS/s。

双斜率 ADC 最广为人知的应用是数字电压计(DVM 或 DMM)。Maxim Integrated 的 ICL7109CPL+ 型 12 位三态输出 ADC 便是一种双斜率转换器,适用于以高达每秒 30 次的速率测量压力、速度或流量等模拟信号。

三角积分 ADC:低频率、高分辨率

三角积分 ADC 可针对低频信号提供最高的分辨率(16 到 24 位)。与双斜率 ADC 一样,它是另一种类型的积分数字化仪(图 5)。输入信号通过一个加法器施加到积分器。积分器的输出随即施加于一个闩锁比较器,并在其中与零电压(接地)信号进行比较。如果积分输出不为零,则会反馈比较器输出,从而使积分器输出更接近零。以转换器的时钟速率重复此过程,直至积分器输出达到零。比较器输出构成一个串行数据流,即转换器的数字输出。

三角积分 ADC 的采样速率远高于设计采样率要求的速率。

请注意,图中的转换器时钟速率快于输出样本的时钟速率(比例因子为 K)。此“过采样”提供的额外样本将被用于对转换器输出进行数字滤波。使用抽取器将输出采样率恢复至指定的样本时钟速率。

Analog Devices 的 AD7734BRUZ 型 ADC 是一款 24 位、4 通道三角积分数字化仪,适用于各种工艺和工业控制应用。

图 5:三角积分 ADC 在音频、工艺和工业控制应用中广泛用于低频信号的高分辨率数字化。(图片来源:Digi-Key)

表 2 概括了所讨论的五种 ADC 类型的分辨率和最大采样率。

表 2:本文所讨论的五种 ADC 类型的 ADC 工作特征。(图片来源:Digi-Key Electronics)

拓扑选择示例

以一个应用为例:该应用对一个使用 40 kHz 变送器的便携式超声测距仪的信号进行数字化。目标反射为发射脉冲幅度的 -40 dB (1/100)。

必须以至少两倍于 40 kHz 信号频率的速率进行信号采样。最好以 40 kHz 的四倍或更高倍数进行采样,因此目标采样率范围为 160 kHz 或更高。而且,最好设置不低于预期值 40 dBm 10 倍的分辨率,即 60 dB。根据经验规则,每 6 dB 需要 1 位分辨率,因此需要 10 位以上分辨率的 ADC。 此外,作为便携式仪器,还需要考虑功耗问题。参考表 2,逐次逼近转换器成为最佳选择。前面提到的 SAR ADC 示例器件 Maxim Integrated MAX11665AUT-T 便非常适合这一应用。

总结

由于无法同时兼顾最大采样率和分辨率,因此 ADC 的选择主要在于这两项特征的权衡。根据具体应用,物理尺寸和功耗等其他考虑因素也可能起着重要作用,在选择过程中应给予应有的重视。

文章转载自:Digikey