作者:Hello,Panda ,文章转载自:ZYNQ分享客微信公众号

MIPI是移动领域最主流的视频传输接口规范,没有之一,目前应用最广泛的是MIPIDPHY和MIPI CPHY两组协议簇(另外还有MIPI MPHY,属于高速Serdes范畴,应用不那么广泛),其中CSI-2主要用于图像接入(一般是接Sensor),DSI-2主要用于图像输出(一般是输出到显示屏)。

本文主要以CSI-2为例进行仔细说明,DSI-2雷同,举一反三即可。

1 接口协议比较

关于MIPI DPHY和MIPI CPHY的详细物理层协议和CSI-2/DSI-2协议咱们自己下载官方英文版细细品读即可,这里主要讲关键点。

1.1 物理层

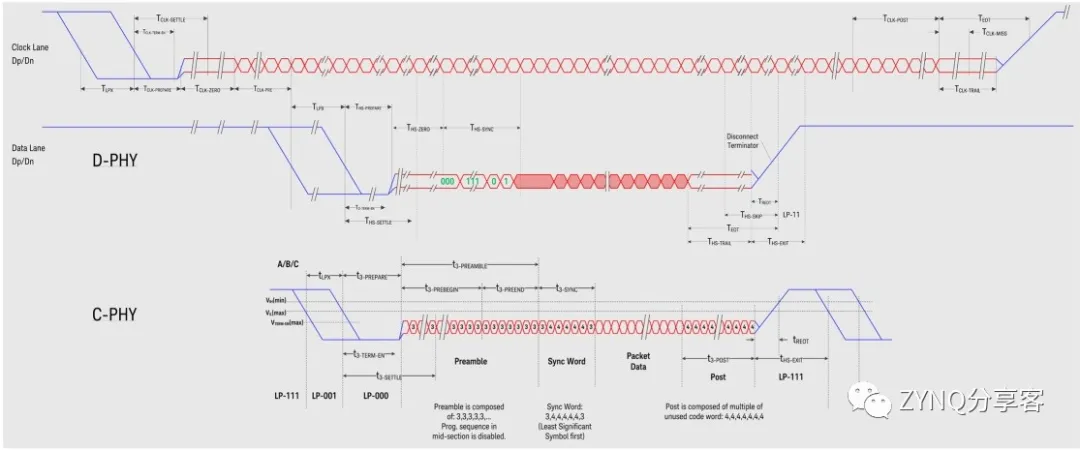

开局一张图(见下图1),内容是干货,MIPI CPHY和DPHY物理层之间的差异全在这张图里面了。

图1 MIPI DPHY和CPHY物理层直观比较图

从图1可以看出,最直观的差异是DPHY是源同步系统,有专门的同步时钟通道,但是CPHY没有同步时钟,时钟是嵌入到数据中的。显然的,实现嵌入时钟的目的是为了增加带宽,肯定会涉及到编码,物理层的结构必然是完全不同,单从线路上看,CPHY是一个A/B/C三线系统。

MIPI DPHY的物理层,咱们大家都很清楚,一对时钟,几对数据,接收端根据时钟边沿采样数据,找到0xB8的同步头,物理层实现就算是齐活了,但MIPI CPHY不同,因为它不传输时钟,那么要接收CPHY的数据,必须先恢复时钟,然后再用恢复的时钟采样数据并寻找同步头,最后还需要进行数据解码恢复出最初的发送的内容(发送端的过程相反)。

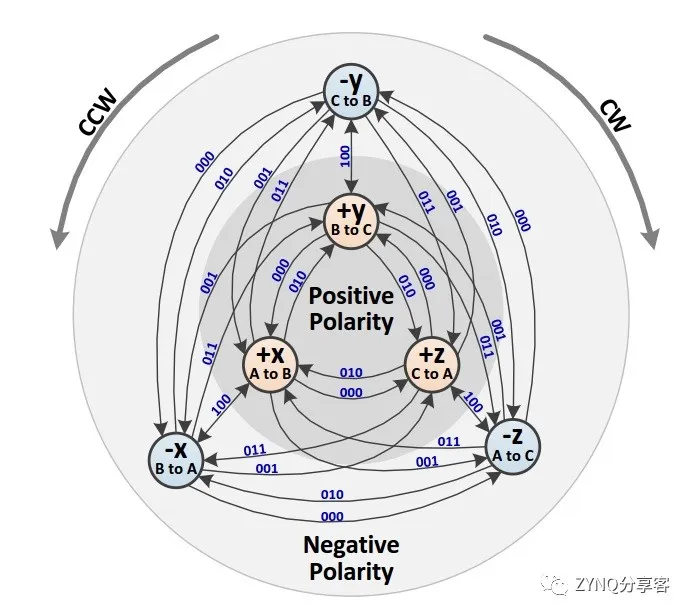

那么,CPHY物理层到底是怎么实现嵌入时钟这一关键步骤的呢?请看下图2和图3。

图2 CPHY“线态”变化图

图3 CPHY接口等效电路图

结合图2和图3,CPHY物理链路(A/B/C线)上传输的是不同的电平,通过A-B,B-C,C-A的电平运算,恢复出+x,-x,+y,-y,+z,-z六种不同的线态,通过前后线态的旋转方向,相位和极性恢复出编码符号,再通过连续7组符号解码出16bit的数据,整个过程见下图4。

图4 数据恢复过程图

为何要选择这比DPHY复杂多的物理层呢?一切都是为了提升带宽,从图2可以看出,某种线态的可能有5种不同的变化,那么它每个符号可编码的数据为log2(5) = 2.3219,理论带宽为DPHY的2.3219倍,每16bit数据编码成7个符号,带宽优势明显。

1.2 CSI-2层

MIPI CPHY和MIPI DPHY的CSI-2层协议大致相同,细节上的差异如下:

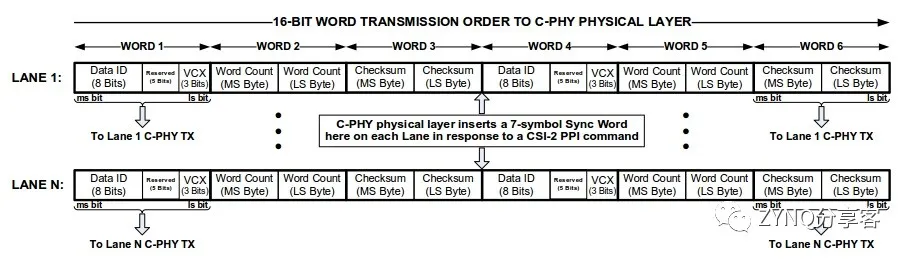

(1) DPHY以Byte为单位进行数据组织;CPHY以16bit Word为单位进行数据组织;

(2) DPHY 的短帧和长帧的帧头信息与数据的组织方式相同;CPHY则是固定每个通道为6×16bit的帧头信息(短帧信息),见下图5。

图5 CPHY CSI-2数据组织

因此,在CSI-2解包逻辑尚无法完全共用。

2 FPGA实现

MIPI接口电平比较特殊,LP模式下为1.2V的LVCMOS电平,DPHY在HS模式下为SLVS-400电平,CPHY在HS模式下需要做电平减法运算。

2.1 硬件电路

就目前而言,直接支持MIPI DPHY的FPGA主要有Xilinx UltraScale+系列(1.5Gbps/Lane Max)Lattice Crosslink(1.5Gbps/Lane Max)及Lattice Crosslink NX(2.5Gbps/lane Max),其它型号的PFGA均需添加额外的电平转换电路将信号转换为LVDS。

(1) DPHY,低于800Mbps/lane速率,使用电阻网络即可;高速率的需选用专门的电平转换芯片,如MC20901、LT89101L等;

(2) CPHY,因为需要做减法运算,故可用专门的告诉比较器(或Repeater),结果以LVDS电平输出。

2.2 逻辑实现

逻辑实现的差异主要在物理层,CPHY和DPHY完全不同。

2.2.1 MIPI DPHY

MIPI DPHY属于源同步系统,转换为LVDS电平后就是一个通用的ISERDES逻辑,主要是时钟方案有两种考虑:

第一种:使用PLL、MMCM或DLL,此种方案对PLL的锁定时间有较高的要求,通常要求us级才能保证在时钟不连续模式下正常锁定,当然具有专用DPHY逻辑的器件有专门的PLL电路实现。这种方案的好处是不易受时钟毛刺的影响,接收较为稳定。

第二种:在源同步时钟基础上使用专门的时钟buffer分频(如Xilinx 7系列的BUFR),这种方案可适应任意速率,不需要预先设定速率来配置锁相环电路,缺点是易受时钟毛刺影响,出错率稍高。

2.2.2 MIPI CPHY

MIPI CPHY的难点是时钟恢复,在FPGA系统中,没有针对MIPI CPHY的专用时钟恢复电路(CDR),因此,需要充分利用CPHY的线态编码均衡和FPGA可编程延时电路的特点来实现CDR,这种方案理论上要求FPGA内部延时逻辑约精确越好,LUT时钟性能越高,这样会把时钟恢复误码和抖动降到最低。时钟恢复完成后,线态解码、符号解码和数据恢复流程见图4。

总之,MIPI CPHY在MIPI DPHY的基础上成倍增加了带宽,减少了线对数量,在高速大靶面传感器和高分高刷新移动设备OLED应用上越来越普及。

2.2.3 资源占用

Panda君在Xilinx kintex-7系列FPGA对MIPI DPHY+CPHY 接收IP进行了验证,占用资源SliceLUTs为2352个,Slice Registers 3401个。本方案亦可在紫光同创、高云等国产FPGA上降速实现。

图5 MIPI DPHY+CPHY Vivado工程图