作者:Nick Liu ,文章来源:Ingdan FPGA微信公众号

Xilinx器件进位链功能描述

FPGA芯片的三个主要资源主要包括可配置逻辑单元(CLB)、存储单元、运算单元、一流的I / O资源和布线资源等。其中,CLB在FPGA中最丰富,在7系列的FPGA中,一个CLB中有两个Slice,Slice中包含4个LUT6、3个数据选择器MUX,两个独立进位链(Carry4,Ultrascale是CARRY8)和8个主轴。这里我们主要介绍Carry4。

高精度延时电路可以广泛用于家用电器、检测与控制、数据采集和控制等领域。通常情况下,延时电路设计方法众多,如采用计数器、锁相环、差频和专用精密延时器件等。随着数字电路技术的发展,数据信号采集速度和精度有了很大提高,各类工程应用对延时电路设计的指标也越来越高。

使用FPGA内部进位链单元所提供的较小而稳定的延时来构建延时链,可以实现纳秒级高精度的延时发生器和信号检测。

1、 Xilinx器件进位链原理

Xilinx公司的7系列FPGA来说,其内部都具有CARRY4这一基本设计单元。通常情况下,进位链资源能够配合LUT资源完成进位实现全加器。进位链级联数越多,造成的路径延迟就会越大,这样会让时序十分的紧张。但是在这里我们恰恰要利用的就是进位链的固定的延时,通过对CARRY4原语的多次实例化调用,就能够实现进位链延时。

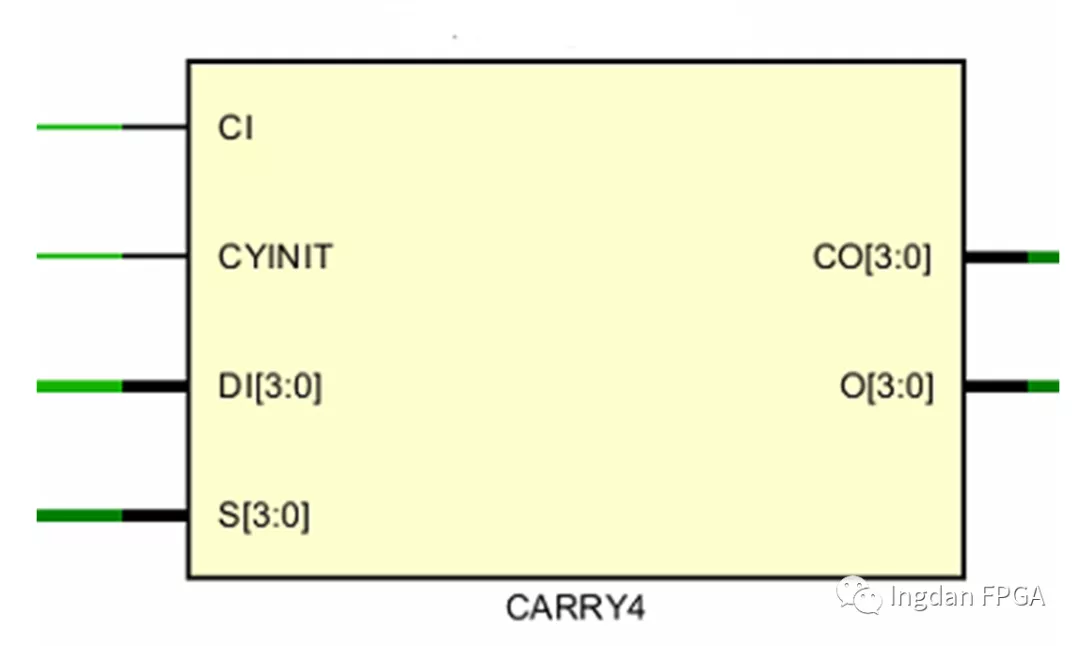

首先,我们来看下CarryChain的结构原理,其输入输出接口如下:

图1:CARRY4的例化

其中,

CI是上一个CARRY4的进位输出,位宽为1;

CYINT是进位的初始化值,位宽为1;

DI是数据的输入(两个加数的任意一个),位宽为4;

SI是两个加数的异或,位宽为4;

O是加法结果输出,位宽为4;

CO是进位输出,位宽为4。

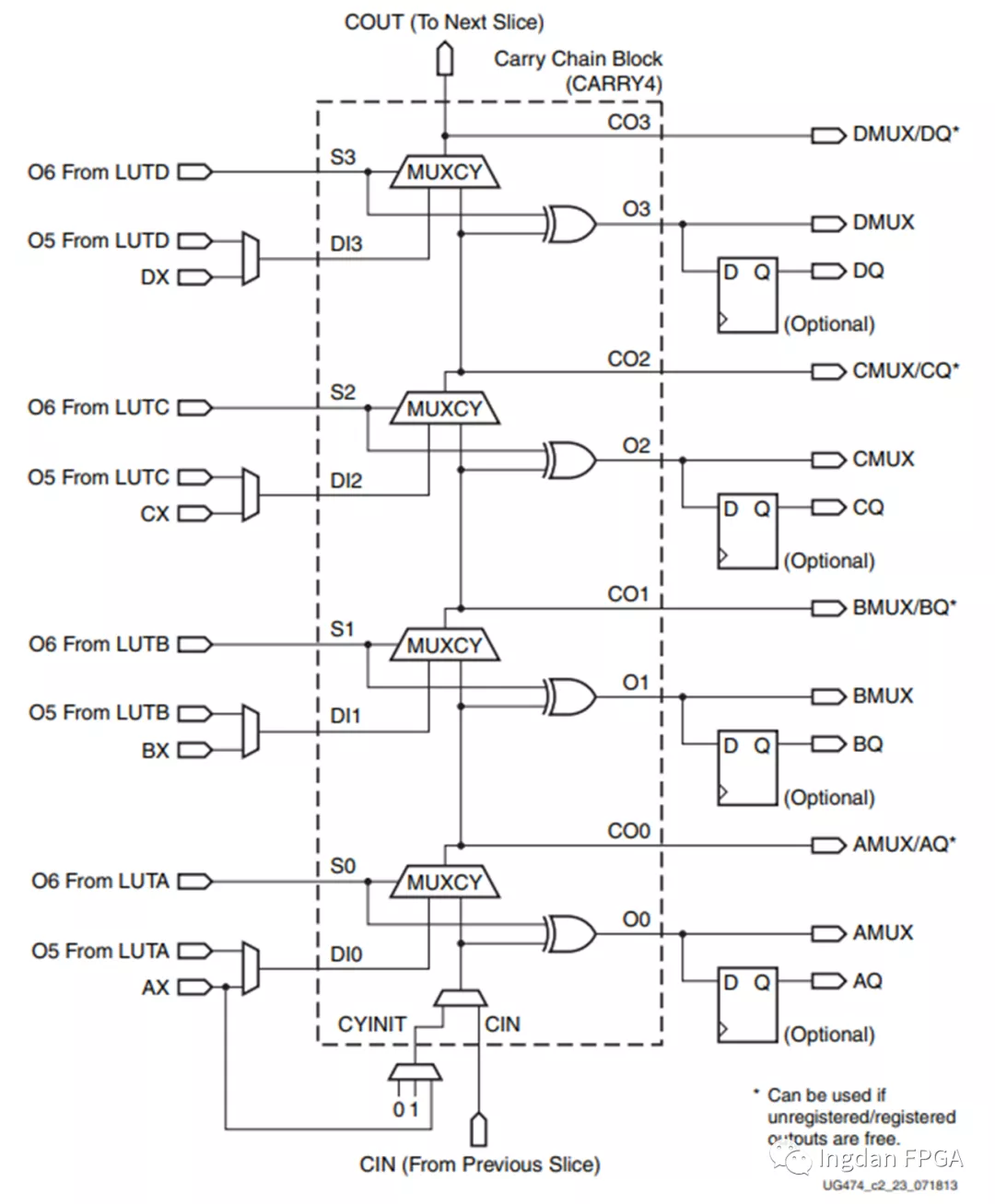

其次,Carry4的内部结构如下图所示:

图二:CARRY4单元结构

CARRY4单元具有的数据输入DI[3:0]和数据选择输入S[3:0]分别对应其内部的4个进位选择器的数据输入端和选择输入端,通过调整DI和S就可以改变进位链的选择和具体的抽头位置,从抽头位置到进位链的末端输出之间所经过的时间间隔即为所需要的延时。其输出可以选择CO0、CO1、CO2、CO3四个通路。

据上述图中,可以看到,当S0-S3均为1(S[3:0]=4‘b1111)时,上一级进位链的结果CIN可以一路向上,从CO3输出(也可以选择CO0/CO1/CO2),其结果和CIN相等,并且其延时完全取决于进位链的器件延时,可以做到ps级的延时。这里每一个进位链的延时最小是53ps(7系列FPGA)。

2、进位链延时原语实现

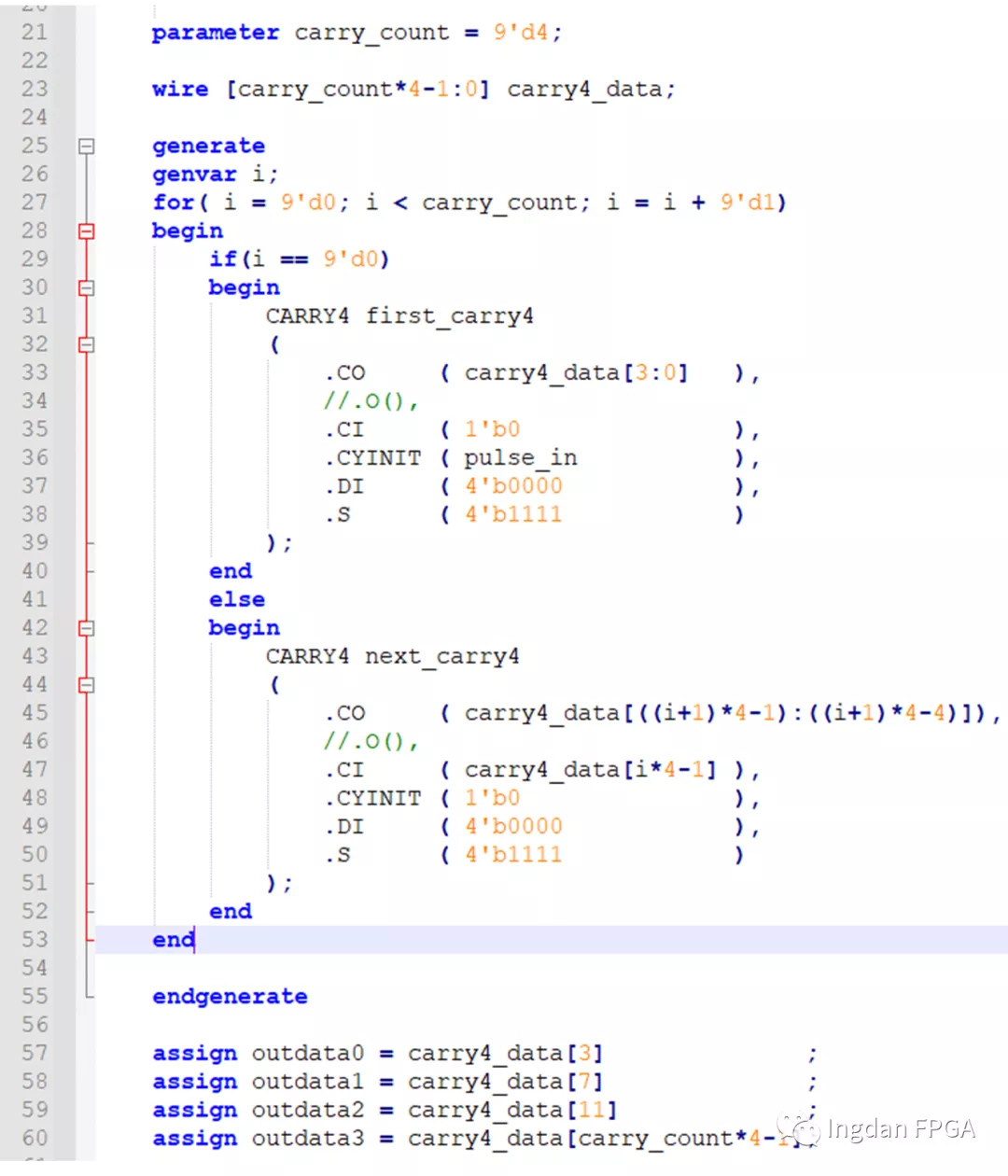

XILINX器件的进位链延时原语调用如图3所示。

carry_count代表CARRY4的级数。第一级的信号pluse_in从 CYINIT进来,从CO出去,到达下一级CARRY4的输入端CI。第一级没有前级进位,所以CI输入为0。以后每一级CARRY4的输出都作为输入到达下一级的CI端。S端输入需要一直为0,这样选择器就会选择从CIN进来的数据。任意一级的CO0/CO1/CO2/CO3都可以作为输出,输出到pin上。

每一级的CO0/CO1/CO2/CO3也可以放到寄存器中,实现对每一级的信号值的测量。

图三:CARRY4原语调用

3、进位链延时计算

根据上述代码使用CARRY4实现进位链延时后,以XC7K325T-2FBG676为例布线如图4所示。这里为方便查看,仅以4级进位链为例,实际中可以实现更长的链和延时。

图四:四级进位链布线图

信号从管脚进来以后,经过4级进位链的延时,从第四级的CO3输出到输出管脚上。其对应的时序报告如图5所示。

图五:四级进位链时序报告

如图5所示,可知整个链路的延时主要是由七部分组成:

1、输入信号的IBUF,延时为固定的0.624ns。

2、IBUF到第一级CARRY4的net延时,这个由具体pin和CARRY4的位置距离决定,尽量选择合适的管脚和CARRY4位置,使二者尽可能地近。

3、第一级CARRY4的延时,固定为0.287ns左右(取CO0-CO3会略有不同,差别不大)。

4、前一级CARRY4的输出到下一级CARRY4的net延时,这个分为三种。

a. 同一个BANK同一列的SLICE,分为上下两个部分(一个BANK同一列上下各25个SLICE),如果是同属上半部分或者同属下半部分的相邻CARRY4,其延时是0ns;

b. 如果同一个BANK分属上下两部分的2个相邻SLICE的CARRY4,其延时是7ns;

c. BANK之间的相邻的2个SLICE,其延时是1ns。

5、后级CARRY4(第一级除外)的延时,最小的延时为(级数-1)*53ps,图中这里级数=4。

6、最后一级CARRY4到OBUF的net延时,这个由具体pin和最后一级CARRY4的位置距离决定。

7、输出信号的OBUF,延时为固定的2.045ns。

由此可见,只要约束了合适的管脚和CARRY4的位置,延时的长短主要取决于CARRY4的级数,每级CARRY4都是固定的延时,从而可以实现以固定的最小延时作为步进的延时递增。

4、进位链延时约束

在设计时,需要CARRY4的位置约束,约束语句使用这样的语句。

set_property BEL CARRY4 [get_cells {genblk1[3].next_carry4}]

set_property LOC SLICE_X153Y106 [get_cells {genblk1[3].next_carry4}]

CARRY4位置约束的使用原则:

1、原则上,CARRY4的位置约束应该选择在距离pin最近的1-2列,不要距离pin太远,级数也不要太多;

2、约束文件中,只有最后一条位置约束语句是有效的,VIVADO会据此位置进行place;

3、根据最后一句的位置,前一级CARRY4会place到下边一个SLICE中(从XILINX的坐标系角度上说是按照Y减小的方向),后一级CARRY4会place到上边一个SLICE中。其余CARRY4按照此规则同列分布;

4、VIVADO会尽量把所有的级数都在同一个列的SILCE进行分配;

5、输入管脚和第一级CARRY4要尽量靠近,输出管脚也要和其最后一级CARRY4尽量离得近。

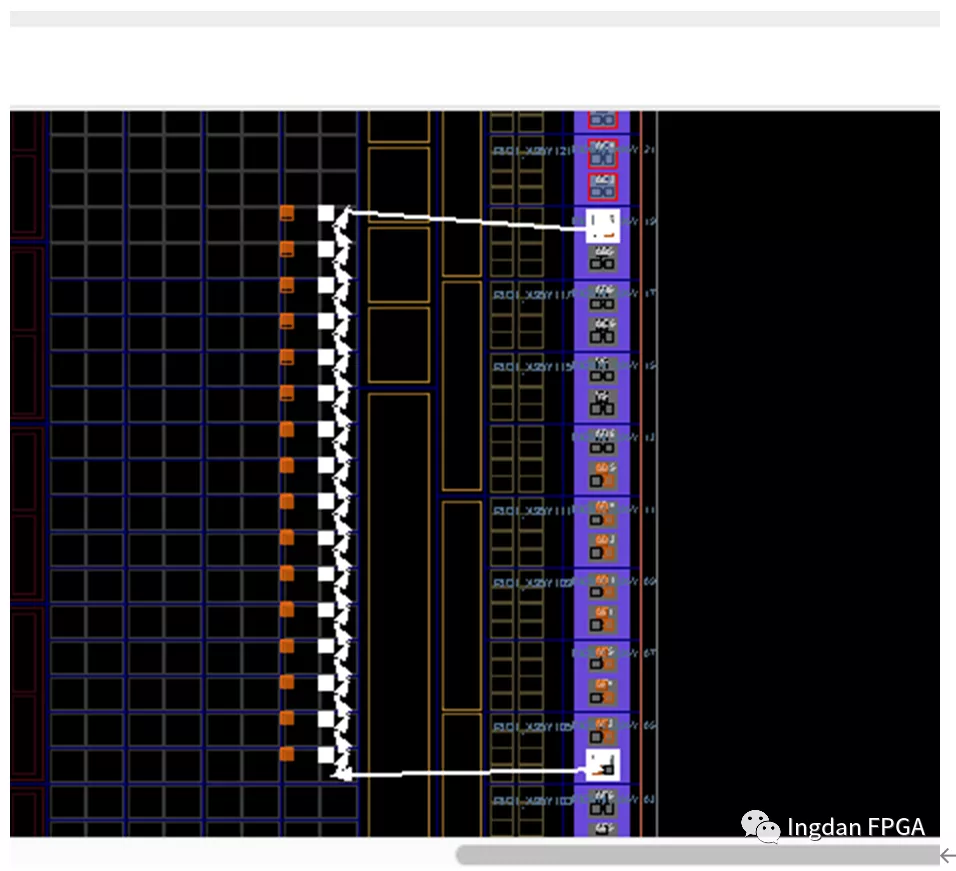

按照上述规则添加约束后,16级进位链的布线图如图6所示。

图六:16级进位链布线图

参考资料

UG474\DS182....

如果您在使用进位链来实现TDC方面有问题,欢迎联系: