摘要:该文分析了多通道宽带通信平台需求和技术特征,提出了一种基于集成射频芯片AD9371 和Zynq UltraScale+ MPSOC 的多通道宽带通信平台解决方案,详细介绍了集成射频芯片AD9371 和Zynq UltraScale+MPSOC内部组成原理,并且基于该平台进行了QPSK算法验证,结果表明该平台性能优越,满足下一代宽带通信平台需求。

引言

随着社会的发展,下一代通信设备对传输容量需求越来越大,并需要对语音、数据、图像和视频的传输和处理,因此对宽带平台的信号带宽和通道数提出了很高的要求。

现阶段的通信平台一般采用超外差和零中频两种架构实现,超外差架构存在不可在线编程、扩展性差、体积大、功耗高等缺陷[1],零中频架构一般采用最新的捷变频收发器芯片AD3961 实现,但是AD9361 带宽最高支持56MHz信号带宽,也不满足宽带通信平台的要求。

综上所述,新一代宽带通信平台必须具备具有多通道、宽频段、高动态范围、轻量化、通用化、硬件可配置、软件即插即用等技术特征。本文提出一种基于集成射频芯片AD9371 和Zynq UltraScale+MPSOC 的下一代多通道宽带通信平台设计方案,可满足新一代宽带通信设备的应用需求,在军民用无线通信领域具有广阔的应用前景。

1. 硬件架构

1.1集成射频处理芯片结构

AD9371是一款高集成度的宽带RF收发器,提供双通道的发射器和接收器、集成式频率合成器、测试和信号处理功能。AD9371提供FDD和TDD应用中的3G/4G 微基站和宏基站设备所需的灵活性能和低功耗组合。该器件的工作频率为300MHz~6000MHz,AD9371 最高支持100MHz 接收器带宽,此外还支持带宽高达250Mhz的观测接收器和发送频率合成,能够适应数字校正算法。另外还集成了ADC/DAC 转换器、射频放大器、模拟滤波器、混频器调制解调器,每个通道还独立集成了自动增益控制(AGC)、直流失调校正、正交校准和数字滤波器电路[2-3]。

AD9371是一款高度集成的宽带RF收发器,提供双通道发射器和接收器、集成式频率合成器和测试和数字信号处理功能。IC提供FDD和TDD应用中3G/4G微和宏基站设备所需的灵活高性能和低功耗组合。该器件的工作频率范围为300 MHz至6000 MHz,涵盖大部分特许执照和免执照蜂窝频段。此IC支持最高100 MHz接收器带宽。另外,它还支持带宽高达250 MHz的观测接收器和发送频率合成,能够适应数字校正算法。

该收发器由宽带直接变频信号路径组成,拥有首屈一指的噪声系数和线性度。每个完整的接收器和发射器子系统都内置直流失调校正、正交误差校正功能和可编程数字滤波器,消除了在数字基带中提供这些功能的必要性。它集成了一些辅助功能,如辅助模数转换器(ADC)、辅助数模转换器(DAC)和通用输入/输出(GPIO),可提供额外的监控和控制功能。

内置具有两个输入的观测接收器通道,可监控每个发射器输出并实施干燥降低和校准应用。该通道还连接到三个嗅探器接收器输入,可监控不同频段内的无线电活动。

高速JESD204B接口支持最高6144 Mbps的通道速率。四个通道专门用于这些发射器、此接收器以及观测接收器通道。

完全集成的锁相环(PLL)可同时针对发射器、接收器、观测接收器和时钟部分提供高性能、低功耗的小数N分频频率合成。精心设计和布局技术提供高性能基站应用中所需的隔离性能。所有集成式压控振荡器(VCO)和环路滤波器元件可最大程度地减少外部元件数量。

需要1.3 V电源向AD9371内核供电,并通过标准四线式串行端口进行控制。其它电压电源提供适当的数字接口电平,可优化发射器和辅助转换器性能。AD9371采用12 mm × 12 mm、196引脚芯片级球栅阵列封装(CSP_BGA)。

应用

内部结构框图如图1所示

图1 AD9371 内部结构图

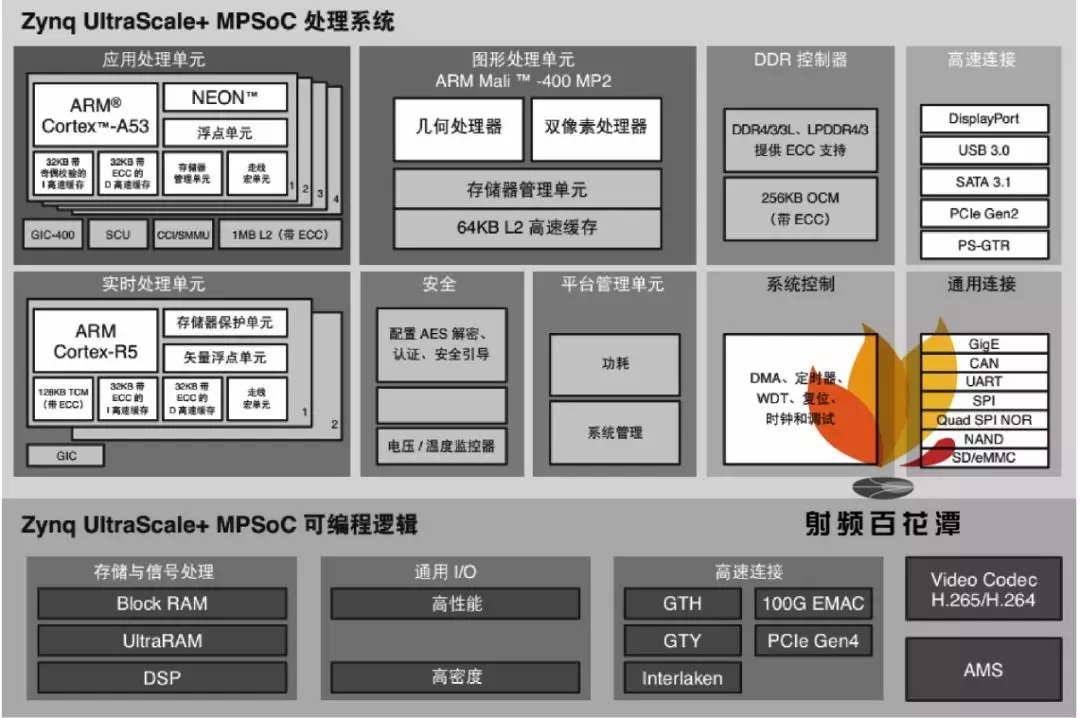

1.2. Zynq UltraScale+MP SOC芯片结构

Z ynq UltraScale+MPSOC 为Xilinx 公司推出的MPSoC芯片,本平台选择XCZU6EG 作为核心处理器。其内部包括PS(ARM)和PL(FPGA)两大部分,相互之间通过片内集成的高速AXI 总线实现高达数Gbps 吞吐率的数据交互,可满足宽带数据交互的要求。PS部分集成四核1.3GHz-A53+ 双核533MHz-R5 实时处理器,高性能的A53完全可以胜任宽带处理平台的控制、协议处理需求,高性能的R5处理器用来处理实时性要求比较高的任务[4]。PS 内部同时集成了多个千兆以太网MAC/SPI 控制器/USB ULPI 接口/I2C 控制器/UART控制器等资源,原理框图[5]如图2所示。

图2 Zynq UltraScale+MPSOC 原理框图

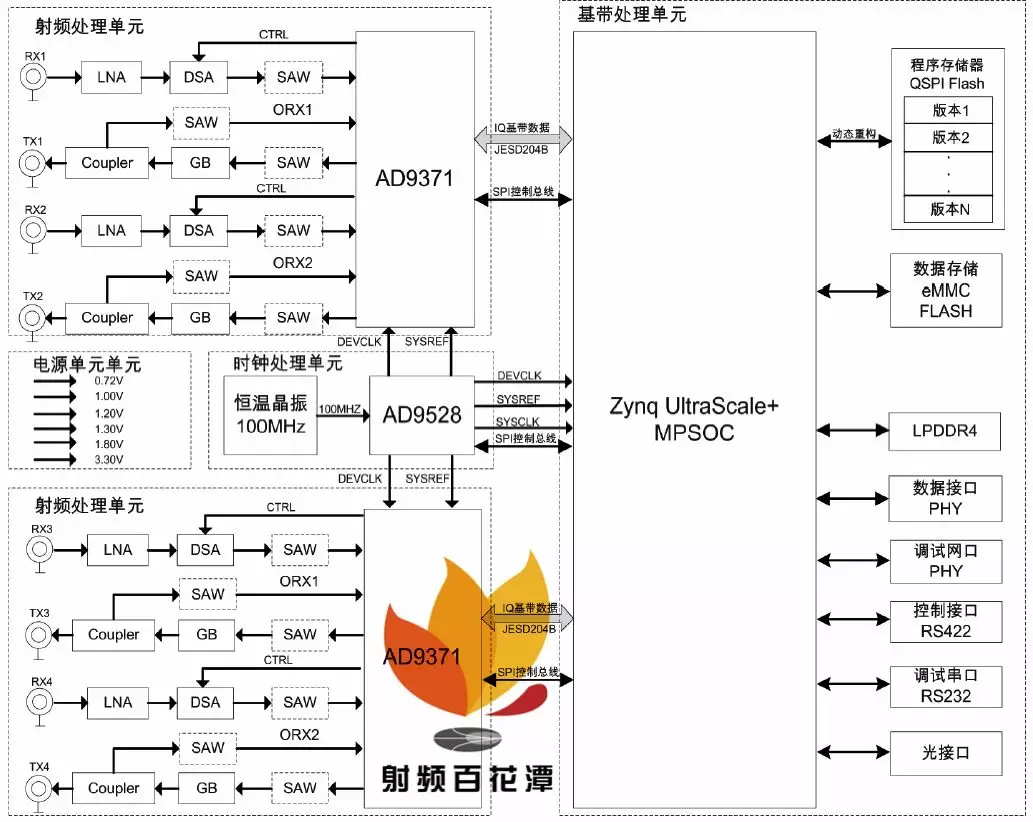

1.3. 基于集成射频芯片和ZynqUltraScale+MPSOC的多通道宽带通信平台硬件架构

为了满足新一代多通道宽带通信平台的宽频段、高动态范围、轻量化、通用化、硬件可配置、软件即插即用等技术特征,结合AD9371 的宽频段、可配置带宽和ZynqUltraScale+MPSOC的低功耗、小型化和高性能的优势,设计了一种新型的多通道宽带通信平台。该平台以集成射频芯片AD9371和ZynqUltraScale+MPSOC为核心,由四个硬件电路单元组成,其系统框图如图3所示:

(1)电源处理单元,主要将外部电压转换为系统正常工作所需的电压,如:0.72V,1.2V,1.3V,1.8V,3.3V[6]等;

(2)射频处理单元,主要由两片AD9371芯片和射频模拟电路组成,完成四通道接收和四通道发射的射频信号处理,射频电路完成信号的放大、滤波等处理,AD9371在接收端将信号进行放大、混频、滤波及A/D转换等处理,将射频信号转换为数字基带信号;在发送端,将数字基带信号进行数字滤波、D/A转换、模拟滤波、混频、放大转换为射频信号[1];

(3) 数字基带处理单元,主要由Zynq UltraScale+MPSOC芯片、LPDDR4芯片、QSPIFLASH、eMMCFLASH和其他接口芯片组成,完成数字基带信号的调制解调算法,对外接口控制、数据存储等工作;

(4)时钟处理单元,主要由时钟芯片AD9528和恒温晶振组成,提供系统工作所需要的时钟频率,并产生同步控制信号,保证两片AD9371和MPSOC工作在同步模式下。此外,时钟处理单元还支持远端光纤时钟恢复,便于通信系统的近远端同步。

图3 宽带通信硬件平台框图

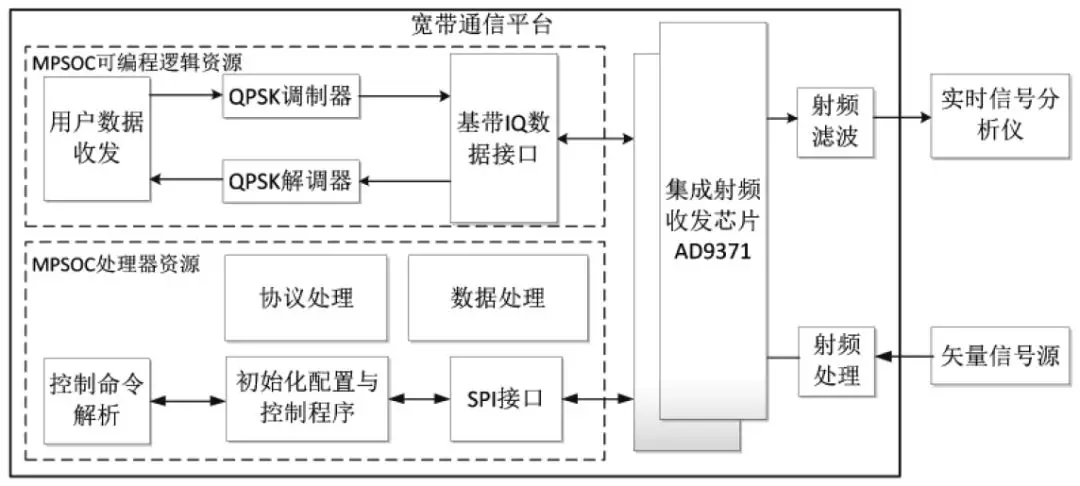

2 算法验证

基于多通道宽带通信平台进行了QPSK算法测试验证,验证原理框图如图4所示。

图4 测试验证原理框图

基带MPSOC的PL部分完成用户数据收发、QPSK调制解调、与集成射频收发芯片之间的基带IQ数据接口,基带MPSOC的PS部分完成控制命令解析、集成射频收发芯片初始化配置与参数控制、SPI 接口实现。集成射频收发芯片主要完成基带数据FIR 滤波、ADC/DAC 变换、模拟基带滤波、上下变频、射频本振、射频放大。

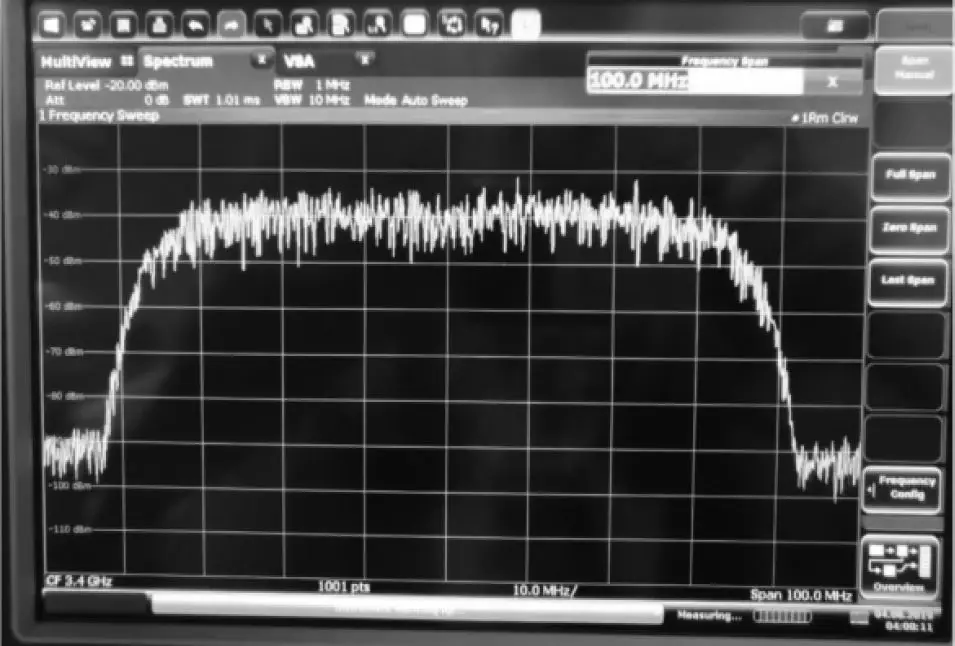

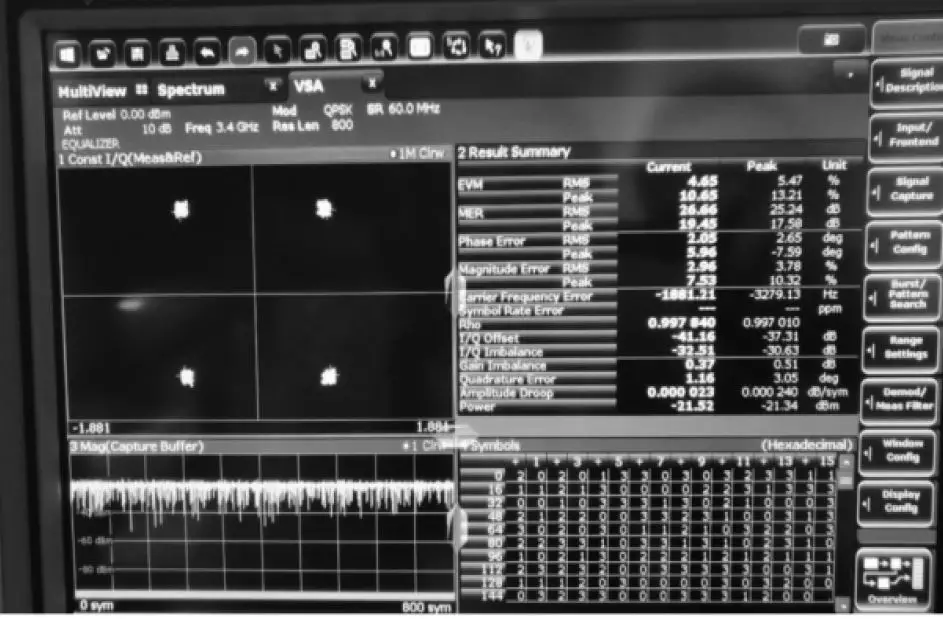

基带MPSOC 中设置QPSK 基带符号速率为60Mbps,成型系数0.35,设置集成射频收发芯片中频频率为3.4GHz,信号带宽为81MHz,通过实时信号分析仪测试发射信号质量,矢量调制误差(EVM)均4.65%,杂散50dBc,性能较好,发射频谱和星座图如图5、图6所示。

图5 发射频谱

图6 星座图

接收测试采用矢量信号源产生,设置基带符号速率为60Mbps,成型系数0.35,经实测解调门限7dB,与理论计算结果吻合。

3. 结论

本文详细介绍了基于集成射频芯片AD9371 和Zynq UltraScale+MPSOC 的多通道宽带通信平台的原理和设计实现,通过加载QPSK算法对平台的性能进行了测试验证,验证结果表明该平台性能优越,具备可编程、可重构、射频数字化等技术特征,在宽带通信领域具备良好的应用前景,具有较好的推广应用价值。

免责声明:本文为网络转载文章,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。