本文转载自: FPGA技术联盟微信公众号

大多数使用Xilinx FPGA的设计者都使用图形用户界面(Graphical User Interface)模式下的ISE项目浏览器和PlanAhead软件。GUI为小项目提供了一个按钮式的流程。

然而,随着FPGA规模越来越大,设计也会越来越复杂,设计团队也变得庞大。在很多情况下,GUI工具阻碍了团队的工作效率,没有对编译过程提供足够的灵活性喝控制,同时也不允许与其他工具简单集成。一种流行的编译管理和持续集成解决方案是TeamCity、Hudson CI和CruiseControl,许多设计团队使用它们进行自动软件构建。

GUI工具也不能为分布式计算环境提供良好支持。编译一个大型FPGA设计需要花费几个小时甚至一天。为改善运行时间,用户在专用服务器上进行设计,典型的有大内存64位多核Linux服务器。但在大多数情况下,还是需要使用GUI。也有第三方工作调度解决方案,如平台LSF提供灵活的编译调度、负载均衡和细粒度(fine-grained)控制。

没有使用GUI工具的一个不起眼原因是内存和CPU资源的利用。ISE 项目浏览器(ISEProject Navigator) 和PlanAhead需要大量占用内存的应用程序。例如,每个工具使用超过100 MB的RAM,而典型工作站有2 GB内存,这意味着占用率超过5%。如果能节省内存用于他用,将会更有利于设计。

最后,许多具有ASIC设计背景的Xllinx用户转向使用FPGA。这些工程师习惯于使用命令行模式下的工具流程,并希望在FPGA设计中继续使用类似的流程。这些都是设计者为什么要切换到命令行模式下进行任务设计的原因。

脚本语言选择

Xilinx的命令行工具可同时运行在Windows和Linux操作系统上,使用如下列清单所示的多种脚本语言。除此之外,运行Xilinx工具的脚本语言还有Ruby和Python。

Perl

Perl是一种流行的脚本语言,广泛应用于EDA等工具中。Xilinx ISE安装中包含了一个定制的Perl分布系统。用户通过运行xilperl命令来输入Perl语言:

$ xilperl -V # display Perl version

TCL

工具命令语言(TCL)是面向ASIC和FPCA设计工具的一种近乎标准的脚本语言。TCL语法不同于其他脚本语言,许多开发者很难习惯。这可能是TCL不如Perl流行的原因之一。

顾名思义,TCL可以很好地运用于书写工具命令脚本。这种语言用途广泛,具有良好的文档和团队支持。Xlim ISE的安装中附带了一个自定义的TCL 分布。若要启动TCL可以使用xtclsh命令:

$ xtclsh -V # display TCL version

UNIX bash和csh

有多种Linux和UNIX界面,其中最流行的是bash和csh。与其他UNIX/ Linux界面不同的是,csh拥有一个类似C的脚本语言。然而,bash脚本语言还提供了更多的功能,如shell函数、命令行编辑、信号捕捉和过程处理( process handling)。bash 是Linux发布的最新版的默认界面,正在逐步取代csh。

Windows批处理和PowerShell

Windows用户有两种脚本语言可以选择: DOS命令行和更灵活的PowerShell。XST从DOS命令行调用的一个例子是:

>xst -intstyle ise -ifn "crc.xst" -ofn "crc.syt"

编译流程

Xilinx 提供了使用命令行工具编译设计的选项,其中4个维度行分别是直接调用、xflow、xiclsh和PlanAhead。

直接调用方法按照下列顺序调用工具: XST(或其他综合工具)。NCDBUILD( 转换),MAP(映射)、PAR(布局布线)、TRCE( 静态时序分析)(可选)和BITCEN(比特流生成)。设计者可以从ISE项目浏览器中自动生成上面序列的脚本语言。

下面的脚本语言是直接调用编译的一个例子。

xst -intstyle ise -ifn "/proj/crc.xst" -ofn "/proj/crc. syr"

ngdbuild -intstyle ise -dd ngo -nt timestamp -uc

/ucf/crc.ucf -p xc6slx9-csg225-3 crc.ngc crc.ngd

map - intstyle ise -P xc6slx9-csg225-3 -W -01 high -t 1 -xt 0

-global_ opt off -lc off -0 crc_ map.ncd crc.ngd crc.pcf

par -W - intstyle ise -ol high crC_ map.ncd crc.ncd crc.pcf

par -W - intstyle ise -ol high crC_ map.ncd crc.ncd crc.pcf

trce -intstyle ise -V 3- S 3 -n 3 - fastpaths -Xm1 crc. twx

crc.ncd -0 crC. twr crc.pcf

bitgen - intstyle ise -f crc.ut crC. Ncd

使用xflow

Xilinx xflow实用程序提供了另一种编译设计的方式。相比直接调用,这种方式更容易使用,不需要太多的工具知识。例如,xflow不需要退出代码来检查条件是否通过/失败。

xflow实用程序可接受描述编译选项的脚本语言。根据这些选项,xflow 可以运行综合、实现、比特流生成,或是三者的结合。

仅综合:

xflow -p xc6s1x9-csg225-3 -synth synth.opt, ./src/crc. V

实现:

xflow -p xc6s1x9-csg225-3 -implement impl.opt../crc.ngc

实现和比特流生成:

xflow -p xc6s1x9-csg225-3 implement impl.opt -config

bitgen.opt .. /crc.ngc

设计者可手动或通过以下位置ISE安装的模板来生成xflow脚本: SXILINXIISE_ DSIISE\xilinx \data\。Xilinx ISE软件不提供自动生成xflow脚本的选项(见图1)。

使用xtclsh

此外,可以使用从Xilinx xtclsh调用的TCL脚本对设计进行编译,例如:xtclsh crc.tcl rebuild project

TCL脚本可以手动编写,然后作为参数传递给xtclsh,也可以由ISE项目浏览器自动产生。

xtclsh是唯一按 照输人方式接收. xise格式的初始ISE项目的编译流程。所有其他流程(如. xst和. prj)都需要项目和文件列表,这些文件从原始的. xise项目中导出。

每一个XST、NGDBUILD、MAP、PAR、TRCE和BITCEN工具选项都有其TCL的等效属性。例如,“Add V0 Bure'的等效XST命令行为-iobur, -fsm syle 是“FSM Syle"(列表)的等效命令行。

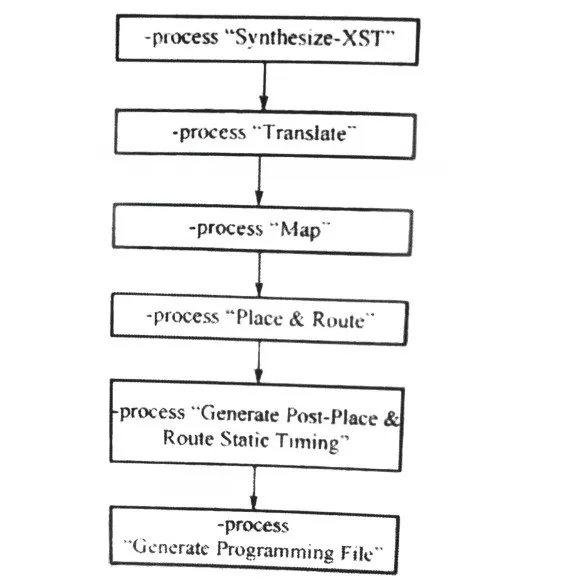

使用CL的"prces um命令调用每个工具,如图2所示。

使用PlanAhead

随着Xilinx用户的日益增多,ISE项目浏览器和PlanAhead也已成为主要的设计工具。PlanAhead提供了更多与编译相关的功能。例如它可以调度多个并发编译,提供更灵活的编译选项和项目操作。

PlanAhead使用TCL作为其主要的脚本语言。

PlanAhead有两种命令行模式:交互式界面和批处理模式。进人交互式界面后,键人以下命令:

PlanAhead -mode tcl

整个TCL脚本运行在批处理模式下,源脚本如下所示:

PlanAhead -mode tcl source

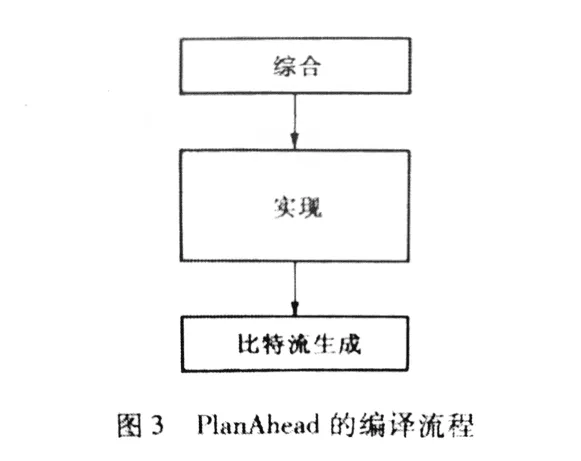

PlanAhead的编译流程(或运行)包括三个步骤:综合、实现和比特流生成,如图3所示:

PlanAhead软件维护其在PlanAhead. jou 文件中的操作日志。该文件是TCL格式,位于Windows操作系统的C:\Dcuments and Sttings \< user name > \Application Data\HDI\目录和Linux操作系统的/. HDI/目录下。

用户可以先在GUI模式下运行编译,然后在命令行复制日志命令来生成脚本。下面是PlanAhead TCL脚本的举例:

create project pa_ proj {CrC_ example/pa _proj}" -part

xc6slx9csg225- 3

set_ property design mode RTL [get_ property srcset

[current run] ]

add_ files -norecurse {crC_ example/proj/ . . /src/crc.v

set_ property library work [get_ files -of objects

[get_ property srcset [current_ run] ] { src/crc.v} ]

add files -fileset [get_ property constrset [current run] ]-

norecurse {ucf/crc.ucf }

set_ property top crc [get property srcset [current run] ]

set_ property verilog_ 2001 true [get_ property srcset

[current run] ]

launch_ runs -runs synth 1 -jobs 1 -scripts_ only -dir

{crc_ example/pa_ proj/pa_ proj. runs}

launch_ runs -runs synth_ 1 -jobs 1

launch_ runs -runs impl 1 - jobs 1

set_ property add_ step Bitgen lget_ runs impl_ 1]

launch_ runs -runs imp1_ 1 -jobs 1 -dir

icrc_ example/pa proj/pa proj,runs}

除了提供标准的TCL脚本功能,PlanAhead 还提供了其他强大功能。它允许从所有的TCL脚本中对设计数据库、设置和状态进行查询与操作。下面这 个简单的脚本用于说明PlanAhead的一些高级功能,它们可以在命令行模式下使用:

set my_ port [get_ portsrst ]

report property $my_ port

get_ property PULLUP $my_ port

set property PULLUP 1 $my port

get_ property PULLUP $my port

上面的简单脚本语言是为设计端口添加上拉电阻。通过改变UCF约束、重新编译项目或使用FPGA编辑器,也可以完成相同的操作。但PlanAhead只用3行代码就能做到。

许多开发者喜欢使用make工具进行FPGA编译。make 有两个最重要的优势,分别是内置的返回代码和自动跟踪检查。以上所述流程都可以使用make工具。

本节已经讨论了在命令行模式下使用Xilinx工具的优势,探讨了几个Xilinx 编译流程,并研究了不同的脚本语言。目的不是找出最佳的编译流程或一种脚本语言, 而是要探讨每个可用的选项及其独特优势和缺点,从而帮助Xilinx FPGA设计者做出明智的选择。

Xilinx FPGA设计者可以将选择过程基于一些标准,如现有的项目设置、设计团队的经验、熟悉的工具和脚本、易于使用性、灵活性、定制的预期水平,以及与其他工具的定制和集成。