本文转载自: XILINX开发者社区

本文作者:赛灵思工程师 Longley Zhang

在Zynq MPSoC里,我们有以下文章介绍怎么在MPSoC实现cache一致性的传输:

[1]https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842098/Zynq+Ultr...

[2]https://support.xilinx.com/s/article/69446?language=en_US

Versal与MPSoC在cache维护数据的架构上,有一定的相似性。所以在Versal器件里,我们仍然可以使用上述文档 [1] 里8.1和8.2的checklist去检测系统是否满足一致性传输的条件。

本篇博客提供了一个基于VCK190 ES1开发板和2021.1 Vivado/Vitis的例子,用来简单介绍在Versal里实现数据从PL 经过 FPD CCI 到达 NoC DDR的一致性传输。

这个例子与上面文档 [2] 的例子类似,使用AXI CDMA IP实现数据的传输,通过修改AXI CDMA在Vitis里的参考设计,实现CPU直接读写AXI CDMA传输过来的数据,不必进行额外的cache操作。

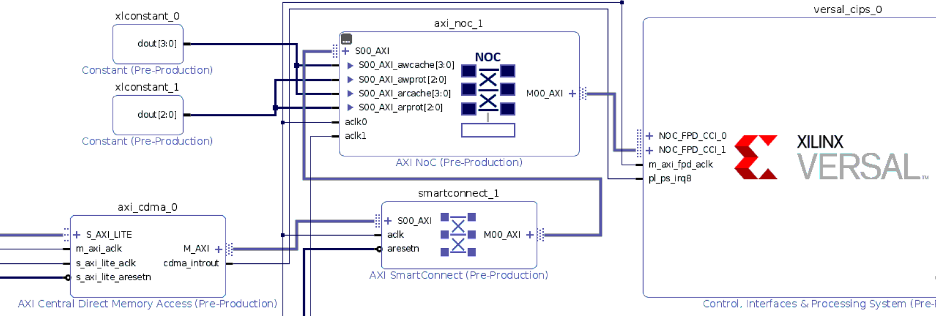

这个例子里,AXI CDMA通过NOC连接到CIPS IP的NOC_FFD_CCI_1接口,这个接口是连接到PS内部的cache管理模块CCI-500,下面是这个例子的Block Design截图。更具体的block design,请新建一个VCK190 ES1的工程,然后运行附件的tcl文件创建完整的block design。

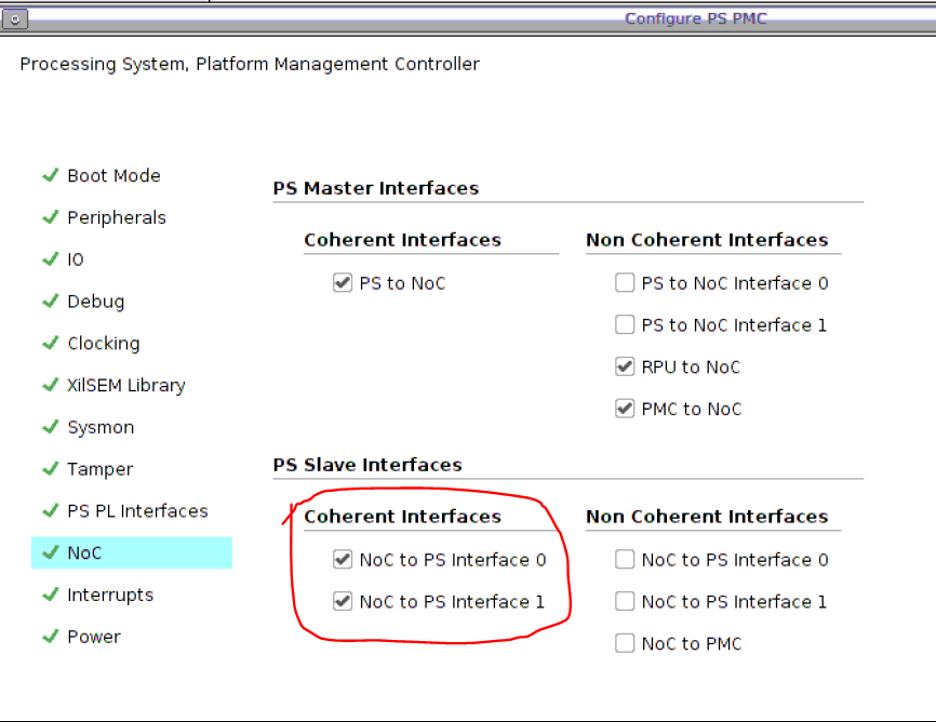

可以通过双击CIPS IP,选择PS PMC,使能连接NoC的CCI接口。(另外,还可以使用PS与PL的ACP或ACE接口,这两个接口也能实现数据的一致性传输。)

NoC的AXI Slave接口需要配置如下AxCache和AxProt的值,具体原因请参考文档 [2]。

AxCache: 0xF

AxProt: 0x0

在Block Design创建后,由于工具的已知问题(https://support.xilinx.com/s/article/76566),需要在tcl里运行下面命令,否则AXI CDMA会访问不到NoC DDR。运行完以下命令后,再重新分配地址。

set_property CONFIG.CONNECTIONS [list FPD_CCI_NOC_1] [get_bd_intf_pins /versal_cips_0/NOC_FPD_CCI_1]

最后把工程导出到Vitis,新建一个基于A72_0的应用工程。把(1)附件的xaxicdma_example_simple_poll.c导入到新的工程里,编译出elf。

(2)附件的xaxicdma_example_simple_poll.c是基于AXI Cdma IP自带的例子修改而来的。里面主要做了两处修改,一是使能了CCI模块S4接口的snooping,二是把例子里对cache的操作去掉。

下面是使能snooping的代码:

Xil_Out32(0XFD005000,0x1);

dmb();

最后可以运行下面的bootgen命令,通过(3)附件的bif文件把pdi和elf文件打包成boot.bin, 然后拷贝到VCK190的SD卡上运行。

[以上123附件可在公众号内回复“123附件”下载]

bootgen -arch versal -image long.bif -w -o boot.bin

下面是正常的输出:

[4.021]PLM Initialization Time

[4.083]***********Boot PDI Load: Started***********

[4.161]Loading PDI from SD1_LS

[4.223]Monolithic/Master Device

[307.009]302.813 ms: PDI initialization time

[307.087]+++Loading Image#: 0x1, Name: lpd, Id: 0x04210002

[307.175]---Loading Partition#: 0x1, Id: 0xC

[332.064]****************************************

[336.419]Xilinx Versal Platform Loader and Manager

[340.945]Release 2021.1 Feb 11 2022 - 09:36:03

[345.384]Platform Version: v1.0 PMC: v1.0, PS: v1.0

[349.908]BOOTMODE: 0xE, MULTIBOOT: 0xF0000000

[353.921]****************************************

[358.315] 51.029 ms for Partition#: 0x1, Size: 2336 Bytes

[363.312]---Loading Partition#: 0x2, Id: 0xB

[367.799] 0.527 ms for Partition#: 0x2, Size: 48 Bytes

[372.021]---Loading Partition#: 0x3, Id: 0xB

[379.571] 3.587 ms for Partition#: 0x3, Size: 60592 Bytes

[381.822]---Loading Partition#: 0x4, Id: 0xB

[387.173] 1.387 ms for Partition#: 0x4, Size: 5968 Bytes

[390.705]---Loading Partition#: 0x5, Id: 0xB

[395.390] 0.721 ms for Partition#: 0x5, Size: 80 Bytes

[399.482]+++Loading Image#: 0x2, Name: pl_cfi, Id: 0x18700000

[404.800]---Loading Partition#: 0x6, Id: 0x3

[11801.051] 11392.281 ms for Partition#: 0x6, Size: 863984 Bytes

[11803.906]---Loading Partition#: 0x7, Id: 0x5

[11872.509] 64.470 ms for Partition#: 0x7, Size: 467600 Bytes

[11875.153]+++Loading Image#: 0x3, Name: fpd, Id: 0x0420C003

[11880.401]---Loading Partition#: 0x8, Id: 0x8

[11885.475] 0.942 ms for Partition#: 0x8, Size: 1104 Bytes

[11889.911]+++Loading Image#: 0x4, Name: apu_ss, Id: 0x1C000000

[11895.178]---Loading Partition#: 0x9, Id: 0x0

[11908.765] 9.453 ms for Partition#: 0x9, Size: 176208 Bytes

[11911.365]***********Boot PDI Load: Done***********

[11915.925]194.206 ms: ROM Time

[11918.708]Total PLM Boot Time

--- Entering main() ----

Successfully ran AxiCdma_SimplePoll Example

--- Exiting main() ---

这篇博客只是着重介绍了在Versal工程里实现cache一致性传输的一些要点。如果在创建工程或运行方面遇到进一步问题,建议到赛灵思中文技术支持社区咨询。