本文转载自: 明德扬FPGA科教微信公众号

进行工程的功能调试时,对AD9144,AD9516进行参数配置是非常重要且必不可少的,这过程中遇到了以下问题。

一、问题1

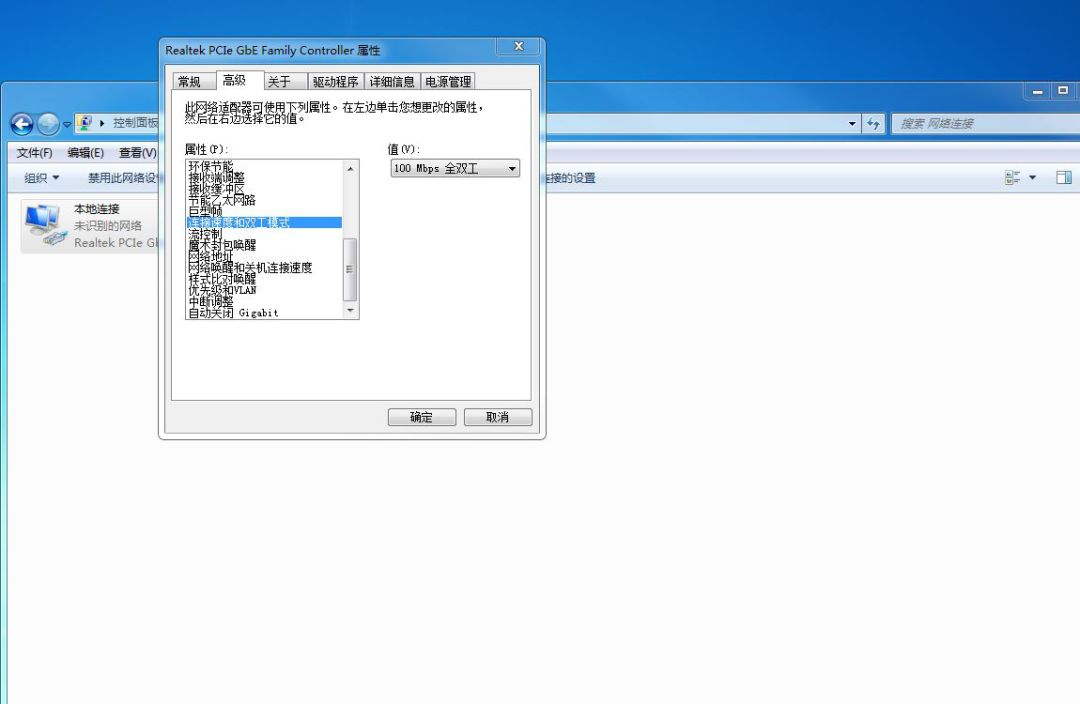

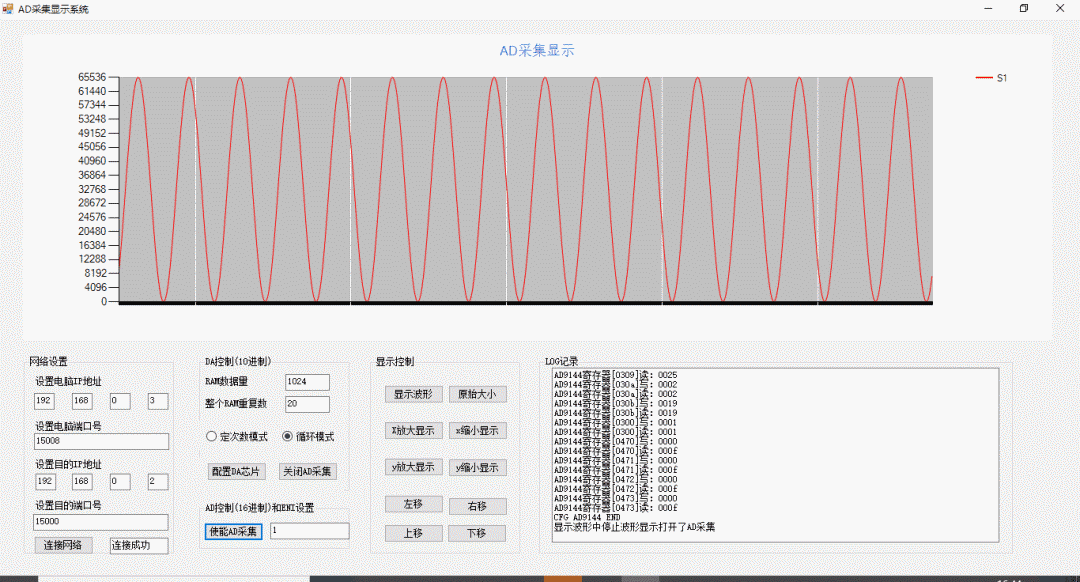

在我们使用上位机软件进行配置时发现上位机的log记录中有写入参数而无读出参数,这个问题有两种可能性,一是参数没有写入进去所以读出来的参数都是0,二是写进去了但是在读参数时出错了。

如图所示:

对此我们怀疑是否是网路通信有问题,检查发现PC与FPGA连接的网口千兆网指灯没有亮百兆网却亮了。

检查网络配置发现网络的连接速度只有百兆网选项,无法使用千兆网传输,也就是电脑不支持千兆网络。

解决方法有两种:一是重新更换电脑主机,二是重新更改程序将其设置为百兆网传输。

此次我们选择方法一,更换PC主机后重新测试发现AD9144,AD9516配置可以正常读写,故此次问题原因是PC与FPGA网络接口不匹配所致。

二、问题2

在进行AD9144,AD9516寄存器配置后,下载bit流文件到FPGA后,用示波器观察AD9144输出信号,发现无波形输出,用Vivado抓取信号观察,发现sync和tx_tready信号始终为低没有拉高,也就是说明AD9144与jesd204b没有同步上。

同步不上的原因有多种,大致可分为硬件问题、时钟关系问题、寄存器配置问题,先暂将硬件问题排除。

对时钟关系进行分析,发现时钟理论数值计算结果没有错误,详细的分析步骤请自行查看《时钟关系说明》。

依据时钟关系理论值检查JESD204B的IP核设置,未发现错误。

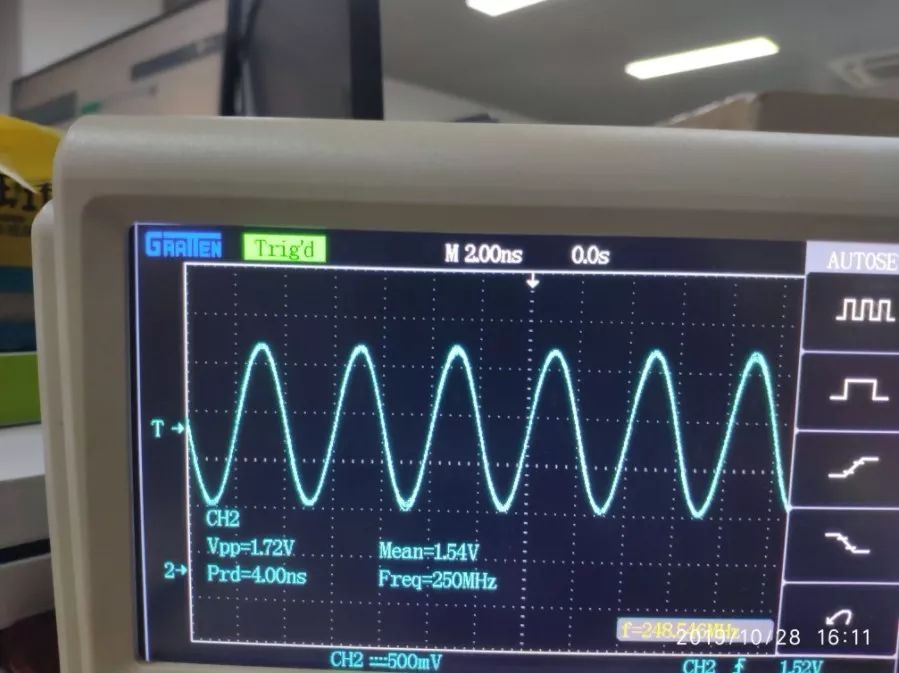

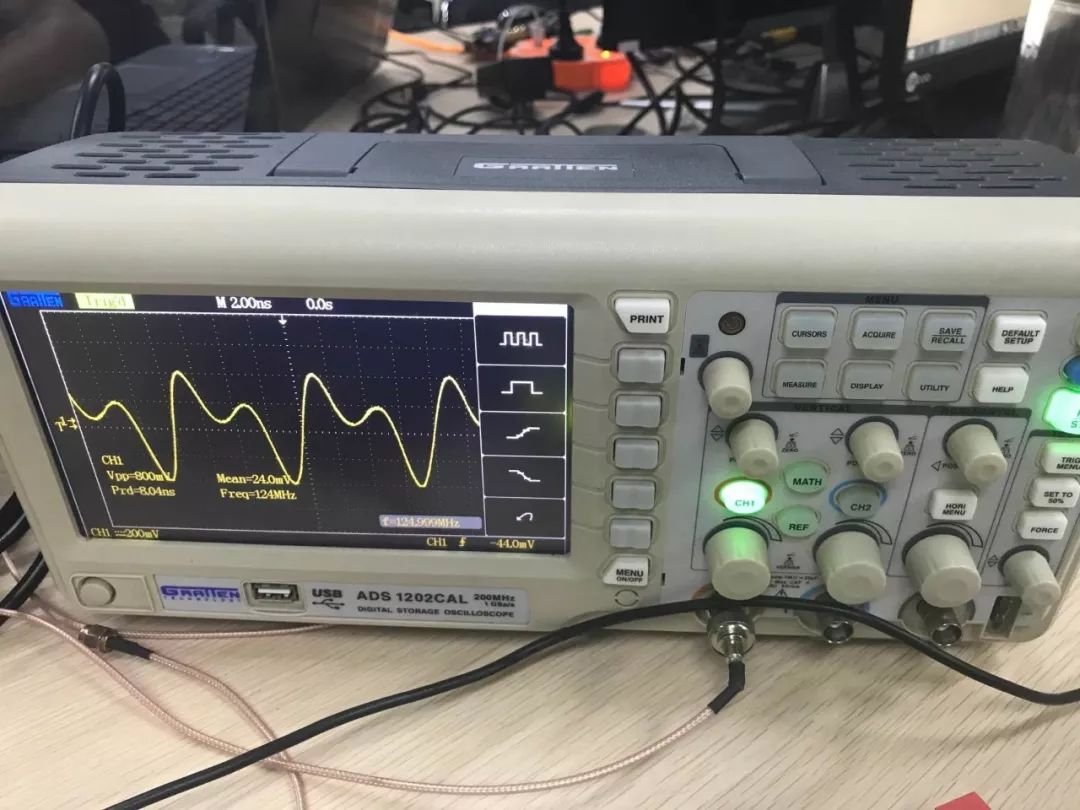

用示波器检查FPGA输送给AD9516的分频时钟发现无法侦测到,检查原理图后定位到对应的引脚,发现FPGA输送过来的时钟过大超频了,使得示波器也无法侦测到信号,通过查找AD9516的操作手册发现其用来分频的源时钟最大值为250MHZ,后将AD9516源时钟设置为250MHZ,用示波器也能正常测试到。

250MHZ时钟源:

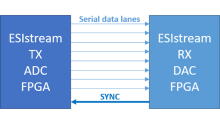

对程序内的时钟进行分析发现数据产生模块的使用的时钟为62.5MHZ,而用来驱动JESD204B模块的时钟为device_clock=125MHZ,因为数据产生和数据传递是同步,所以时钟不匹配,将62.5MHZ改为125MHZ。

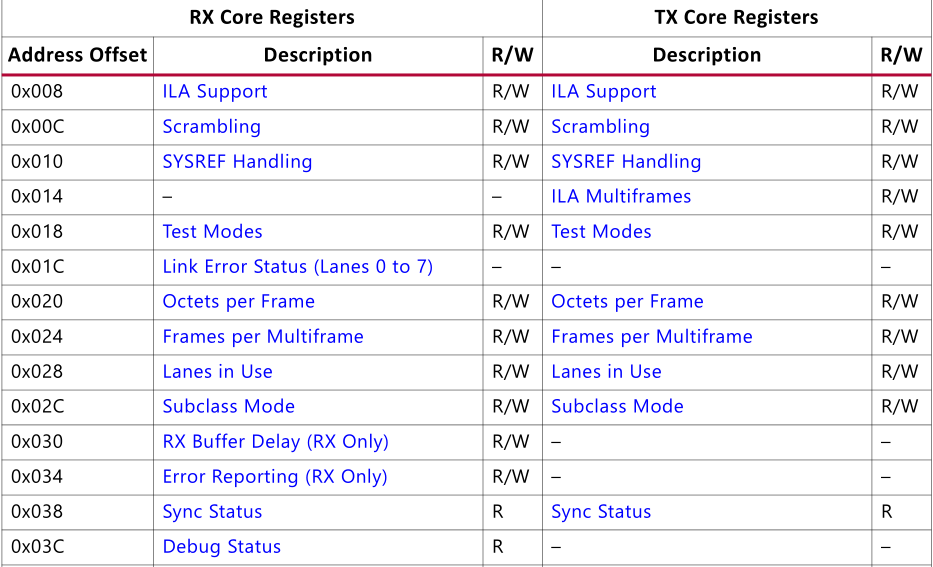

对照JESD204B的IP核手册提供的寄存器配置数据,未发现有错误。

JESD204B的IP核参数:

查看AD9144寄存器配置手册,找到AD9144同步信号指示0X470,0X471,0X472,0X473

其分别代表代码组同步信号既同步K码,帧同步信号校验核检查标志,初始通道同步信号。

然后再次通过上位机配置观察配置过程发现其他寄存器值都可以正常读写,而这4个寄存器读出值为0,也就是说明硬件无问题,极有可能是寄存器配置方面出错了。

同步指示寄存器:

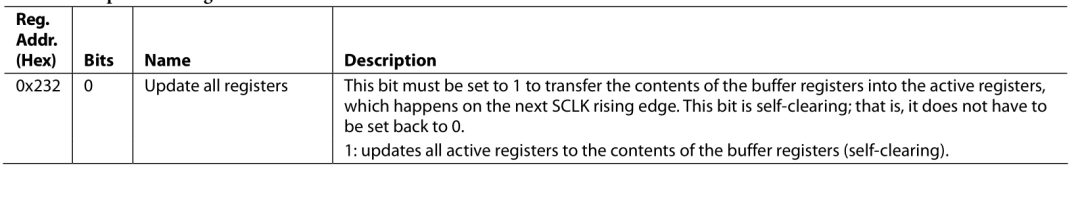

查阅AD9144,AD9516手册发现AD9516的寄存器0X232的写入值应该为1,但是AD9516的配置软件给出的参考值为0,因而更改寄存器值后能够成功配置。

寄存器配置:

成功配置后如下图所示:

三、问题3

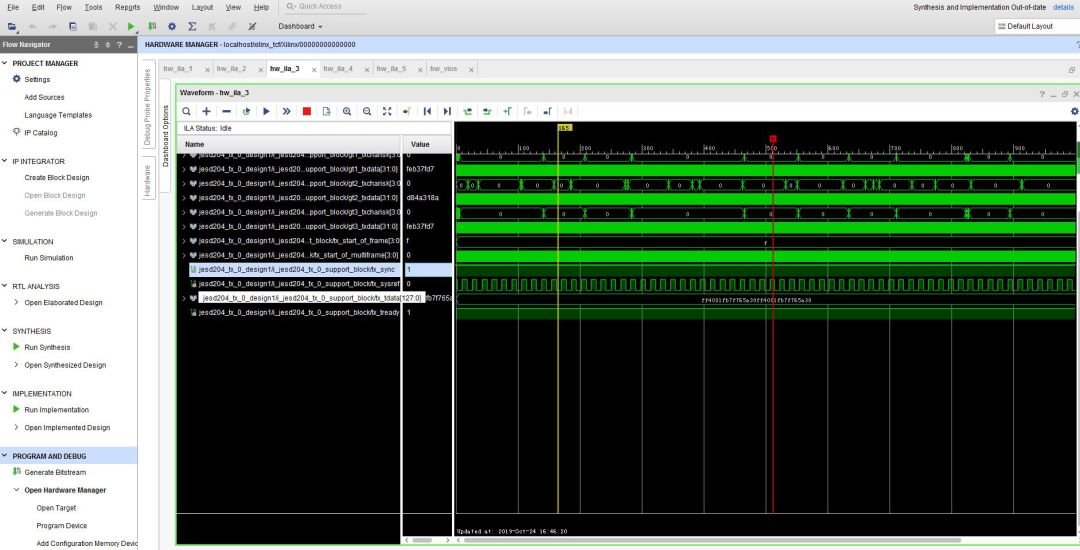

解决配置问题后,进行测试用vivado的观测sync,tx_tready信号发现信号已经拉高,并且tx_data有数值,说明AD9144与JESD204B已经完成同步了。

同步完成后的信号:

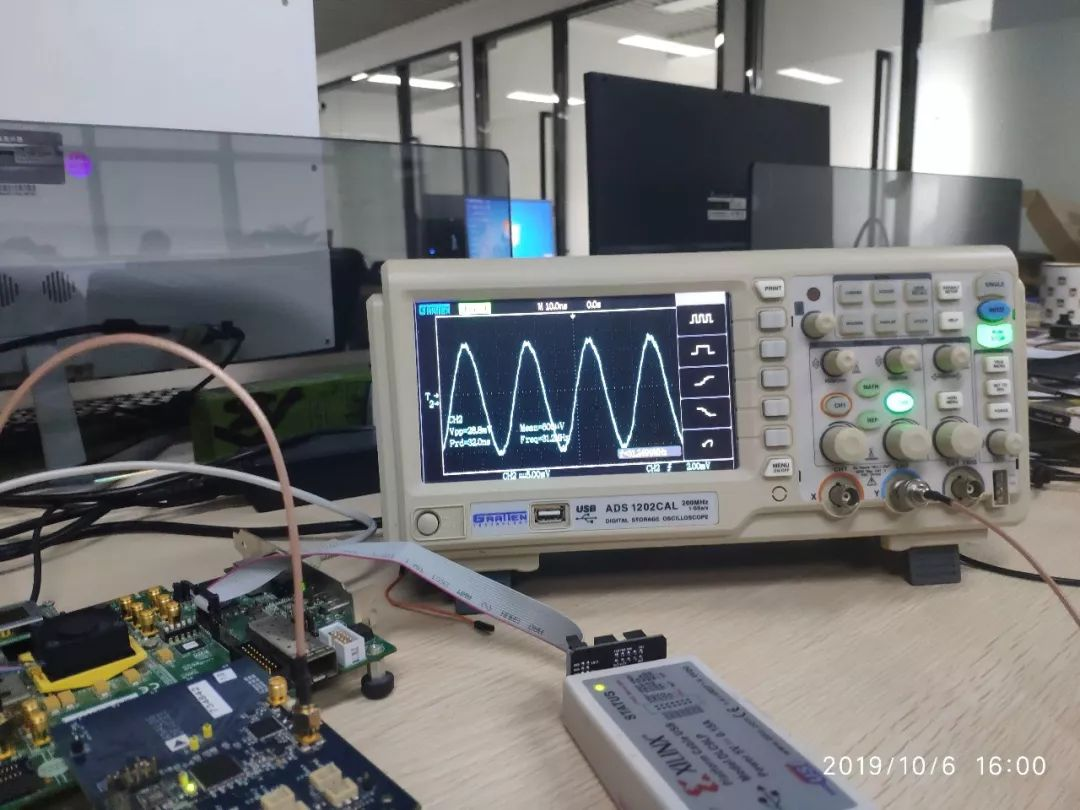

但是在用示波器观察AD9144的模拟波形时发现波形与预期的有偏差,查阅AD9144和JESD204B的手顺并结合vivado的vio功能来在线调试数据,发现其数模转换的方式是以16进制的补码相对应,后重新调整数据后,输出波形与预期一致,完成调试。

异常波形(125MHZ):

正常波形(31.25MHZ):

以上就是调试过程中遇到的问题,这里总结出来与大家分享,欢迎在评论中互相讨论。