在之前的《芯片巨头,争艳Hotchips》以及《全球最大的芯片怎么玩?Hotchips精彩继续》文章里,我们介绍了Hotchips上的一些芯片。在这篇文章里,我们将继续带来Hotchips上的AMD关于全球最大的FPGA分享。

在 Hot Chips 2023 上,我们获得了有关 AMD Versal Premium VP1902 FPGA 的更多信息。我们之前在文章《世界上最大的FPGA发布》中说到,这是一个巨大的芯片,专为制作更大芯片的原型而设计。

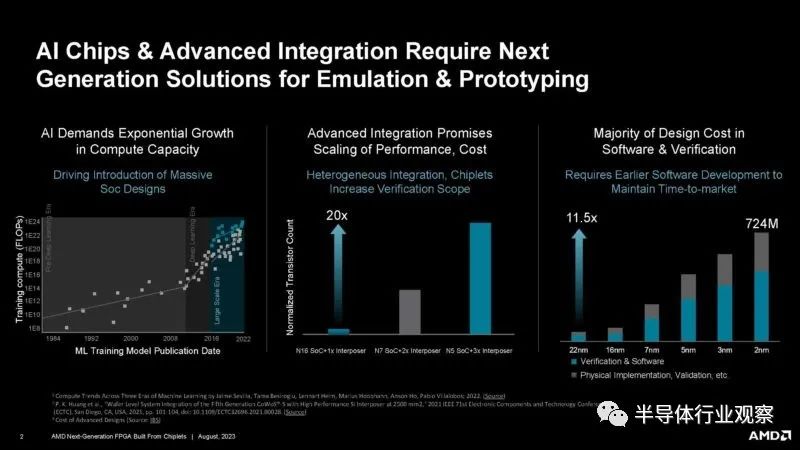

由于 2023 年一切都是人工智能,甚至构建 CPU、GPU 和人工智能加速器的工具现在也有了人工智能。

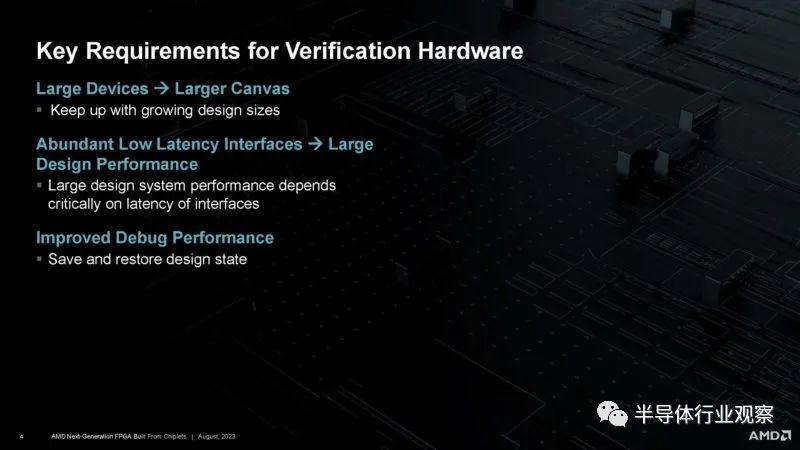

VP1902 的设计目的不是作为单个设备使用,而是更多地以集群方式使用,以帮助驱动芯片级验证和测试。

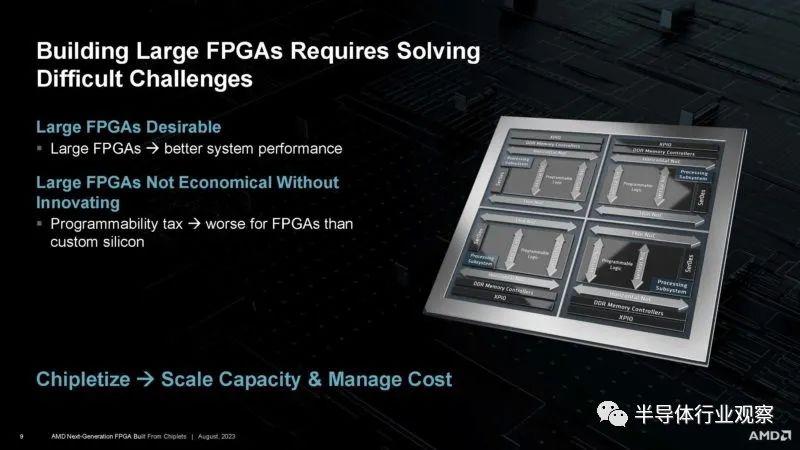

在这里,大就是好的,因为 FPGA 的密度不如它们原型设计的芯片。更大的芯片意味着更少的 FPGA 来容纳更大设计的所有逻辑,或者只是能够将更大的设计放入这些 FPGA 集群中。

从下图,我们可以看到这系列FPGA的演变。

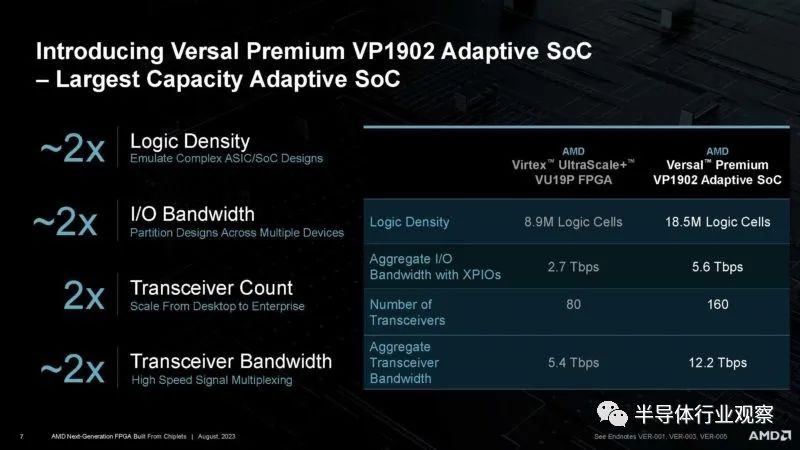

这是一款 AMD Versal Premium VP1902 自适应 SoC,设计规模庞大。

使用 2×2 小芯片排列以及各代增强功能,VP1902 的性能大约是上一代产品的两倍。

我们在上一篇文章中介绍了 VP1902,但这里有一张很好的幻灯片,介绍了该芯片的一些亮点。

AMD 现在正在讨论扩大设计规模和使用小芯片。

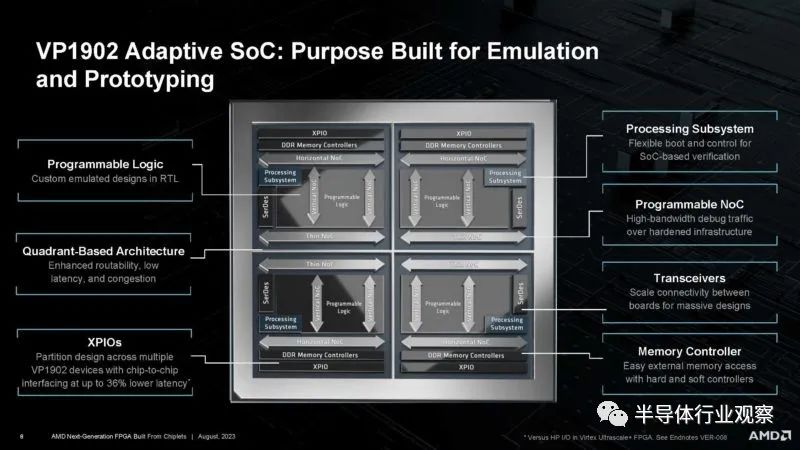

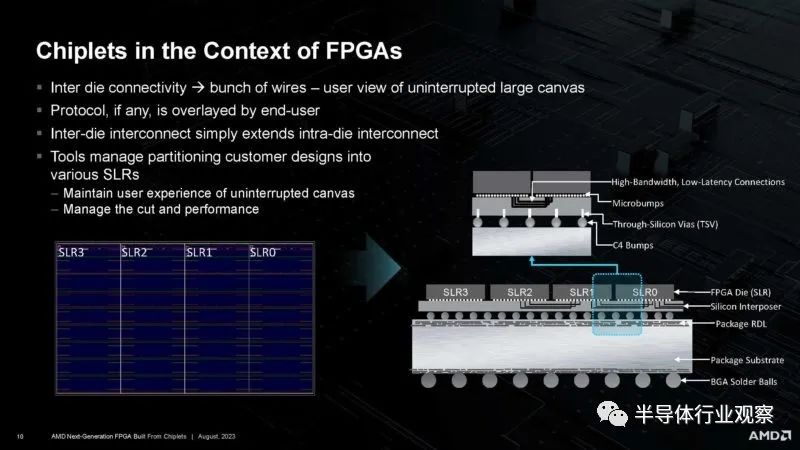

这就是芯片间的连接以及芯片的封装方式。FPGA 不仅需要具有小芯片到小芯片的连接性,而且通常还需要支持极高速和密集的外部 I/O。

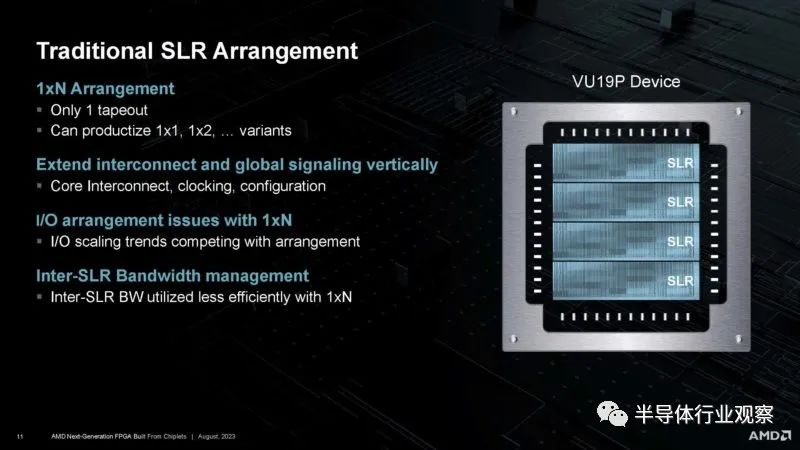

这是之前 VU19P 中的小芯片。

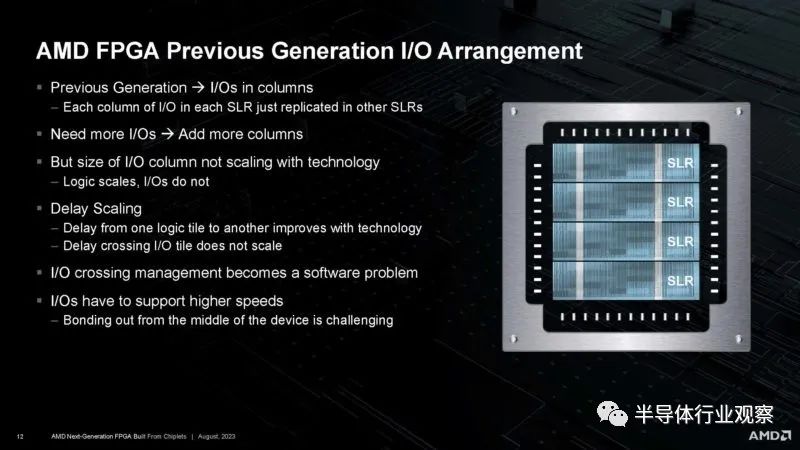

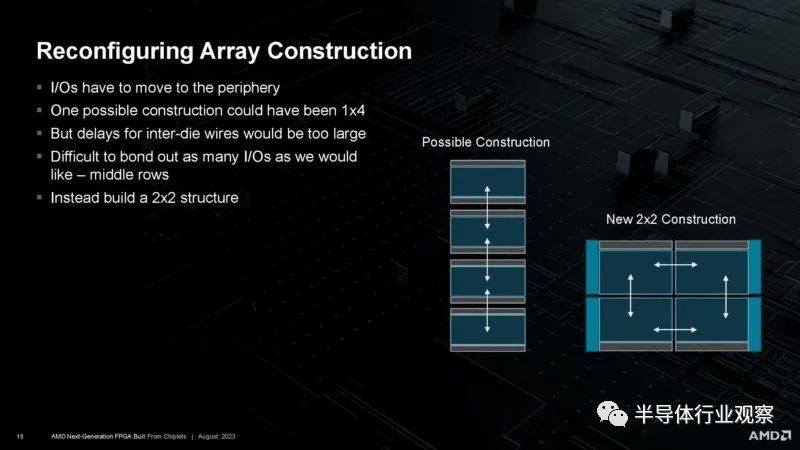

该方法的 I/O 列无法扩展。这里真正有趣的是,这些又长又宽的小芯片正是英特尔在 Hot Chips 2023 上改变其 Xeon CPU 架构时所展示的。一个关键的区别是,端盖芯片是英特尔设计中 UPI、PCIe Gen5 和 CXL 等 I/O。

以下是象限方法的构建方式,与当前的 Sapphire Rapids Xeon 更相似。

作为本次会议的一部分,AMD 展示了如何使用 2×2 而非 1×4 来降低轨道需求。

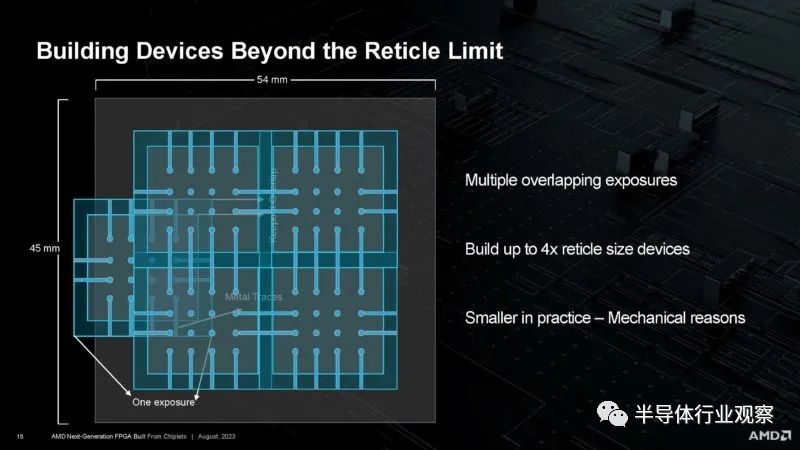

Chiplet 还允许 AMD 突破单片芯片(无Cerebras)的制造尺寸限制。

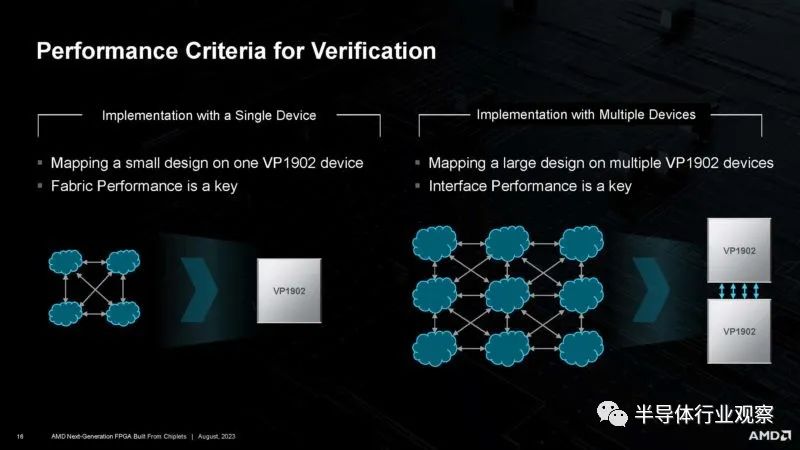

现在 AMD 正在讨论扩展到更多设备的性能标准。

这是 AMD 的性能指标。

以下是有关影响的更多信息。

这是新的界面性能:

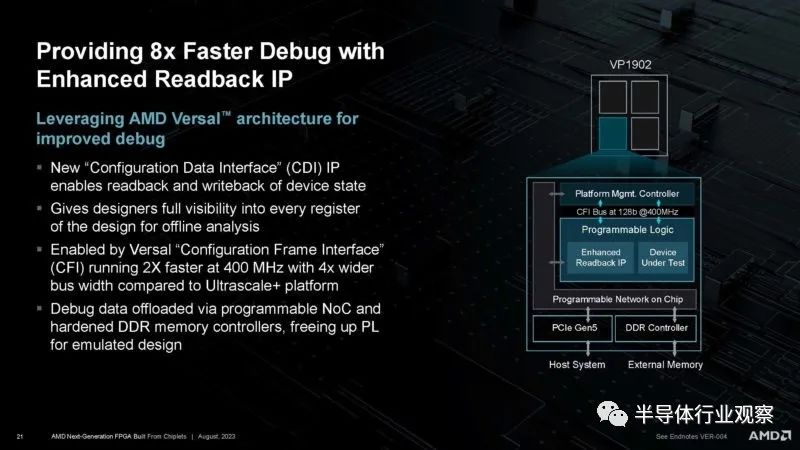

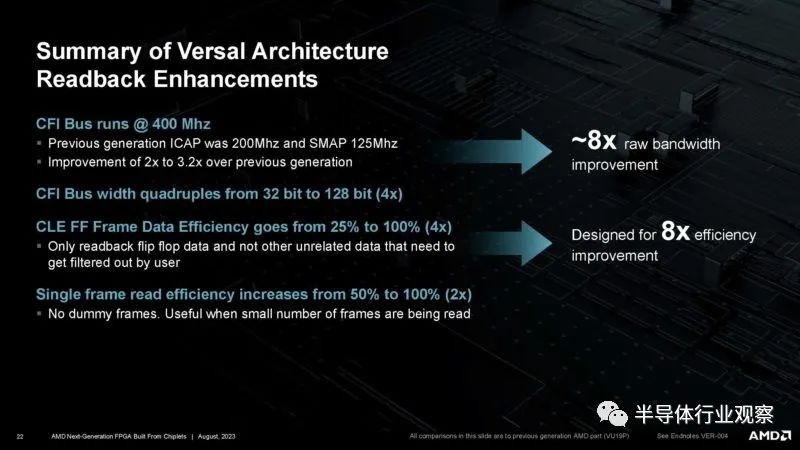

以及验证中 FPGA 结构的读回性能。

对于芯片验证工程师来说,了解每个寄存器的新能力非常重要。

以下是刚刚介绍的内容的摘要。

这是 AMD 关于扫描链方法的幻灯片。

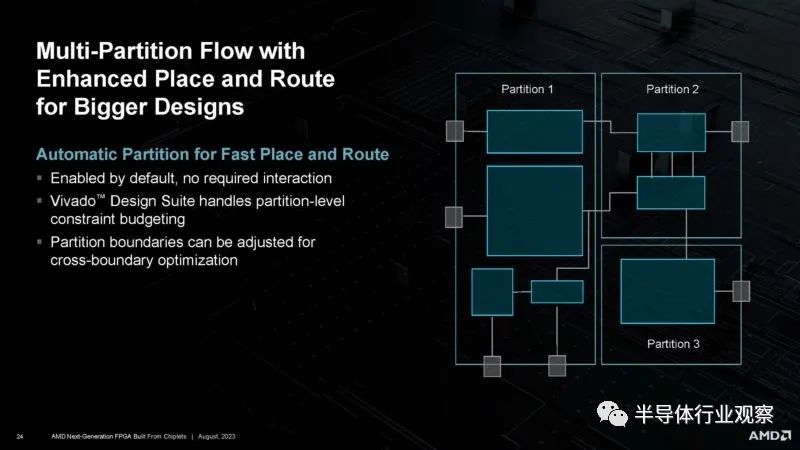

这是 AMD 的多分区流程,可实现更快的布局和布线。

这是演讲的摘要幻灯片。

参考链接

https://www.servethehome.com/amd-versal-premium-vp1902-next-gen-chiplet-...

本文转载自: 半导体行业观察微信公众号