串行器/解串器(SerDes)电路多年来一直在帮助芯片间进行告诉数据通信,但新的工艺技术正迫使它以意想不到的方式进行调整和改变。

传统上作为模拟电路实现的SerDes技术一直难以进一步缩小尺寸,而低电压、变化和噪声则使其更难获得充分的量产。因此,为了保持相关性,它在架构上已经转变为复杂的混合信号电路,它越来越依赖数字信号处理来处理半导体和通道中的缺陷。

先进封装对SerDes提出了新的要求,同时在涉及异构芯片时也提供了新的机会。现在,可以将SerDes设计与核心设计脱钩,从而为每种工艺提供最佳选择。但是先进的封装也为芯片之间的通信提出了全新的需求。关于这是并行通信还是串行通信通道,或者即使电气通信具有长期作用,仍需进行评审。

保持不变的一件事是,用于移动数据的驱动器并未减慢速度。“我们看到了对高速数据传输的巨大需求,”西门子业务部门Mentor的模拟Fast-SPICE产品线的高级产品经理Greg Curtis说。“每天上传的照片超过20亿张。视频大约占下游总流量的60%,尤其是当人们在家工作时。然后,这将推动自动驾驶汽车的发展。所有这些数据都必须从应用程序传输到可以处理数据的内容。这必须经过SerDes设计的发送器和接收器。该管道正在成为传输所有数据的瓶颈,需要更高的带宽。”

在进行单片集成和小芯片之间的权衡取舍之前,先了解一下SerDes电路中正在发生的架构变化是有益的。“直到几年前,SerDes还是相对简单的,” Silicon Creations的负责人兼联合创始人Jeff Galloway说。他们现在已经发展成为高端,复杂的PAM4系统。PCIe rev 5及更低版本以每秒32 Gb的速度运行,并且是两级SerDes,而高级进程实际上并没有太大帮助。除了每秒32G比特外,大多数SerDes都是PAM4。这种区别在架构上有很大的不同。“

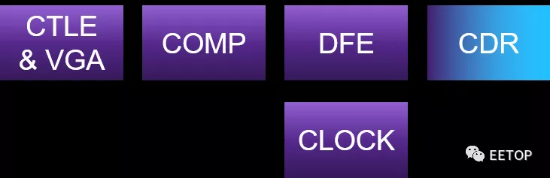

传统的SerDes如图1所示。”上一代SerDes曾经是模拟的,您具有连续的时间线性均衡(CTLE)电路,可以放大和部分均衡信号,“高速SerDes产品营销经理Priyank Shukla解释说。Synopsys的IP 。”这之后是一个比较器,该比较器做出1位判决和判决反馈均衡器(DFE)。时钟和数据恢复(CDR)也大多以模拟方式实现。“

图1:SerDes的传统模拟实现。资料来源:Synopsys

问题是,在最新的节点中,模拟经历的变数比过去多得多。”数字设计比模拟设计更容易预测。“Mentor的Curtis说。”设计团队要尽量向数字方面转移,但仍有一些功能无法转化。“

从16nm开始,在速度大于56Gbps时,图2所示的架构更有可能被使用。

图2:混合信号SerDes框图。资料来源:Synopsys

Synopsys的Shukla说:” SerDes接收器实质上消除了信道损伤。“ ”其中许多现在可以通过数字方式完成。接收器只是有一个模数转换器(ADC)。可以进行时间交织以获得更高的数据速率。之后,可以获得数字样本,并且可以使用DSP进行处理,从而可以很好地扩展该技术。这包括前馈均衡器(FFE)。“

这些设计是经过充分验证的。Xilinx技术市场经理Martin Gilpatric表示:”我们的56G和112G收发器已经转向基于ADC/ dsp的接收均衡策略。“这需要大量典型的模拟电路,并将其转换成数字逻辑。随着PAM4以如此高的速度移动,边际成本极低,我们能够解决所有的问题,并拥有一个非常强大的数字接收器。”

架构的选择和大量正在使用的过程节点意味着对于SerDes IP提供商来说是好时机。SiliconCreations的Galloway说:“行业无法满足更多需求。” “例如,TSMC正在添加22nm变体和低功耗变体。当开发40nm或开发28nm时,一些较旧的技术和某些较晚的PCIe标准还不成熟。PCIe 5.0即将到来,我们已经远远超过16nm。在较旧的技术上有很多设计开始,因此基本上需要在较旧的节点上回填各种标准。”

新挑战

较新的节点正在面临挑战。Galloway说:“底层晶体管不断变得越来越小,功耗越来越低,但是互连却越来越差。” “互连电阻和电容会给您带来复杂的布局效果。由于存在额外的寄生效应,从而导致了速度限制已经额外功耗。”

Mentor的Curtis通过数字举例说明:“我们的一个客户提到,当从40nm到5nm时,互连电阻的增加,已经上升了7倍以上。这实际上已经限制了线材的性能,远远超过了设计。”

“GDS层的数量正在大幅增加,”Curtis补充道。“当从180nm下降到5nm时,这增加了9倍。其影响是设计规则检查(DRC)的运行时间。从180nm降到16nm finFET,运行DRC检查所需的时间约为10倍。然后你从16降到5,又是10倍。”

另一个因素是噪音。“与先进工艺节点相关的噪声正在成为一个重大挑战,”Shukla说。“噪音是ADC的一个难题。对于选择的结构是逐次逼近寄存器(SAR)型ADC,这是一种模块化的方法。需要在这个ADC的许多slices中进行交错处理。对SAR的不同slices进行对齐是有挑战的,但这可以通过数字方式得到补偿。所以无论模拟出现什么挑战,我们都有办法弥补。这也是很多创新正在发生的地方。”

Mixel首席执行官AshrafTakla表示:“我们知道,有一些巧妙的电路设计技术可以用于模拟设计,特别是SerDes,在不影响性能的情况下继续支持先进技术。”例如,在使用I/O电压的同时堆叠薄氧化物晶体管,是继续以先进技术设计高性能SerDes IP的一种方式。“

新晶体管可能带来新挑战。”在最新的节点上,如果晶体管技术切换到全能门(GAA),那么就不可能从经济角度出发以合理的方式集成SerDes,“高级系统集成与集成部门负责人Andy Heinig说。Fraunhofer IIS自适应系统工程部高效电子部门主管。”必要的SerDes面积将不断增长或被卡住,但是GAA晶体管的成本更高。仅当使用缩放比例时,GAA才有意义。从我们的角度来看,将SerDes集成到另一个芯片中的专用技术系统中,并以先进的封装技术将其与GAA芯片相结合是有意义的。“

单片集成的案例

设计团队面临的一个新决策是,他们是否应该将所有内容都集成到单个单片芯片上还是采用多芯片异构解决方案。这两个选择之间的动态关系几乎每天都在变化。”如今,多芯片封装非常昂贵,“ Flex Logix首席执行官Geoff Tate说。”除非进一步降低成本,否则对成本敏感的应用将继续青睐整体式Die。即使SerDes可能不是最佳选择,它当然也更便宜。“

转到新节点的许多好处与PPA收益有关。”如果设计是纯模拟的,那么除非电源电压发生变化,否则从28nm到16nm再到7nm不会节省多少功耗,“ Cadence产品营销总监Wudy Wu说。”采用基于DSP的设计,尽管仍然有很大一部分模拟电路,但40%至50%的电路是数字电路。因此,当下降到较小的节点时,我们可以从面积和功耗中受益。如果我们保持100%的模拟设计,那么这种动力就会减弱。“

有时,由于某些特定原因,单片集成是唯一可接受的解决方案。赛灵思芯片营销总监Manuel Uhm表示:”我们特别选择了单片解决方案,因为这在降低延迟,降低功耗和散热方面提供了最佳结果。“几年前,我们率先开发了小芯片,例如将高带宽存储器耦合到FPGA芯片或将多个FPGA芯片耦合在一起。所有这些选项对我们来说都是摆在桌面上的,但是我们绝对不会离开将SerDes集成到芯片上的想法。

小芯片案例

在数字化设计中,只需重新综合即可将同一设计从7nm移至5nm。SerDes混合信号设计,如果我们需要移植SerDes混合信号设计,则需要更长的时间。一个关键的动机是,通过使用小芯片方法,将SerDes设计周期与核心设计周期脱钩。

在移动领域,更重要的问题是空间,小芯片方法可以让芯片垂直堆叠,这样就可以在可预见的未来继续集成更多的功能。对于已经有中间件的设计来说,在电源分配是一个问题的情况下,它提供了成本优势。因此,SerDes的采用者都可以通过这类方法获得一些好处,你可以将裸片隔离开来。”

即使采用新的SerDes架构,扩展速度仍在放缓。Galloway说:“他们不再在面积或功率上扩大规模。” 从一个节点到另一个节点的迁移无助于传统的32Gbps及以下的SerDes。对于某些基于DSP的高级SerDes,缩放在一定程度上有所帮助,但是缩放的速度肯定不及数字逻辑的缩放速度。“

成本是许多设计的重要因素。”根据我们的经验,16 / 12nm是非常适合模拟设计的工艺,“ Mixel的Ashraf说。”与28nm相比,它的Ft / Fmax高得多,而余量比5nm大。“ 我们还考虑到设计的复杂性,工作量和工具成本从16 / 12nm增加到7/6 / 5nm的情况。当16nm速度不足以达到目标数据速率时,则需要高级节点。另外,我们可以看到更多的人采用小芯片。小芯片是使模拟和SerDes模块能够使用最合适,最便宜的处理技术,同时允许数字模块使用更高级节点的好方法。解决了互连标准化难题之后,我们预计小芯片将被广泛采用。”

设计工作可能是造成成本的重要因素。“从缩放角度来看,从180nm到5nm的数字芯片面积缩放比例大于1,000倍,” Curtis说。“从模拟缩放角度来看,它的数量级大约是10倍。与数字信号相比,模拟信号也很难描述。我并不是说您无法描述它的特征。这更加困难,并且变量更多。这就是为什么在PVT corner分析上花费更多时间的原因。”

结论

这其中有很多是前瞻性的思考。“裸片到裸片接口是共同设计的,今天通常由同一家公司设计,”Galloway说。“它们甚至可能是同一设计的不同实例,所以对标准化的需求较少,那里的互操作性问题较少。我们处于起步阶段,还没有真正的标准来解决许多客户正在尝试做的事情。这对客户来说还好,但对IP的可用性有影响。”

一直以来,在封装内或封装外对速度的需求都在增加。Wu表示:“明显的趋势是联合封装光学器件。”目的是用光学器件代替长距离的SerDes。只要看看从事这项工作的初创公司的数量即可。我不认为61Tb交换机会采用共封装光学器件进行商业生产。可能会有一些原型,但可能会是100Tb。这是三年后的事情。光纤的走线是最大的问题,以及如何做到量产。

但业界并不准备在必要时放弃铜缆。“你是转到PAM8电气连接,还是转到某种学片外芯片?在如何整合特定技术方面,这是一个非常完整的行业问题。”Gilpatric说。

文章来源:EETOP