开发者分享 | Vivado 仿真器中的通用验证方法学(UVM)支持

judy 在 周二, 05/19/2020 - 15:31 提交

Vivado 集成设计环境支持将通用验证方法学 (UVM) 应用于Vivado 仿真器。Vivado 提供了预编译的 UVM V1.2 库。请遵循以下步骤创建示例设计测试案例,以便在工程模式下使用 UVM。本文随附了 1 个简单示例,可供您下载解压使用。

Vivado 集成设计环境支持将通用验证方法学 (UVM) 应用于Vivado 仿真器。Vivado 提供了预编译的 UVM V1.2 库。请遵循以下步骤创建示例设计测试案例,以便在工程模式下使用 UVM。本文随附了 1 个简单示例,可供您下载解压使用。

随着人工智能和5G的兴起,数据处理对芯片的算力和带宽要求更高。为了布局未来,助力人工智能和5G,赛灵思也推出了自己的FPGA加速芯片-ACAP。ACAP是一款基于7nm工艺,集成了通用处理器(PS),FPGA(PL),math engine以及network-on-chip的革命性芯片。

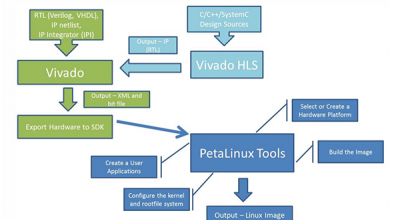

本篇博文涵盖了配置设备树以将外设和第三方应用详细信息添加到 PetaLinux 工程中的基本流程。在某些情况下,设备树无法生成相关外设所需的所有必需信息,例如,以太网 PHY 信息。在此类情况下,您需要手动将此板级信息和特定开发板信息添加到设备树文件 (system-user.dtsi) 中。

今天, 赛灵思宣布,正在全球四所最负盛名的高等学府设立“赛灵思自适应计算集群( Xilinx Adaptive Compute Clusters,XACC )”。赛灵思诚邀全球顶尖高校加入 XACC 项目,在采用了赛灵思最新自适应计算加速技术的集群上合作开展尖端 HPC 研究。

全球范围内,每年会安装数千万个 IP 摄像头。如果我们假设全球已经安装了1亿个 IP 摄像头(保守估计),且每台摄像机都在 7x24x365 (当然也有可能上是366)的工作频率下以 30fps 的速度采用非智能方式传输 H.264 编码高清视频,那么,每年所需的总带宽将为约 859Tbps 或 3.4ZB

本文描述了如何使用XMPU、XPPU和TrustZone提供的硬件和软件机制来隔离子系统。

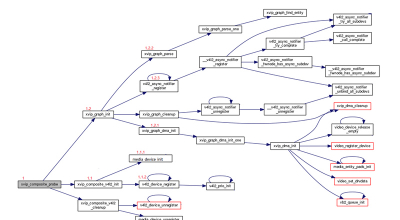

Xilinx提供了完整的V4L2的驱动程序,Xilinx V4L2 driver。处于最顶层的驱动程序是V4L2框架的视频管道(Video pipeline)驱动程序,也叫桥驱动程序(bridge driver),主要代码在文件xilinx-vipp.c中。在V4L2框架中,整个视频管道(Video pipeline)可以通过媒体设备(/dev/media)配置

现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手

有些应用中,单板没有DDR,OCM又不够存储所有数据和指令。这种情况下,Xilinx提供了参考设计Zynq-7000 AP SoC Boot - Booting and Running Without External Memory,把代码和只读数据放在QSPI Flash中运行程序,这就是execute in place (XIP)。

2011年,德国鲁尔大学的两位博士花了3000美元和7个小时成功破解了Mifare DESFire MF3ICD40使用的安全算法,但这个破解在现实生活却没有任何价值,因为一颗RFID芯片的价值只有几分钱,没人傻到去花大钱去破解一个几乎免费的芯片