Xilinx Kintex-7系列XC7K410T-FFG900外设之DDR3硬件设计

judy 在 周三, 04/17/2024 - 09:44 提交

基于K7+C665x为核心的电路板中用到了DDR3存储芯片,现将FPGA外接DDR3时硬件设计中的一些心得做一个简单的分享

基于K7+C665x为核心的电路板中用到了DDR3存储芯片,现将FPGA外接DDR3时硬件设计中的一些心得做一个简单的分享

在DDR读写的设计中,有一些比较经典的问题,是在设计中必须考虑到的,这些问题会影响项目的整体方案或者架构

在DDR读写的设计中,有一些比较经典的问题,是在设计中必须考虑到的

在实际的DDR使用场景中,一般有如下2种场景,一个是把ddr当成一个大fifo

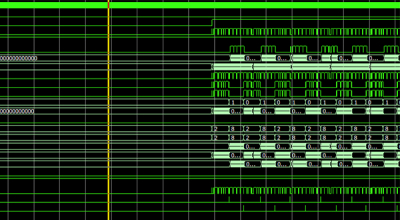

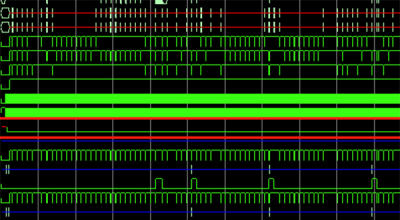

前面modelsim已经仿真成功了DDR3的初始化

在生成example的时候,vivado就自带仿真激励的

查看MIG IP输出的init_calib_complete信号

内置校准: DDR3和DDR4控制器通常具有内置的校准机制

话说之前从来没有使用过DDR,工作中的项目都是流式处理的

本文总结了DDR3带宽的计算方法