显示屏连接:不断发展以满足 8K 标准 – 为 8K 做好准备(2)

judy 在 周三, 08/16/2023 - 14:47 提交

音频/视频(A/V)接口是任何显示系统不可或缺的一部分

音频/视频(A/V)接口是任何显示系统不可或缺的一部分

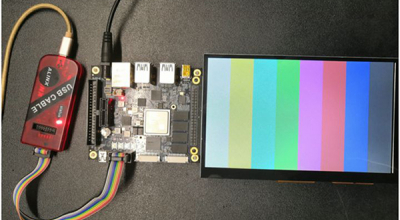

本实验使用FPGA通过HDMI接口输出彩条、色带、方块等图像。

目前基于MPSOC的一些参考设计中并没有实现开机画面的功能 ,那在一些带显示屏的产品在设计的时候就需要这一功能,基于原来传统的方式也可以在FPGA中来实现,今天分享一个在PS侧来实现开机画面,以节省PL侧的宝贵资源。

基于HDMI输出实验,本章介绍7寸液晶屏的显示。LCD屏显示方式从屏幕左上角一点开始,从左向右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步

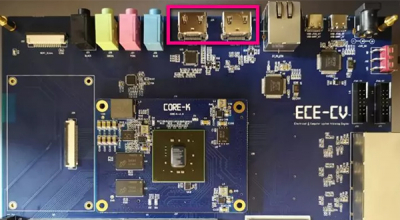

前面我们介绍了led闪灯实验,只是为了了解Vivado的基本开发流程,本章这个实验相对LED闪灯实验复杂点,做一个HDMI输出的彩条,这也是我们后面学习显示、视频处理的基础。实验还不涉及到PS系统,从实验设计可以看出如果要非常好的使用ZYNQ芯片,需要良好的FPGA基础知识。

HDMI主要用于给高清显示设备传输视频和音频数据,除了使用专门的HDMI芯片外,当然还可以用ZYNQ的PL部分产生相应的时序,本文就是用FPGA的IO口与HDMI显示设备直接进行通信。

HDMI 1.4 / 2.0发送器子系统是一个分层IP,它捆绑了一组HDMI™IP子核心并将其输出为单个IP。 它是一个现成的即用型HDMI 1.4 / 2.0发送器子系统,无需手动组装子核心即可创建可用的HDMI系统。

许多视频 IP 核都附带有示例设计。这些设计用于 IP 演示,并提供示例以供您在自己的设计中使用 IP 核时作为参考。赛灵思 HDMI IP 核分为两种:源端 (Source) IP 核 (HDMI 1.4/2.0 TX Subsystem) 和 Sink IP 核 (HDMI 1.4/2.0 RX Subsystem)。

HDMI高清多媒体界面(英语:High Definition Multimedia Interface)是一种全数字化视频和声音发送接口,可以发送未压缩的音频及视频信号。HDMI可用于机顶盒、DVD播放机、个人计算机、电视游乐器、综合扩大机、数字音响与电视机等设备。HDMI可以同时发送音频和视频信号,由于音频和视频信号采用同一条线材,大大简化系统线路的安装难度

本文从软件工程师角度对HDMI spec进行解析,基于的spec版本为1.4,也是设备支持最多最成熟的版本,目前最新版本为2.0。

1 概述