Xilinx Srio IP学习笔记之初识Srio

judy 在 周四, 01/12/2023 - 16:33 提交

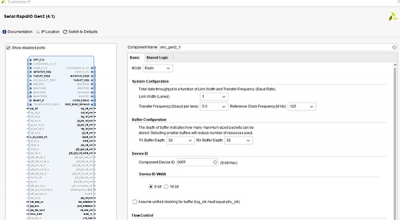

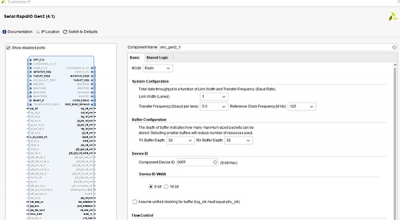

因为工作原因,需要对rapidio 的协议进行了解,在xilinx的IP核中,是对应着Serial RapidIO Gen2 这个IP核

因为工作原因,需要对rapidio 的协议进行了解,在xilinx的IP核中,是对应着Serial RapidIO Gen2 这个IP核

RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接。

参考

书籍《RapidIO The Embedded System Interconnect》

xilinx手册pg007《Serial RapidIO Gen2 Endpoint v4.1 LogiCORE IP Product Guide》

Zynq-Linux移植学习笔记之14-RapidIO驱动开发

Rapid IO协议由于无主机,且各设备之间可以并行交换信息,所以广泛应用于对交换速率要求高,且交互复杂的应用中。