FPGA,被RISC-V完全征服

judy 在 周四, 04/18/2024 - 11:21 提交

不知不觉中,FPGA 的 MCU 市场已经成为 100% 基于 RISC-V 的市场,我们也在逐步进入应用处理器市场

RISC-V是一种基于精简指令集计算机(RISC)架构的开源指令集架构(ISA)。与其他商业架构(如ARM或x86)不同,RISC-V是由加州大学伯克利分校的学术界和行业合作伙伴开发的,它是一种开放、免费的指令集架构,具有可扩展性和灵活性。

RISC-V的设计目标是提供一种简洁、灵活且可扩展的架构,使其能够适应各种不同的应用场景,从微控制器到超级计算机等。RISC-V架构采用了模块化设计的理念,定义了基本的指令集,并允许用户根据自己的需求添加自定义指令集扩展(ISA扩展),从而实现对特定应用的优化。

由于其开放的特性,RISC-V架构在学术界和工业界都受到了广泛的关注和采用。它已经成为了各种不同领域的研究和开发的重要工具,如嵌入式系统、物联网、人工智能、边缘计算等。很多公司和组织都开始采用RISC-V架构设计自己的处理器芯片或者开发板,以满足不同领域的需求。

总的来说,RISC-V作为一种开放、免费的指令集架构,具有可扩展性、灵活性和通用性,已经成为了计算机体系结构领域的重要创新,并在全球范围内得到了广泛的应用和推广。

不知不觉中,FPGA 的 MCU 市场已经成为 100% 基于 RISC-V 的市场,我们也在逐步进入应用处理器市场

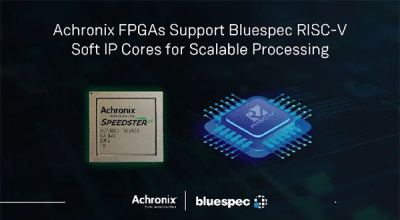

Bluespec支持加速器功能的RISC-V处理器将Achronix的FPGA转化为可编程SoC

Bluespec近日宣布已加入Xilinx Partner Program,并向Xilinx用户开放两款优化升级的RISC-V处理器IP。这两款RISC-V处理器系列是为了满足不同性能和资源的需求而定制的,可以在Xilinx的Vivado和Vitis环境下使用

RISC-V-On-PYNQ Overlay实现了在PYNQ-Z2板上的RISC-V处理器及工具链集成,并提供了完整的RISC-V源码与设计流程,得益于PYNQ软件框架,其支持在Jupyter Notebook对RISC-V进行编译、调试与验证,即可以在Jupyter Notebook上编写一段C/C++/RISC-V汇编程序,将编译后的二进制文件放到picoRV32上运行

2019年8月1日至2日,“中国开放指令生态(RISC-V)联盟”(简称CRVA联盟)与鹏城实验室,在湖北恩施举行的中国计算机学会第二十三届计算机工程与工艺学术年会暨第九届“微处理器技术”论坛(NCCET 2019)现场,联合展示了最新研发的RISC-V开源芯片设计系统级验证及原型平台SERVE,介绍开源理念并鼓励参会人员积极参与。