Vitis HLS AXI_master总线的突发读写概览

judy 在 周二, 12/07/2021 - 17:55 提交

本文给大家分享系统级别的一些宏观概念以及如何预估 HLS 内核向 DDR 发送突发读写在各个步骤中的延迟。

本文给大家分享系统级别的一些宏观概念以及如何预估 HLS 内核向 DDR 发送突发读写在各个步骤中的延迟。

Vitis Vision库是OpenCV和Vision功能的加速库,可在Vitis环境中使用,这些库的L1目录是示例设计。为了适应各种用户环境,从2020.1版本开始,Xilinx不再使用Vivado / Vitis工具提供预安装的OpenCV版本。尽管Vitis_hls编译Vision库不需要OpenCV,但是用户测试验证使用时OpenCV。

为期2天的培训课程,介绍了基于Vitis HLS工具的综合策略、特性,如何最优化吞吐量、面积、延迟、接口创建、仿真代码编辑和编码注意事项;最终,还将通过基于图像处理的实际案例分享,给学员展示完整的Vitis HLS工程开发过程,以及如何进行有效的设计优化和调试。

HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

本视频说明了如何消除由 C 设计中的阵列引起的瓶颈。

视频展示了如何在 Vitis™ HLS 工具中指定端口级协议。

本视频重点介绍了 Vitis™ 高层次综合工具的主要功能。

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

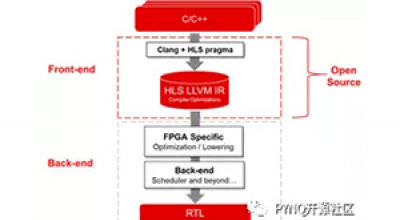

赛灵思一直致力于支持开源计划的不断飞跃,为帮助开发人员和研发社区充分发挥自适应计算的优势,我们再次做出了令人振奋的举措: 在 GitHub 上开放提供 Vitis HLS(高层次综合)前端。Vitis HLS 工具能够将 C++ 和 OpenCL™ 功能部署到器件的逻辑结构和 RAM/DSP 块上。

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技术的不断进步,以及算法迭代的日益频繁,人们似乎并不满足于此。

不少刚刚接触到Pynq的用户第一个问号?Pynq是不是用Python编程FPGA的新物种?