协处理器架构:一种用于快速原型开发的嵌入式系统架构

judy 在 周五, 08/27/2021 - 15:14 提交

本文重点介绍分立式微控制器 (MCU) 和分立式现场可编程门阵列 (FPGA) 的组合,展示了这种架构如何适合高效和迭代的设计过程。利用研究资料、实证结果和案例研究,探讨这种架构的好处,并提供示范性的应用。读完本文,嵌入式系统设计者将对何时以及如何实现这种多功能硬件架构有个更好的理解

本文重点介绍分立式微控制器 (MCU) 和分立式现场可编程门阵列 (FPGA) 的组合,展示了这种架构如何适合高效和迭代的设计过程。利用研究资料、实证结果和案例研究,探讨这种架构的好处,并提供示范性的应用。读完本文,嵌入式系统设计者将对何时以及如何实现这种多功能硬件架构有个更好的理解

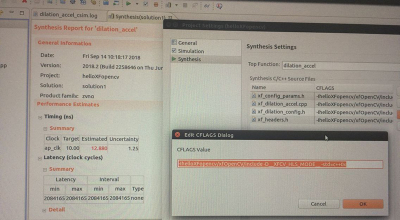

我们在进行HLS编译的时候会设置顶层文件,顶层文件中包括形参、返回值等等。这些映射到硬件电路中会产生信号,这些信号具体又遵循什么样的接口描述我们需要设置,这不仅可以帮助我们设置更优的约束条件使得编译出来的硬件电路更加完美,更重要的是可以让我们精确了解端口所遵循的时序

了解如何使用 Vivado HLS 可视化数据流设计的专用波形。这些波形轨迹有助于确认数据流已实现的并行性。

本来写了一篇关于在HLS中使用xfOpenCV的记录,一步一步,但不小心删掉了。只能重新大致回忆下,肯定没有之前的全面。

本视频介绍了 Vivado HLS 工具从 C 语言设计中抽象出来的端口级协议。

深入介绍高层次综合及 Vivado HLS 工具的基础知识。

据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,HLS可以在一定程度上降低FPGA的入门门槛(不用编写RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构

ug948中提供的官方例程为图像的中值滤波,该设计将一副256*256大小的RGB图像,添加噪声后提取出其中的Y通道,使用C++语言完成中值滤波。该设计将在Simulink环境下进行仿真。本次设计的流程是利用Vivado HLS建立C/C++代码,Export RTL–>System Generator–>Vivado。

ug948中提供的官方例程为图像的中值滤波,该设计将一副256*256大小的RGB图像,添加噪声后提取出其中的Y通道,使用C++语言完成中值滤波。该设计将在Simulink环境下进行仿真。本次设计的流程是利用Vivado HLS建立C/C++代码,Export RTL–>System Generator–>Vivado

作者: OpenSLee,来源:FPGA开源工作室

1. 背景知识