ZynqNet解析(八)对IPcore的HLS

judy 在 周四, 03/28/2019 - 10:00 提交

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。

背景:我们需要仿照ZynqNet的模式构造卷积的IPcore用于FPGA的优化。

目的:搞懂zynqNet的cache的实现。

在zynqNet项目之中,程序到底如何分配DRAM上的地址作为global Memory。以及如何分配相应程序的内存。

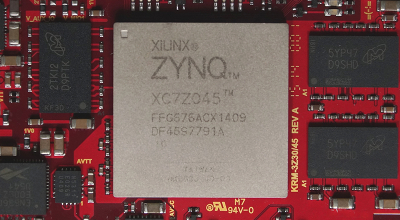

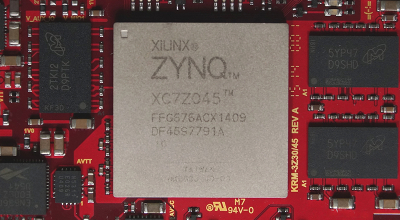

背景:ZynqNet能在xilinx的FPGA上实现deep compression。

目的:读懂zynqNet的代码中关于硬件实现的部分。

背景:ZynqNet能在xilinx的FPGA上实现deep compression的网络,FPGA端程序运用传入每层数据运算后存在DRAM上。

目的:读懂ZynqNet的FPGA端的代码。

FPGA端代码经过HLS高层次综合为硬件语言实现在FPGA上。为fpga_top.cpp与fpga_top.hpp

程序包括:

fpga_top

gpool_cache

image_cache

weights_cache

output_cache

processing_element

memory_controller

(数据定义中fpga_top.hpp需要包含了network.hpp与netconfig.hpp)

ZynqNet能在xilinx的FPGA上实现deep compression的网络。目的:读懂ZynqNetCPU端的代码。

背景:ZynqNet能在xilinx的FPGA上实现deep compression

目的:运行zynqNet的代码。

源码地址:https://github.com/dgschwend/zynqnet

项目程序架构,针对我们的项目,我们需要看懂相应的HLS程序和ARM端的程序。

ARM端的程序以_FIRMWARE为准;FPGA端程序以HLS为准。

1. _TRAINED_MODEL

这部分为训练好的caffe模型与预训练的权重。

2. _FIRMWARE

这部分程序针对Zynq 7Z035 ARM processor。make之后是在服务器上运行的,一次迭代需要将近3590ms

make

./test CPU|FPGA indata.bin (-quiet)

背景:ZynqNet能在xilinx的FPGA上实现deep compression。

目的:读懂zynqNet的代码和论文。

一、网络所需的运算与存储

1.1 运算操作:

1.2 Memory requirements:

1.3 需求分析: