SDAccel 和 Vitis 对Rtl 的Kernel的要求

guanxiao_505740 在 周五, 10/30/2020 - 11:11 提交

本节文章参考的代买为xilinx github上vitis 的事例工程,主要是讲解如何写用户自己的rtl kernel

本节文章参考的代买为xilinx github上vitis 的事例工程,主要是讲解如何写用户自己的rtl kernel

本演示将展示在 Ubuntu 操作系统上为 Alveo U200 加速卡安装部署软件的程序。部署软件的安装需要 Xilinx® 运行时 (XRT) 的软件包以及使用 DEB 安装包的部署 shell。

结合 SDSoC 和赛灵思 SDK,SDAccel 流现在是 2019.2 Vitis™ 统一软件平台的组成部分,便于开发者针对赛灵思器件上的所有软件任务使用统一平台。下面分享来自 DesignLinx 公司高级嵌入式软件工程师 Nathan Sullivan 所撰写的技巧

在 SDAccel 框架中,应用程序在主机应用程序和硬件加速的内核之间分配,它们之间具有通信通道。使用 C/C++ 编写并使用 API 抽象(如 OpenCL)的主机应用程序在 x86 服务器上运行,而硬件加速的内核在赛灵思 FPGA 内运行。由赛灵思运行时 (XRT) 管理的 API 调用用于与硬件加速器通信。

SDAccel™ 环境使用标准编程语言,提供开发和交付 FPGA 加速数据中心应用的框架。SDAccel 环境包括基于 Eclipse的综合开发环境 (IDE) 的熟悉的软件开发流程和能充分使用 FPGA 资源的架构最优化编译器。

本指南适用于希望使用 SDAccel 开发环境创建 FPGA 加速应用程序的软件开发者和 RTL 设计师。它向开发者介绍了基于 FPGA 加速的基本概念,并描述了以最佳性能加速应用程序的逐步方法。

本演讲资料介绍了使用 SDAccel 开发计算存储

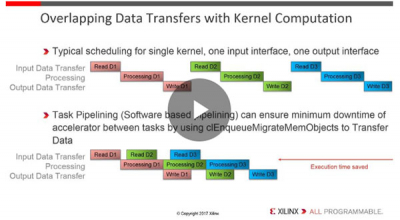

此培训视频介绍了如何开发、执行和分析在 AWS F1 上运行的加速应用。观看此视频,了解 SDAccel 执行模型和重要的 OpenCL API,分析和调试功能以及主机代码优化技术。

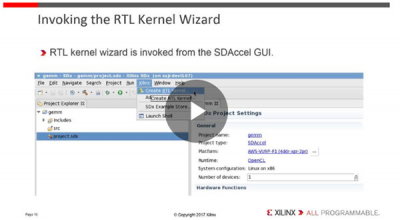

该培训视频涵盖了 SDAccel RTL 内核向导,并详细介绍了封装 RTL 设计、构建 FPGA 设计和生成 Amazon FPGA 映像(AFI)所涉及的步骤。

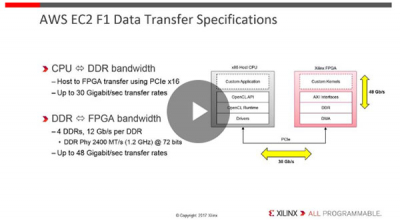

本培训视频介绍了 AWS F1 硬件平台的技术规格。观看此视频,以了解 AWS FPGA 中的各个区域,了解AWS F1 Shell 并查看重要的性能注意事项。