AMD Versal AI Edge 自适应计算加速平台之体验ARM,裸机输出(7)

judy 在 周日, 04/28/2024 - 10:33 提交

本章使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性

本章使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性

本实验通过PL端Verilog代码直接读写ddr4,主要了解NoC的配置方法

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次

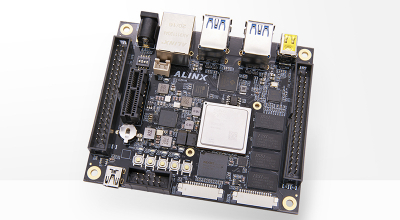

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分

每个工程下面都有一个生成vivado的脚本,用于重建vivado工程

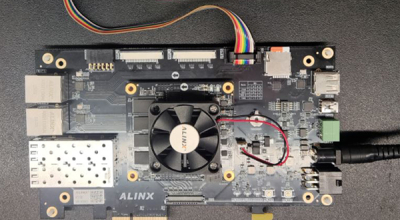

Versal AI Edge VE2302器件拥有应用处理单元双核Arm Cortex-A72、实时处理单元双核Arm Cortex-R5F

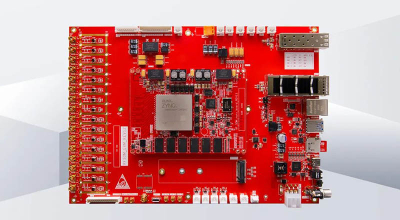

采用Zynq UltraScale+RFSoC Gen3系列ZU47DR FPGA芯片,集成射频直接采样数据转换器

大多数人可能没有意识到我们的设备在多大程度上是由时间驱动的,无论是你的手机、你的笔记本电脑还是网络服务器。在大多数情况下,设备保持准确的时间一直是一个深奥的苦差事,由有限的硬件制造商负责处理。虽然这些设备达到了它们的目的,但几位Facebook的工程师认为必须有一个更好的方法。

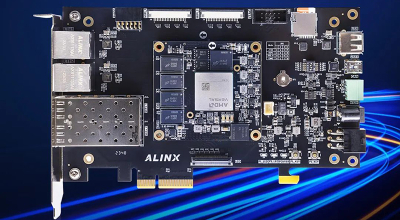

今天,先来推荐XILINX比较新的系列, Zynq Ultrascale+ MPSoC系列,主要针对中高端市场需求。Zynq® UltraScale+™ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。置于包含通用实时处理器和可编程逻辑的平台上

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。