作者:OpenSLee

1 背景知识

HDMI(High Definition Multimedia Interface)是高清晰多媒体接口线的缩写,能高品质地传输未经压缩的高清视频和多声道音频数据,最高数据传输速度为5Gbps。同时无需在信号传送前进行数/模或者模/数转换,可以保证最高质量的影音信号传送。

HDMI线支持5Gbps的数据传输率,最远可传输30米,足以应付一个1080p的视频和一个8声道的音频信号。而因为一个1080p的视频和一个8声道的音频信号需求少于4GB/s,因此HDMI线还有很大余量。这允许它可以用一个电缆分别连接DVD播放器,接收器和PRR。此外HDMI支持EDID,DDC2B,因此具有HDMI的设备具有“即插即用”的特点,信号源和显示设备之间会自动进行“协商”,自动选择最合适的视频/音频格式。如下图是一根HDMI线。

DMI接口的原理图

上图所示,HDMI接口有3对数据差分信号、一对时钟差分信号、HDMI_CEC(HDMI遥控器信号)、HDMI IIC信号、HDMI_HPD(HDMI热插拔检测信号)和HDMI_OUT_EN(HDMI电源输出控制)。本节设计将把RGB888转化为HDMI信号输出来控制显示屏的显示。

3 HDMI接口的FPGA设计

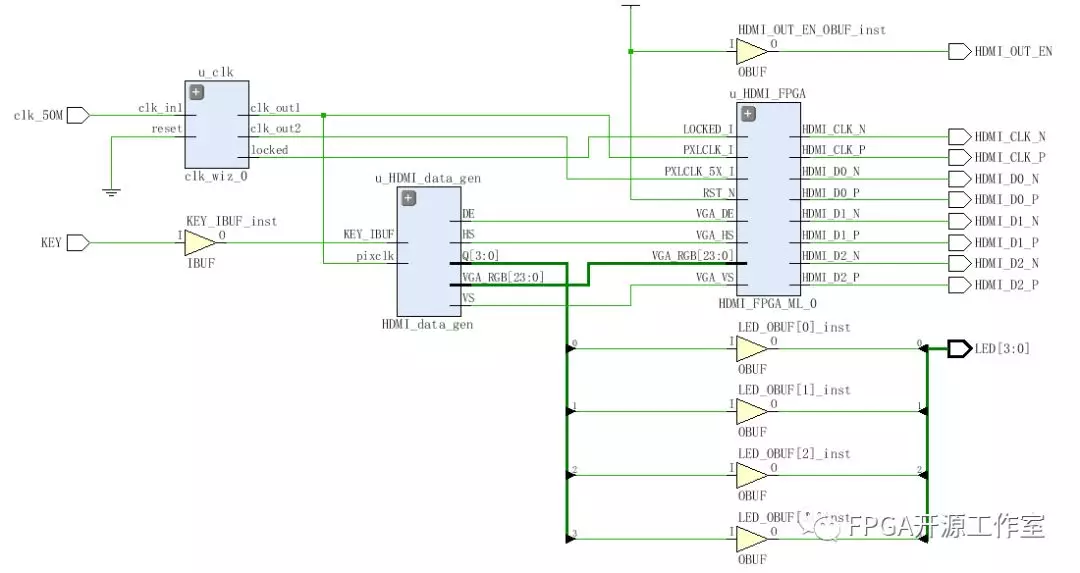

上图所示,为整个HDMI接口显示模块图。主要分为三个模块。

1)时钟产生模块

时钟产生模块主要产生VGA显示的像素时钟和HDMI的串行时钟。我们实验的显示器推荐设置为(1920x1080)所以pixel_clock为148.5MHZ。HDMI的串行时钟为pixel_clock的5倍为742.5MHZ。

2)HDMI_data_gen模块

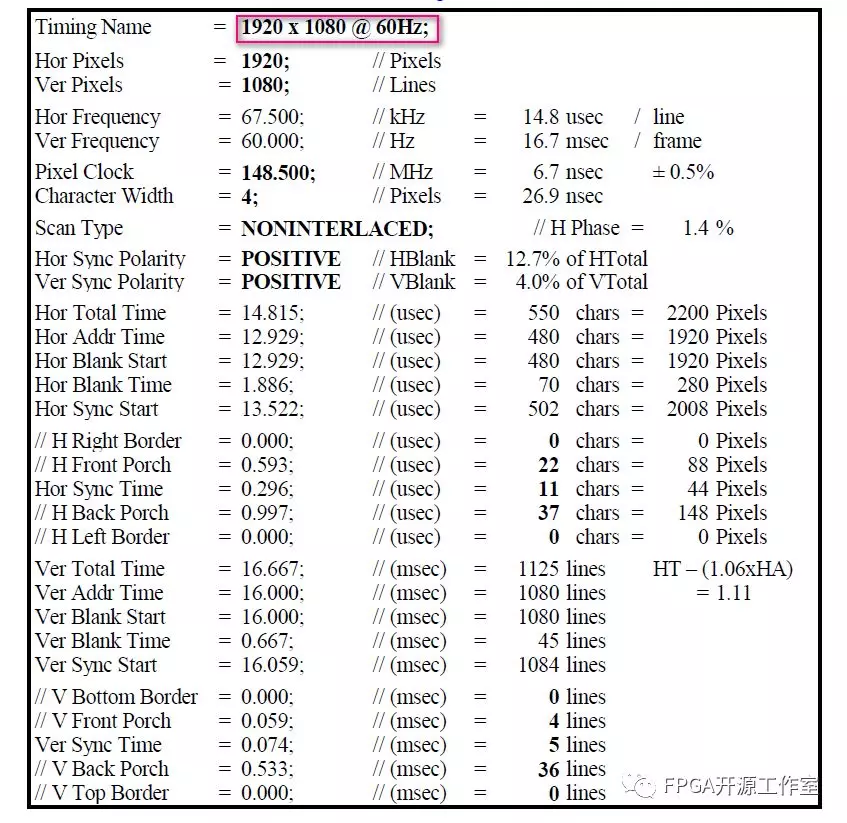

HDMI_data_gen模块主要产生VGA的时序和测试图像。我们这里采用1920x1080@60HZ。时序参数如下图所示。

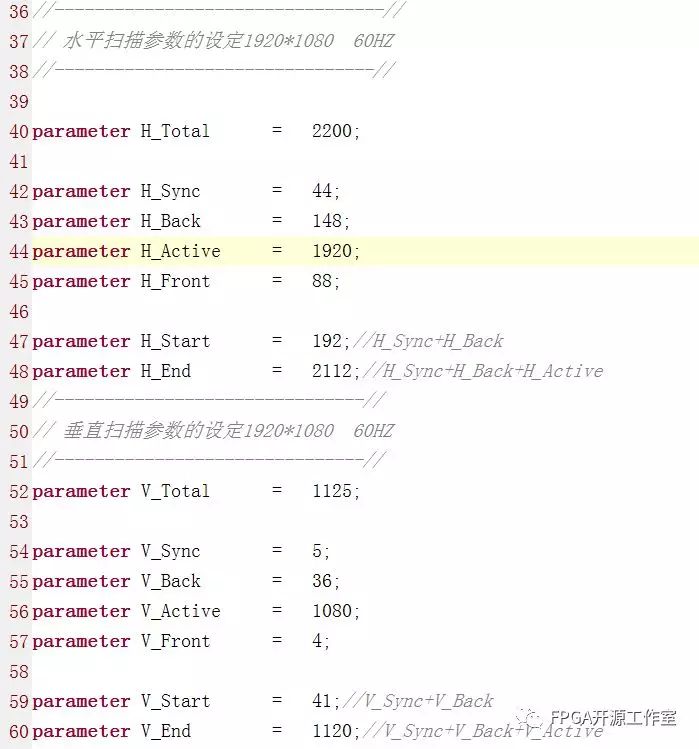

具体参数代码如下:

于按键程序和各种测试图像的产生请参考《基于FPGA的5英寸LCD屏显示》或联系FPGA开源工作室。

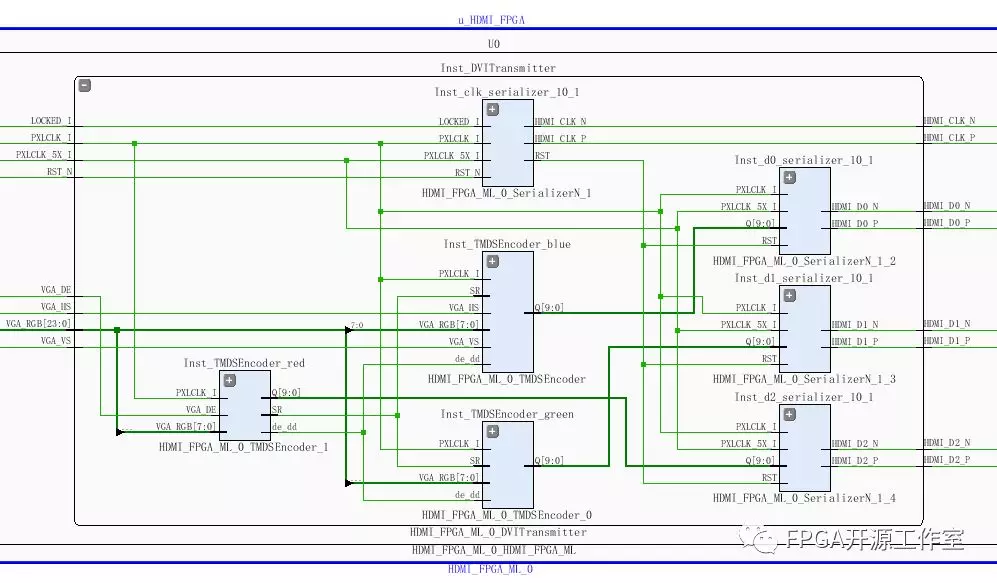

3)VGA转HDMI模块

这个模块我们采用IP。具体代码有兴趣的同学可以研究研究。VGA转HDMI的内部模块如下图。

4)代码和约束

顶层代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/08/27 16:50:00

// Design Name:

// Module Name: HDMI

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// FPGA开源工作室

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module HDMI(

input clk_50M,

input KEY,

output HDMI_CLK_P,

output HDMI_CLK_N,

output HDMI_D2_P,

output HDMI_D2_N,

output HDMI_D1_P,

output HDMI_D1_N,

output HDMI_D0_P,

output HDMI_D0_N,

output HDMI_OUT_EN,

output [3:0] LED

);

wire pixclk;

wire[7:0] R,G,B;

wire HS,VS,DE;

assign HDMI_OUT_EN = 1'b1;

HDMI_data_gen u_HDMI_data_gen

(

.pix_clk (pixclk),

.turn_mode (KEY),

.VGA_R (R),

.VGA_G (G),

.VGA_B (B),

.VGA_HS (HS),

.VGA_VS (VS),

.VGA_DE (DE),

.mode (LED)

);

wire serclk;

wire lock;

wire[23:0] RGB;

assign RGB={R,G,B};

HDMI_FPGA_ML_0 u_HDMI_FPGA

(

.PXLCLK_I (pixclk),//148.5MHZ

.PXLCLK_5X_I (serclk),//742.5MHZ

.LOCKED_I (lock),

.RST_N (1'b1),

.VGA_HS (HS),

.VGA_VS (VS),

.VGA_DE (DE),

.VGA_RGB (RGB),

.HDMI_CLK_P (HDMI_CLK_P),

.HDMI_CLK_N (HDMI_CLK_N),

.HDMI_D2_P (HDMI_D2_P),

.HDMI_D2_N (HDMI_D2_N),

.HDMI_D1_P (HDMI_D1_P),

.HDMI_D1_N (HDMI_D1_N),

.HDMI_D0_P (HDMI_D0_P),

.HDMI_D0_N (HDMI_D0_N)

);

clk_wiz_0 u_clk

(

.clk_in1 (clk_50M),

.reset (1'b0),

.clk_out1 (pixclk),

.clk_out2 (serclk),

.locked (lock)

);

endmodule

约束代码:

set_property IOSTANDARD LVCMOS33 [get_ports clk_50M]

set_property PACKAGE_PIN U18 [get_ports clk_50M]

create_clock -period 20.000 -waveform {0.000 10.000} [get_ports clk_50M]

set_property IOSTANDARD TMDS_33 [get_ports HDMI_CLK_P]

set_property IOSTANDARD TMDS_33 [get_ports HDMI_D0_P]

set_property IOSTANDARD TMDS_33 [get_ports HDMI_D1_P]

set_property IOSTANDARD TMDS_33 [get_ports HDMI_D2_P]

set_property IOSTANDARD LVCMOS33 [get_ports HDMI_OUT_EN]

set_property PACKAGE_PIN N18 [get_ports HDMI_CLK_P]

set_property PACKAGE_PIN V20 [get_ports HDMI_D0_P]

set_property PACKAGE_PIN T20 [get_ports HDMI_D1_P]

set_property PACKAGE_PIN N20 [get_ports HDMI_D2_P]

set_property PACKAGE_PIN V16 [get_ports HDMI_OUT_EN]

set_property IOSTANDARD LVCMOS33 [get_ports KEY]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}]

set_property PACKAGE_PIN N15 [get_ports KEY]

set_property PACKAGE_PIN M14 [get_ports {LED[0]}]

set_property PACKAGE_PIN M15 [get_ports {LED[1]}]

set_property PACKAGE_PIN K16 [get_ports {LED[2]}]

set_property PACKAGE_PIN J16 [get_ports {LED[3]}]

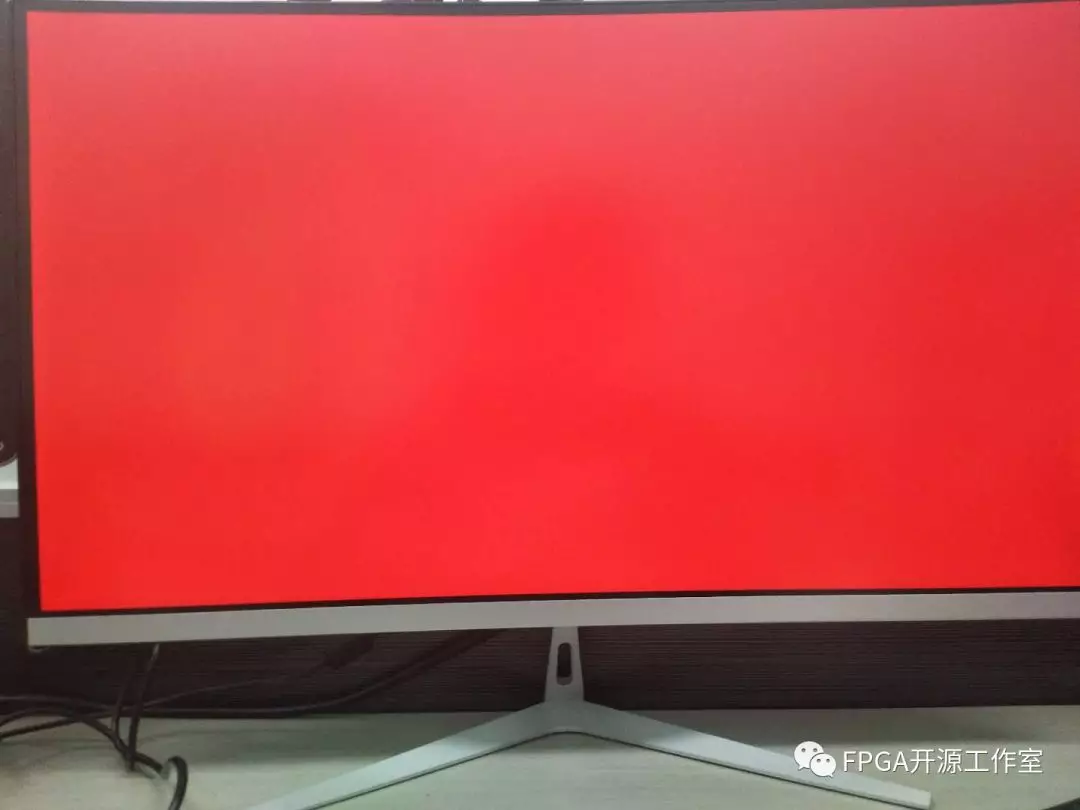

4下板测试

当按下按键时,我们的屏幕就会显示不同的测试图像。结果如下:

视频欣赏:

文章来源:FPGA开源工作室