如果给 DCM/PLL/MMCM 的输入时钟施加 PERIOD 约束,约束会自动传递给输出时钟。这些时钟被视为相关时钟而跨时钟域路径由时序分析器进行分析,我该如何从时序分析中排除跨时钟域路径呢?

解决方案 1

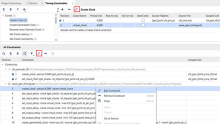

要从时序分析删除一组路径,如果您确定这些路径不会影响时序性能(False 路径),可用FROM-TO 约束以及时序忽略 (TIG) 关键字。这种方法要指定时序忽略 (TIG) 约束,应按如下定义:

以下给出 DCM/PLL/MMCM 的使用实例;假设 clk_in 是 DCM/PLL/MMCM 的输入时钟而clk_0、clk_90、clk_180 是输出时钟:

net "clk_in" TNM_NET = clk_in_grp; net "clk_0" TNM_NET = clk0_grp; net "clk_90" TNM_NET = clk90_grp; net "clk_180" TNM_NET = clk180_grp; TIMESPEC TS_clk_in = PERIOD "clk_in_grp" 10ns HIGH;

1.假定信号 clk_in 还驱动DCM/PLL/MMCM之外的其他同步元件

TIMEGRP "clk_out_grp" = "clk0_grp" "clk90_grp" "clk180_grp"; TIMESPEC TS_01 = FROM "clk_in_grp" TO "clk_out_grp" TIG; TIMESPEC TS_02 = FROM "clk_out_grp" TO "clk_in_grp" TIG;

这些约束忽略 DCM/PLL/MMCM 输入时钟和输出时钟之间的跨时钟域路径。

2.假定信号 ckl_in 只驱动 DCM/PLL/MMCM

TIMESPEC TS_01 = FROM "clk0_grp" TO "clk90_grp" TIG; TIMESPEC TS_02 = FROM "clk0_grp" TO "clk180_grp" TIG; TIMESPEC TS_03 = FROM "clk90_grp" TO "clk0_grp" TIG; TIMESPEC TS_04 = FROM "clk90_grp" TO "clk180_grp" TIG; TIMESPEC TS_05 = FROM "clk180_grp" TO "clk0_grp" TIG; TIMESPEC TS_06 = FROM "clk180_grp" TO "clk90_grp" TIG;

这些约束忽略 DCM/PLL/MMCM 所有输出时钟的跨域路径。

敬请参考 时序约束用户指南 (UG612) ;了解更多有关错误路径约束的详情: http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/ug612.pdf

解决方案 2

此外,您也可在 UCF 中为 DCM/PLL/MMCM 输出时钟手动添加不相关的 PERIOD 约束,而不是采用自动传递。只要不施加相关的 PERIOD 约束,工具就不会分析时钟跨域路径。查看以下范例。

自动传递:

net "clk_in" TNM_NET = clk_in_grp; TIMESPEC TS_clk_in = PERIOD "clk_in_grp" 10ns HIGH; TIMESPEC TS_clk0 = PERIOD "clk0" TS_clk_in HIGH; (Note 1) TIMESPEC TS_clk90 = PERIOD "clk90" TS_clk_in PHASE + 2.5 ns HIGH; (Note 1) TIMESPEC TS_clk180 = PERIOD "clk180" TS_clk_in PHASE + 5 ns HIGH; (note 1)

注 1:这些约束可自动传递到输出时钟。

手动添加不相关的 PERIOD 约束:

TIMESPEC TS_clk0 = PERIOD "clk0" 10 ns HIGH; TIMESPEC TS_clk90 = PERIOD "clk90" 10 ns HIGH; TIMESPEC TS_clk180 = PERIOD "clk180" 10 ns HIGH;

敬请参考 时序约束用户指南 (UG612) ;了解更多有关"related" PERIOD约束的详情: http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/ug612.pdf