如 AM003 中所述,“Calibrated Deskew”(校准去歪斜)功能特性用于最大程度减小全局时钟网络上的时钟偏差。

如果您当前使用“时钟校准去歪斜”,那么时序所含的偏差结果是不正确的。

解决方案:

Vivado 2021.1 和 2021.1.1 使用“时钟校准去歪斜”,因此您需要应用此处随附的补丁。

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性。

INFO: [Constraints 18-5720] The default GCLK Deskew mode is Calibrated.

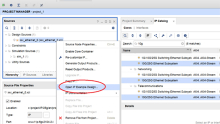

应用随附补丁后,需重新实现设计,您可检查 Vivado log 日志以验证是否已应用该补丁。

Vivado 2021.2.x 默认禁用该功能特性,因此不受影响。

| Vivado 版本 | 时钟校准去歪斜默认设置 |

| 2020.3 及先前版本 | 关闭 |

| 2021.1 和 2021.1.1 | 开启 *需补丁 |

| 2021.2 和 2021.2.1 | 关闭 |

| 2022.1 | 根据指定的器件和速度文件(请参阅下表),无需安装补丁(请参阅 Vivado 2022.1 - Versal 时钟校准去歪斜的时序问题) |

| 2022.2 | 根据指定的器件和速度文件(请参阅下表),无需安装补丁(请参阅 000034546 - Vivado 2022.2 - Versal 时钟校准去歪斜的时序问题) |

| 2022.2.2 | 根据指定的器件和速度文件(请参阅下表),无需安装补丁(请参阅 Vivado 2022.2.2 - Versal 时钟校准去歪斜的时序问题) |

注释:本答复记录随附的策略补丁还提供了适用于下列问题的补丁。此处提供了单个通用补丁以便于您使用。

Vivado 2021.1.x 和更低版本中的“时钟管理器”上的“去歪斜检相器”(即,使用 CLKIN_DESKEW 和 CLKFB_DESKEW 管脚)可能导致 Vivado 时序报告中出现错误的时序。

[1] 由于 CPM4 会将 DPLL 与去歪斜检相器搭配使用,因此会受此问题影响,请参阅 76947 - 适用于 PCI Express 的 Versal ACAP CPM 模式 (Vivado 2021.1) - 启用 CPM4 到 PL 接口的设计中可能存在时序问题

[2] 如果 MMCM 使用 CLKIN_DESKEW 管脚或 CLKFB_DESKEW 管脚,则可能会受此问题影响,请参阅 76908 - Vivado 2021.1 Vivado Versal 时钟设置:MMCM 和 DPLL 的去歪斜逻辑时序错误