您是否担心 RTL 设计中的延迟?

您的设计是否有效并经过优化?

AMD Vitis HLS 可帮助您解决这些问题。

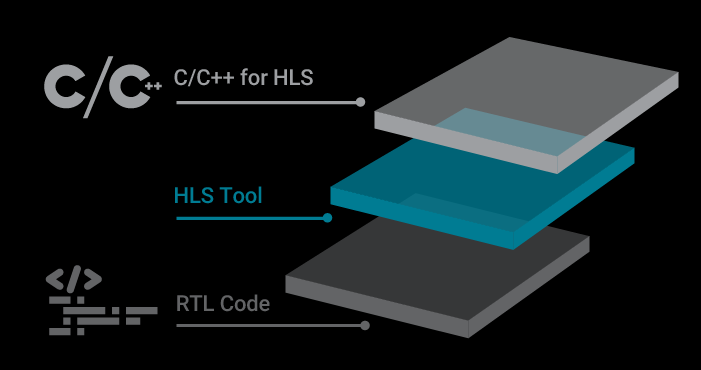

通过 Vitis HLS,您可将 C/C++ 函数综合到 RTL 中,从而轻松创建复杂设计算法。

AMD Vitis™ HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado™ Design Suite(用于综合、布置和布线)及 Vitis™ 统一软件平台(用于所有异构系统设计和应用)高度集成。

全新推出的Vitis HLS资源,具有以下特点:

点击下载和查看更多关于Vitis HLS的资源:https://china.xilinx.com/products/design-tools/vitis/vitis-hls.html