作者: Tulip Peng,来源:FPGA FAE技术分享选集微信公众号

AMD自适应计算加速平台(ACAP)是一个完全软件可编程资源集合,这些资源结合在一起构成片上系统 (SoC),包括以下主要的资源块:

Versal ACAP 应用可以利用这些资源中的功能。要创建设计或将设计移植到 Versal ACAP,必须确定哪些资源最能满足应用的不同需求,并跨资源对应用进行分区。下图显示了 Versal ACAP 的布局。

图1 Versal 器件布局

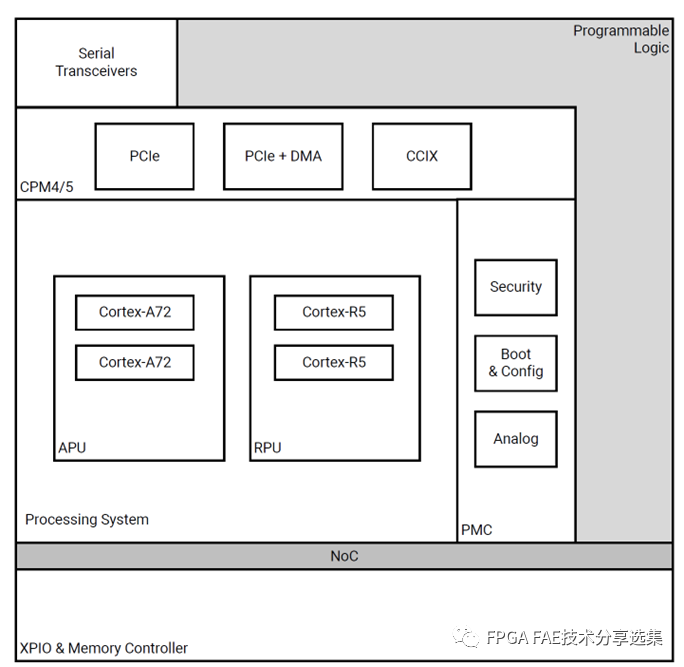

所有器件都包含一个由标量引擎(APU和RPU)和外设组成的处理系统(PS)。PS是包括平台管理在内的一组体系结构元素的一部分控制器、CPM块、NoC和集成内存控制器是紧耦合的,但也是能够彼此独立操作。简化的布局如下图所示。

图2 PS和周围的功能块

主要功能模块互连

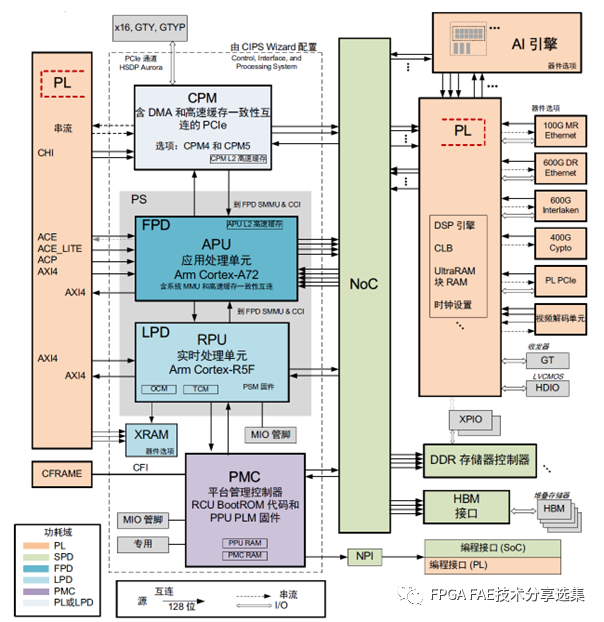

如下图所示,PS 模块、PMC 模块与 CPM 模块组合在一起,并使用 Control, Interface, and Processing System (CIPS) IP核进行配置。

图3 器件级互连架构

CIPS IP 核支持您完成以下配置:

1、配置 PMC、PS、NoC 和(可选)PL 的器件时钟设置

2、配置 PMC 闪存控制器、外设及其关联的多路复用 I/O (MIO)

3、配置 PS 外设及其关联的 I/O

4、配置 PS-PL 中断和交叉触发

5、配置 CPM(含 DMA 和高速缓存一致性互连的 Integrated Block for PCIe®)

6、配置连接至 NoC 和 PL 的 PS 和 CPM AXI 接口

7、配置系统监控器供电和温度监控和警报

8、配置 HSDP 用于高速调试

CIPS相关IP核定制和作用解析

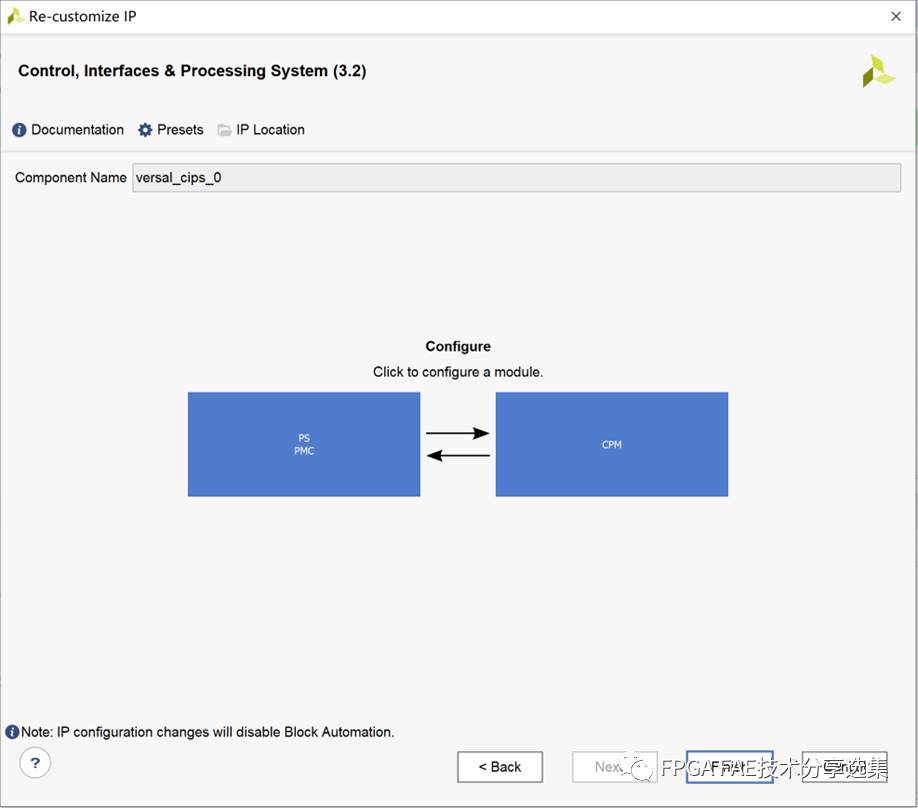

Versal ACAP 支持 2 种设计流程:传统设计流程和基于平台的设计流程。但所有 Versal 器件设计必须包含 CIPS IP。平台管理控制器 (PMC) 整合到 CIPS IP 中,必须对其加以配置才能使 Versal 器件正确启动。

1、CIPS IP核心模块设计

单击CIPS IP,可以自定义控制接口和处理系统IP核。选择定制的框图如下图所示。

图4 CIPS IP 核模块设计

a、选择设计流程

CIPS非常灵活,可以用几种不同的方式进行配置。CIPS IP允许配置许多操作参数。有两个设计流程可用于配置这些参数。这两个流程基于两个用户的传统典型应用,如下表所示。

CIPS IP为设计人员提供块/板卡自动化等辅助。块自动化提供初始配置并连接到其他相关IP块。当选择单板部件并设置预置时,Board Automation会对CIPS IP应用特定的配置预置,以配合目标板卡。此外,其他IP可以为连接到CIPS IP的附加外设/连接提供连接自动化。块自动化不可重入。除非将IP从IP集成器中删除并再次添加,否则它不能被再次调用。

b、块自动化

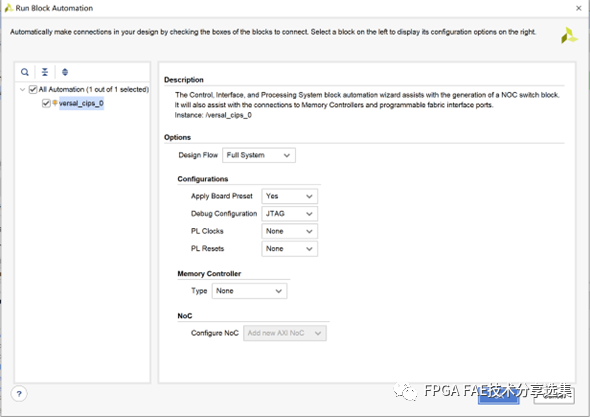

Vivado®支持CIPS IP的块自动化以帮助将其集成到更大的设计中。将CIPS IP添加到框图后将弹出块自动化横幅,如下图5所示。单击Run Block Automation打开块自动化页面。

有两种设计流程可供选择,选择的流程将反映在CIPS IP中。建议利用块自动化来配置DDR内存控制器,因为它可以确保CIPS和NoC IP的专用接口之间的适当连接。

图5 块自动化

图6 运行块自动化

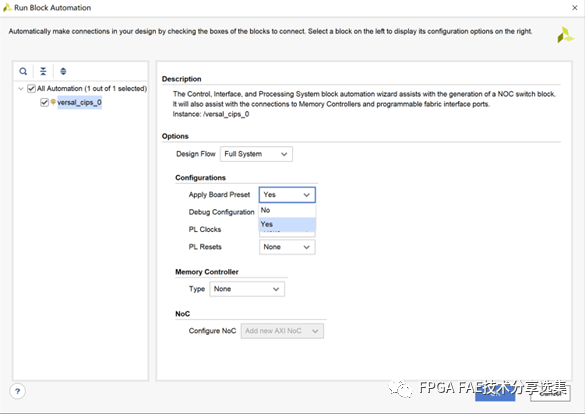

c、板卡自动化

创建针对单板而不是特定器件的Vivado®项目时,可以使用单板预设来初始化具有单板特定设置的CIPS IP核。在块设计中实例化CIPS IP后,将出现一个绿色横幅,要访问板自动化,请单击此横幅上的运行块自动化。

如果要设置单板预置,请在“运行块自动化”窗口中将“应用单板预置”设置为“是”。

图7 应用块自动化实现板自动化

d、CIPS预置

CIPS是通过CIPS参数的默认配置(称为Presets)启用的。预置方便设计创建和块自动化,并使用户能够通过GUI快速配置IP,而无需深入参数细节。根据所选择的设计流程,可以使用不同的预设。默认预设表示最简单和必要的设置选项。这些选项基于传统的、大多数遇到的用例,以及设备最小的启动和运行时需求。

有两个可用的设计流程,即PL子系统和整个系统。在选择设计流的基础上,将默认的预置配置启用到所选参数中。下图所示为CIPS IP核全系统与PL子系统预置。

图8 CIPS 预置

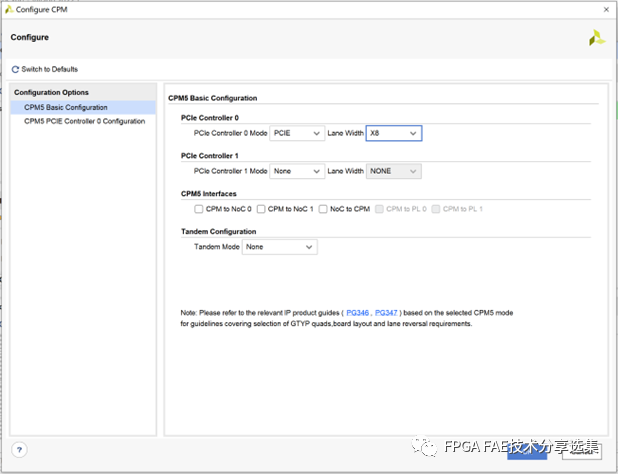

2、CPM模块

Versal 架构包括多个块,用于实现基于 PCITM-SIG 技术的高性能标准接口。在包含 CPM 的 Versal ACAP 中,CPM 遵循服务器系统方法论来为设计提供主要接口。作为 Versal 架构集成 shell 的一部分,CPM 与 NoC 之间存在专用连接,通过该连接可以访问 DDR 和其他硬化 IP。CPM 与可编程逻辑分开配置,使集成 shell 在启动后即可快速运行,而无需配置 PL。这种单独配置方法解决了 PCIe 规范带来的常见上电和复位时序问题。CPM 有 2 种实现方式:CPM4 和CPM5。

不同系列的 Versal 的器件可支持的 PCIE 最高速率不同,能够支持PCIE5.0协议的产品,例如 VPK120,其 CIPS 内使用的是CPM5,而只能支持到 PCIE 4.0 协议的产品,例如VCK190,其 CIPS 内使用的是 CPM4,某些器件不提供CPM。

目前,只有Full System (PS + PMC + CPM + PL)流程支持CPM块中的PCIe®配置。

图9 CPM4基本配置

图10 CPM5基本配置

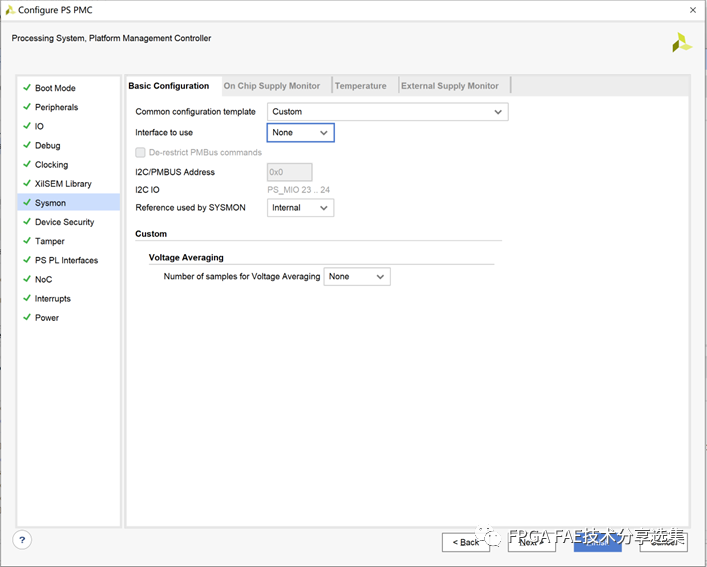

3、系统监控器

系统监测器(SYSMON)既可在Versal®ACAP本身内监测物理环境,也可在使用外部输入的更广泛的系统内监测物理环境。它是用来确保通用ACAP和整个系统以安全、稳妥、可靠的方式运行的。SYSMON为客户提供温度和应用电压供应的数字测量,以及在更广泛的系统范围内的片外电压测量。

它的主要用途是用于电源电压/电流的板电平监测。

CIPS IP核可以实现以下措施:

1、芯片供电监控

2、温度测量

3、外部供应测量

基本配置选项卡具有默认和自定义选项,如下图所示。

图11 SYSMON基本配置

默认窗口具有不同的预设选项,为SYSMON使用提供了一个典型用法。每个测量都有相关的阈值水平,控制报警断言。报警默认启用。对于对SYSMON测量的外部访问,支持I2C和PMBus接口。为确保不误触发SYSMON告警,请检查预置告警值,确保当前选择的值符合所需用例。

默认窗口还提供了设置电压平均水平为2、4、8和16的选项。MIO引脚分配可以通过IO面板进行修改。任何MIO冲突都以图标突出显示。

CIPS IP 核心允许最多选择 16 个引脚进行外部电源测量。所有 AUXIO 均应分配到同一Bank。AUXIO支持 PMC MIO、LPD MIO 和 HDIO。

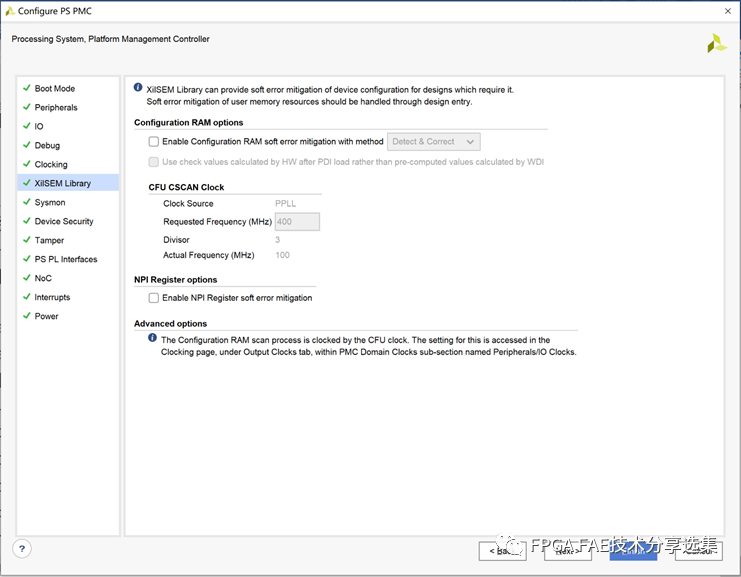

4、Xilinx Soft Error Mitigation (XilSEM)库配置

Xilinx Soft Error Mitigation (XilSEM)库提供了一种预配置和预验证的解决方案,用于检测并可选地纠正Versal ACAP配置存储器中的软错误。CIPS可以启用XilSEM库的基本功能。XilSEM库的高级功能可以通过应用于设计的属性进行访问。

图12 XilSEM库配置

5、篡改事件/响应配置

Tamper事件是来自篡改监测功能的中断。Tamper监测系统在检测到电源毛刺、温度偏差、调试(JTAG)切换检测、自定义用户(外部MIO)事件、Tamper寄存器事件和电压告警事件时,CIPS中产生中断,对上述每个篡改事件有不同的响应,用户可以为每个篡改事件选择不同的响应。

图13 Tamper事件/响应 配置

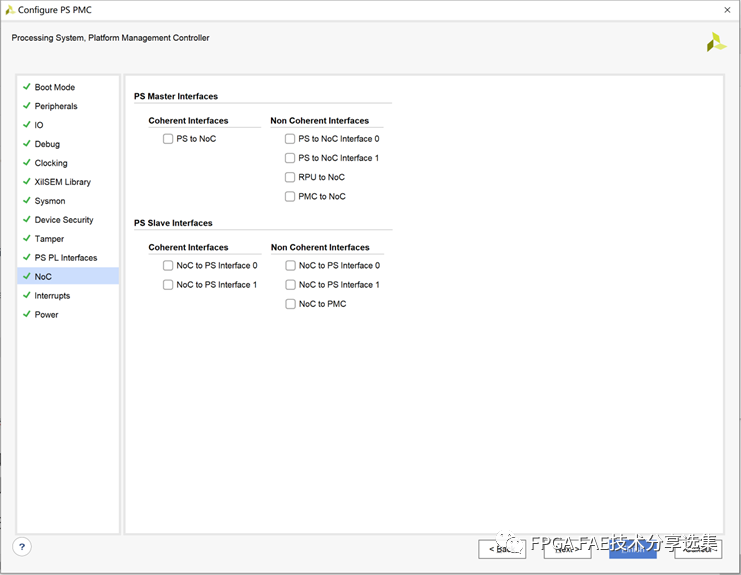

6、PS-NOC接口

PS-NoC接口选项支持从CIPS处理器到其他通用®设备资源(如DDR、AI引擎和PL)的内存映射连接。下表列出了可以在IP核配置中选择的NoC接口。

CIPS IP核PS-NoC接口显示了启用这些端口的不同NoC主/从端口选项,如图17所示。

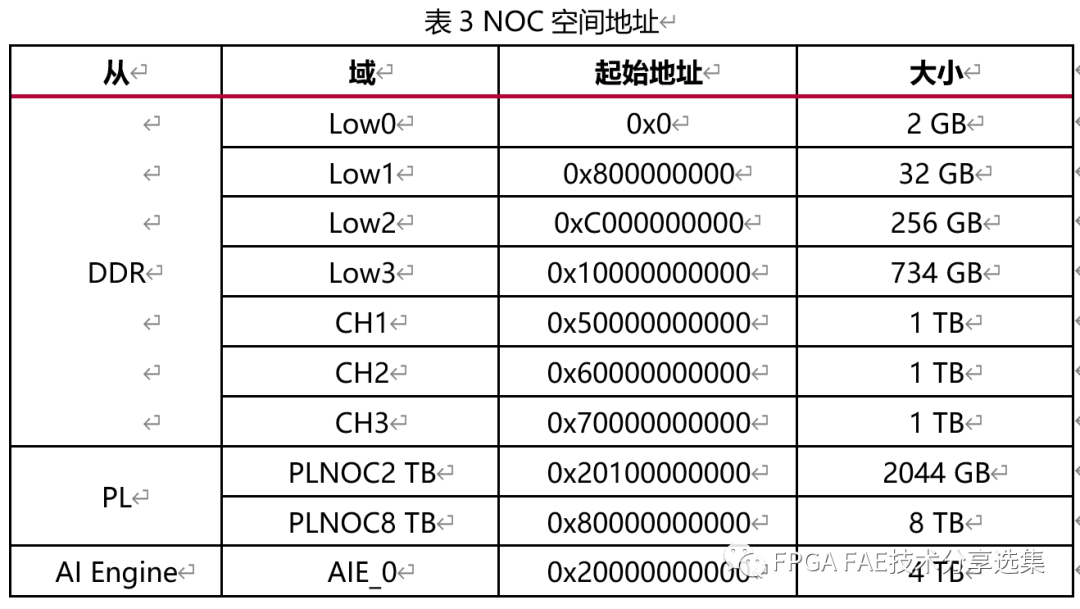

下表3显示了可以分配给连接到CIPS主NoC端口的DDR/AI Engine/PL从机的地址。

图14 PS-NoC接口

以下是关于PS-NoC端口使用的一些建议。

NoC上CIPS + DDR + PL从连接示意图如下图18所示:

图15 CIPS NOC

关于NOC可以同时参阅公众号里面“AMD Versal系列FPGA NoC介绍及实战”文章。

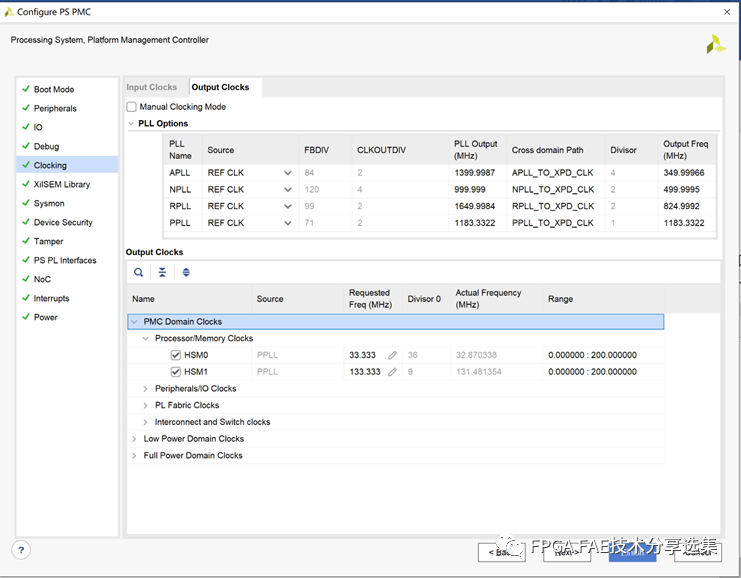

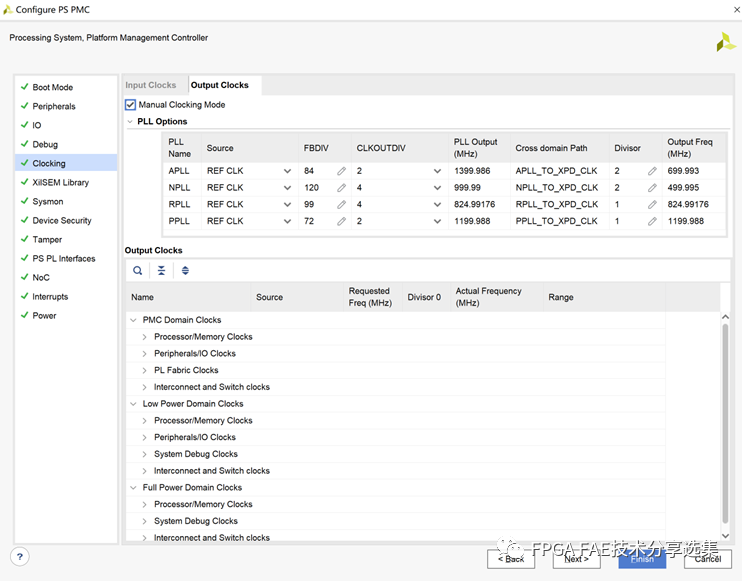

7、时钟配置

该界面可以用来配置外设时钟、PL时钟、DDR内存、AI引擎和CPU时钟。时钟组分为如下三种:

输入时钟:

图16 输入时钟配置

输出时钟显示允许更新频率的默认/用户选择的外围时钟,输出时钟保持不同的域锁相环。

PS和PMC中的PLL是:

•APLL:位于FPD领域的APU PLL

•NPLL:位于PMC域中的NoC PLL

•RPLL:位于LPD域的RPU PLL

•PPLL:位于PMC域中的PMC PLL

在默认模式下(当手动模式关闭时),核自动选择源锁相环并计算M(乘法器)和D(除数器)值,以确保工具满足请求的频率到最接近的可能值。因为每个PLL都满足多个外设的需求,核可能无法实现所有请求的值。如下图17所示。

启用手动时钟模式时,会显示不同的选项。用户可以直接输入各种锁相环的源锁相环,M和D值以及单个外围时钟除数值,从而实现更精细的控制。在手动时钟模式下,输入Ref时钟频率为33.33 MHz时给出默认除数值。如果您以不同的参考时钟频率移动到手动模式,那么您将遇到用户需要手动解析除数值的DRC。如下图18所示。

图17 输出时钟配置(默认模式)

图18 输出时钟配置(手动模式)

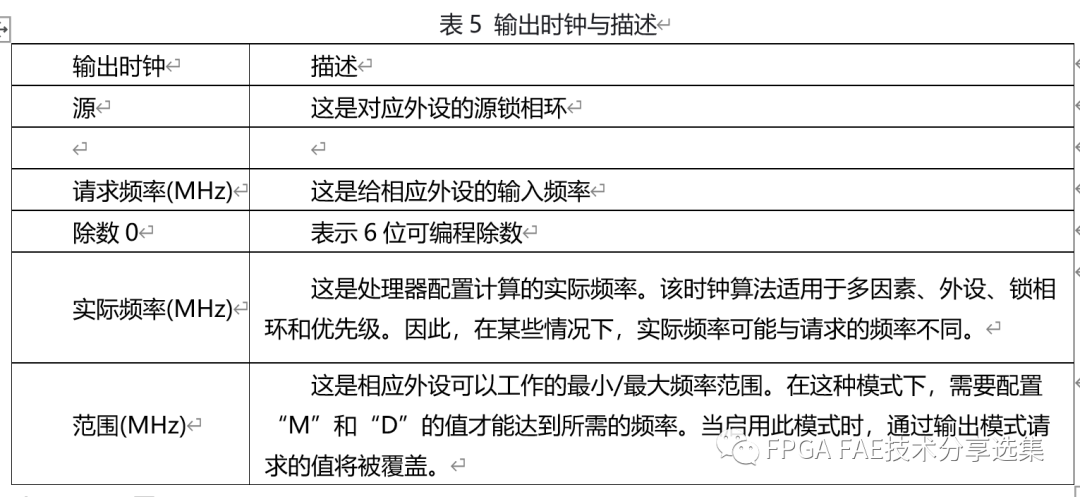

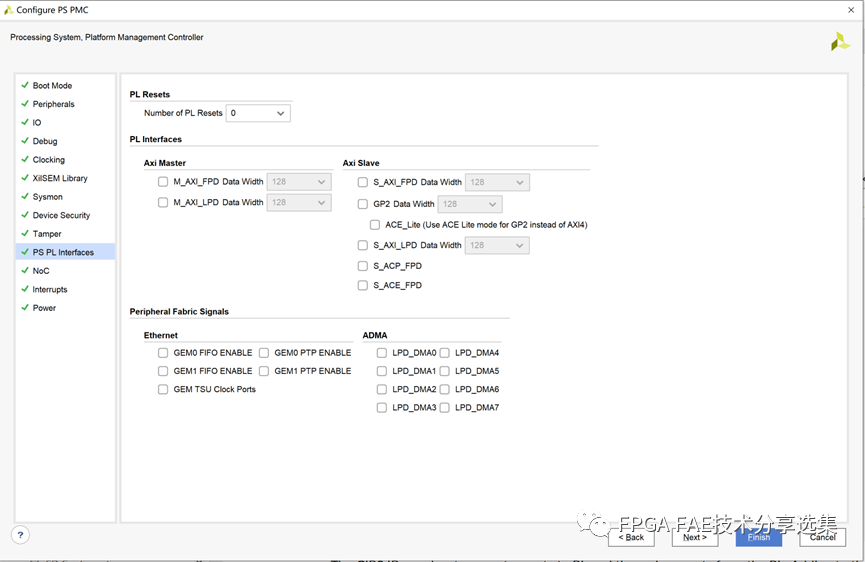

8、I/O配置

I/O Configuration页面反映了外设及其I/O连接性。您可以为信号分配属性。I/O外设分为PMC和PS两个域,共有78个MIO, PMC区域有52个(PMC MIO Bank0和PMC MIO Bank1), PS区域有26个(LPD MIO Bank)。每个IO可以根据规则分配给任何外设。

或者,来自每个外设的相同引脚可以路由到EMIO信号,这将信号带到设备的PL部分进行进一步处理。可用于外围引脚的MIO分为三个Bank: PMC MIO Bank0 (MIO 0-25), PMC MIO Bank1 (MIO 26-51)和LPD MIO Bank (MIO 52-77)。每个Bank的所有IO都有一个通用的I/O电压标准,默认值是LVCMOS1.8,还有LVCMOS2.5和LVCMOS3.3两个I/O电压标准选项。

您可以选择外设,GPIO和核篡改信号,以利用MIO。如果多个外设之间发生任何MIO冲突,将显示DRC消息以发出警报。每个外设都有不同的支持MIO集,您可以在这些外设之间进行调配,以避免外设间MIO的DRC发生冲突。此外,每个外设都有EMIO选项,也可以选择这个选项来解决MIO冲突。

在I/O配置页面启用外设后,您将能够在时钟配置中设置相应的外设频率。

对于每个MIO,都有一组引脚属性,用户可以通过单击各自的MIO在核心中设置这些属性。

图19 I/O配置

a、MIO IO接口

MIO保留功能允许您选择未使用/未分配的MIO作为GPIO/AUX- IO。要选择这些,您需要单击工具栏上的MIO PIN view按钮,然后在被认可的MIO的外部使用列中选择GPIO/AUX-IO选项。如果有任何MIO被分配给外设,那么这个MIO不能被设置为GPIO/AUX-IO,所以它的外部用法下拉列表被禁用。

如果MIO使用率为GPIO,则可以将其输出数据设置为active-High或active-Low,方向设置为In或Out。在启动后,当设置为Out方向时,该值将在IO上驱动。只有MIO用做是AUX-IO,才能设置方向为In/Out。

图20 MIO I/O保留设置

在“IO配置”界面中还可以选择PMC域的64个GPIO-EMIO引脚,PS域的32个GPIO-EMIO引脚。启用后,这些引脚将暴露到PL区域。

在通用®设计工具中,CIPS IP核用于配置核多用途IO (MIO)端口。CIPS IP核有多达78个MIO端口可用。该核允许您选择连接到MIO端口的不同外设端口。

b、EMIO接口

由于最多只有78个MIO端口可用,因此许多超出这些端口的外设I/O端口仍然可以通过扩展MIO (EMIO)接口路由到可编程逻辑。

通过可编程逻辑的IOP接口的替代路由使您能够充分利用CIPS IP核中可用的IOP。通用CIPS IP核允许您选择多达96个GPIO信号。通用CIPS IP核具有控制逻辑,可以调整流入CIPS IP核的用户选择宽度。用于I2C、SPI闪存、千兆以太网管理数据输入/输出(MDIO)、SD/eMMC、GPIO 3状态使能的EMIO信号在通用CIPS IP核中会反转。

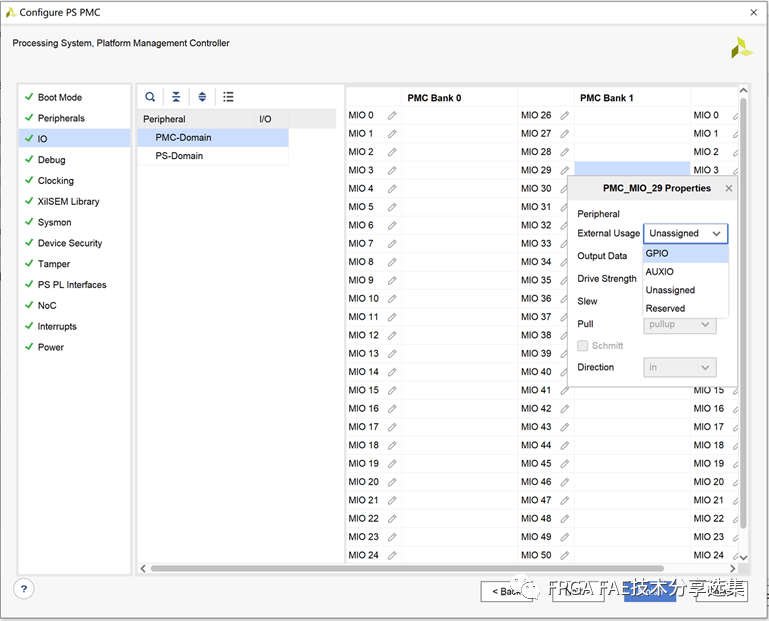

9、PL-PS配置

PL-PS配置页面控制哪些接口暴露给PL。图24PL- PS接口说明了控制,接口和处理系统IP核中的PL-PS接口,其中有两个GP主端口到PL和三个GP从端口来自PL。此外,还有一个ACE和一个ACP端口来自PL。所有这些端口的最大数据宽度为128位。

图21 PL-PS接口

10、PL中断

控制接口和处理系统IP核提供3个PS到PL中断接口(依次为每个外设提供大量共享中断)和16个PL到PS中断。此外,CIPS IP核有一个处理器和调试中断列表。“Interrupt Configuration”工具签用于启用/禁用CIPS核心与PL之间的中断。

图22 中断配置

11、电气特性配置

此页面允许您为Bank选择LVCMOS。对于所有相应的IO,每个Bank都有一个通用的I/O电压标准。默认值是LVCMOS1.8,还有两个选项LVCMOS2.5和LVCMOS3.3 I/O电压标准。

此设置必须反映每个MIO Bank使用的板LVCMOS电压。这些设置不用于设置任何寄存器或MIO电压。Vivado report_power使用它们来估计功耗。

图23 MIO电压标准

12、Debug设置

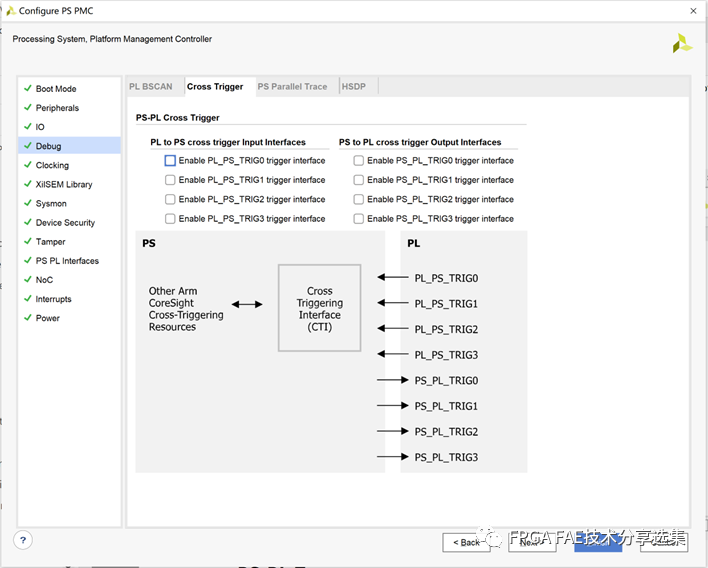

a、PS-PL交叉触发

PL到PS的交叉触发器输入是来自PL的触发器输入。您可以启用这些端口以从硬件获取触发器事件并将其提供给ILA以分析/调试硬件状态。

PS到PL交叉触发输出可用于设置软件中的调试断点以停止硬件。一旦给硬件触发事件,软件就会访问硬件状态进行调试。

图24 PS-PL交叉触发器配置

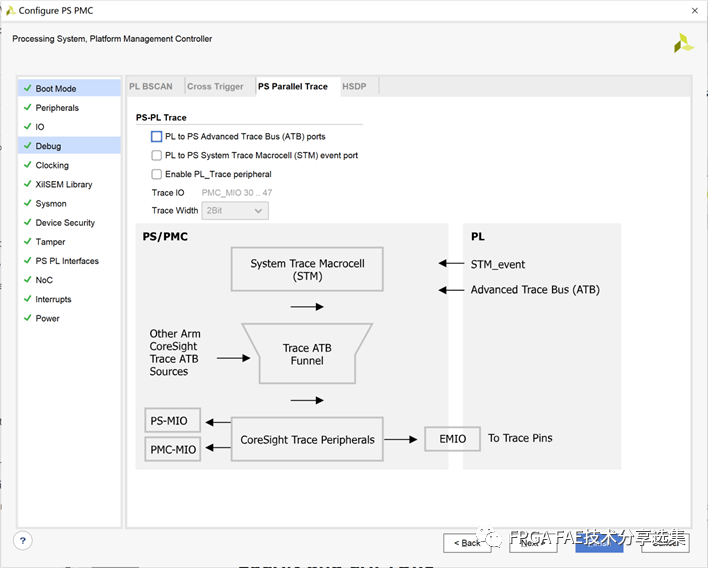

b、PS-PL跟踪

启用PL到PS高级跟踪总线(ATB)端口将启用CIPS IP上的ATB端口,允许PL访问高级跟踪总线。

PL 到 PS 的System Trace Macrocell (STM)事件端口将使能CIPS IP上的STM端口,允许PL访问CoreSight System Trace Macrocell。

片外并行跟踪允许通过MIO或EMIO从PS输出跟踪数据到PL。启用PL_Trace外围设备允许从IO面板视图中选择MIO或EMIO。

对于通过EMIO进行跟踪,可以使用PL IP连接到PS-PL跟踪接口,并根据Arm跟踪标准向PL XIO输出跟踪数据。PL XIOs通常连接到Mictor连接器,其中跟踪探针可以收集跟踪数据,以便在调试IDE中进行分析。

图25 PS-PL跟踪配置

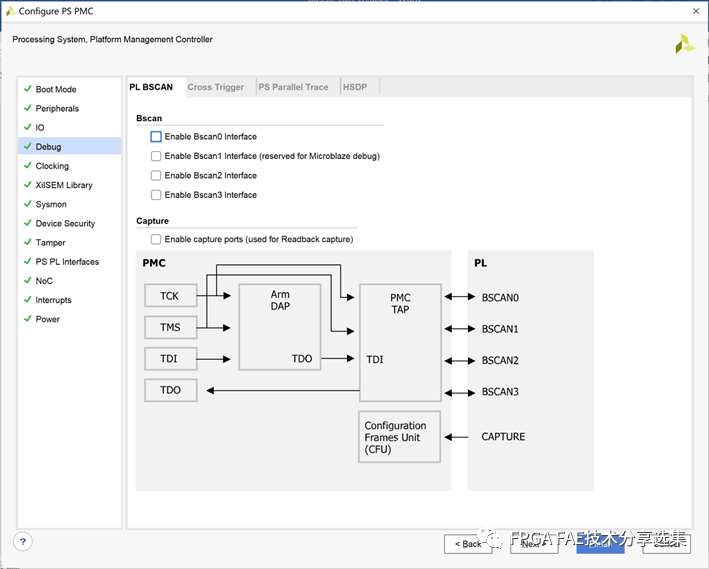

c、BSCAN和CAPTURE

有四个BSCAN接口可用于连接任何支持BSCAN的PL调试模块。BSCAN接口连接到PMC测试接入点(TAP)控制器,用于调试/边界扫描目的。CAPTURE端口提供用户控制和同步,控制何时以及如何请求捕获寄存器信息任务。只有寄存器触发器和锁存状态可以被捕获。

图26 BSCAN和CAPTURE Configuration

d、高速调试端口(HSDP)

高速调试端口是为可编程逻辑(PL)、处理系统(PS)和AI引擎提供调试和跟踪的协议。HSDP可以在设备上使用千兆收发器,提供比JTAG接口更好的性能。

由于HSDP是一种协议,事务层由调试包控制器(DPC)处理,链路层可以是下面列出的四个接口之一:

•JTAG

•HSDP Aurora(硬化的Aurora IP)

•CPM PCIe控制器

•PL Aurora (Aurora软IP)

图27 高速调试端口

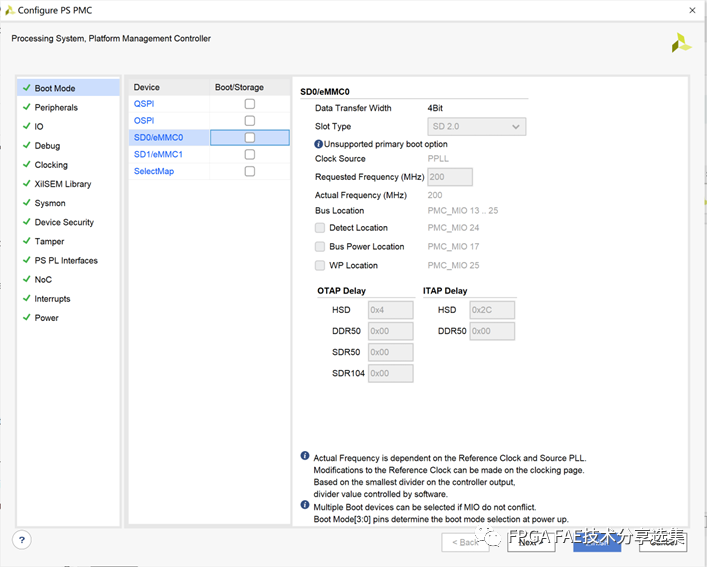

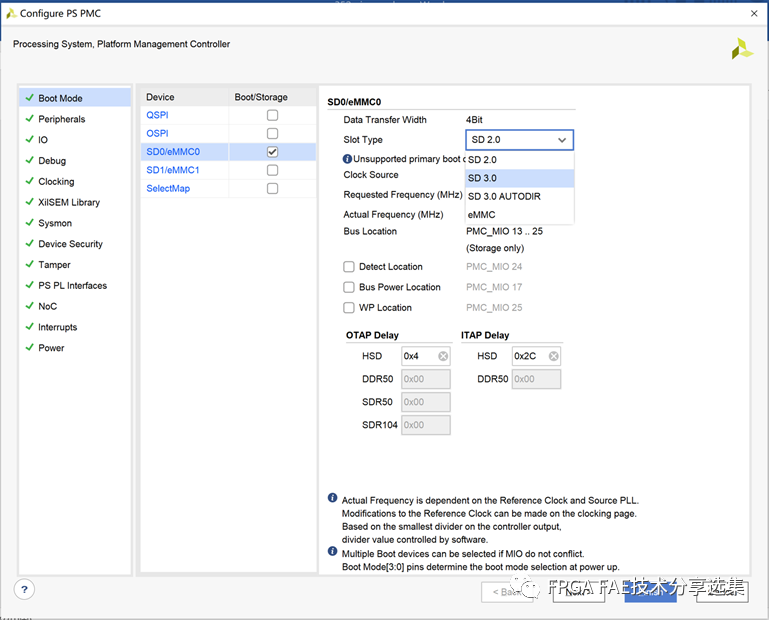

13、启动模式

Versal®设备启动方式与传统FPGA不同。不再有独立的比特流,而是在通用设备中有一个可编程设备映像(PDI),其中包括一个PL配置帧数据。CFI (Configuration Frame Interface)是通过配置帧数据来配置配置帧的接口。CFI属于PMC,PMC BootROM负责通过选定的引导介质从PDI读取PLM。

PLM包括启动设备配置。在“启动方式”页面中选择启动方式。根据单板支持的启动方式,可以选择多种启动方式。时钟设置,如启动外设所需频率和REF_CLK频率可在此页面设置。如果您只想使用PL部分,则应该使用此页面来配置启动外设。

QSPI、OSPI、SD0、SD1、eMMC1和SelectMAP都是主要的启动外设选项。如果选择的MIO不支持主启动,则SD0、SD1和eMMC1设置提供标志。

在Vivado GUI为SD0/1中显示一条关于使用存储或启动(和/或)存储的信息消息。

STARTUP选项可用于将设备引脚和逻辑接口到全局异步设置/复位信号,全局3态专用路由和启动结束(EOS)。

在Tcl命令提示符中支持的STARTUP选项,您可以设置CONFIG.PS_PMC_CONFIG设置为1,以获取CIPS上的基本端口。

图28 启动模式配置

在配置SD 0/eMMC0或SD 1/eMMC1控制器时,有多个选项可用。

图29 SD /eMMC配置

本期文章对CIPS主要功能模块做了解析,下一期会发布建立示例工程流程,敬请期待!

如果您对此文章内容感兴趣,欢迎联系:

simonyang@comtech.cn

charlesxu@comtech.cn