Xilinx(AMD) vivado软件IP核及license许可文件简介

yangyf000 在 周四, 01/18/2024 - 09:32 提交

Vivado软件作为Xilinx FPGA器件重要的开发设计软件

Vivado软件作为Xilinx FPGA器件重要的开发设计软件

本文来进一步讲解如何来建立CIPS IP核示例工程。

本文对CIPS主要功能模块做解析

本文主要介绍FIFO的一些基础知识,帮助大家能够理解FIFO的基础概念

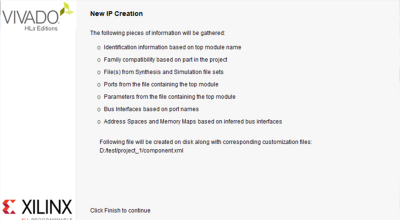

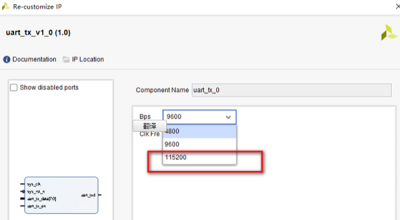

本文介绍了在Vivado中创建自定义IP核的步骤

本文将介绍Vivado中XCI与XCIX文件以及如何使用Core Container打包IP核

本文主要介绍了用户应当如何设置以太网IP的相关参数

本文向大家介绍一种更简单快捷的读写DDR数据方法

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核

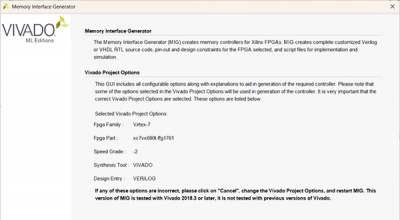

本文将向大家介绍Xilinx FPGA下的MIG IP核使用方法